1. RDC 解释

当前复杂设计除了包含多个时钟域外还包含了多个异步复位域。实际上,如果设计种存在跨异步复位域时同样会经常会遇到亚稳态的问题。 具体而言,对于有多个异步复位域的设计,如果某个异步复位在复位时,其复位的信号可能正好落在接受域时钟的建立和保持时间窗口内,这会造成接受端采样到发送端信号复位前后或复位后的值,从而造成仿真行为和真实行为的不一致。因此,需要不同异步复位域之间需要进行有效隔离或同步,或者提前指定异步复位的先后顺序,以确保设计可以可靠复位,避免由于跨异步复位域而引起的亚稳态问题。

1.1 跨异步复位分析

1.1.1 单时钟域中的跨异步复位

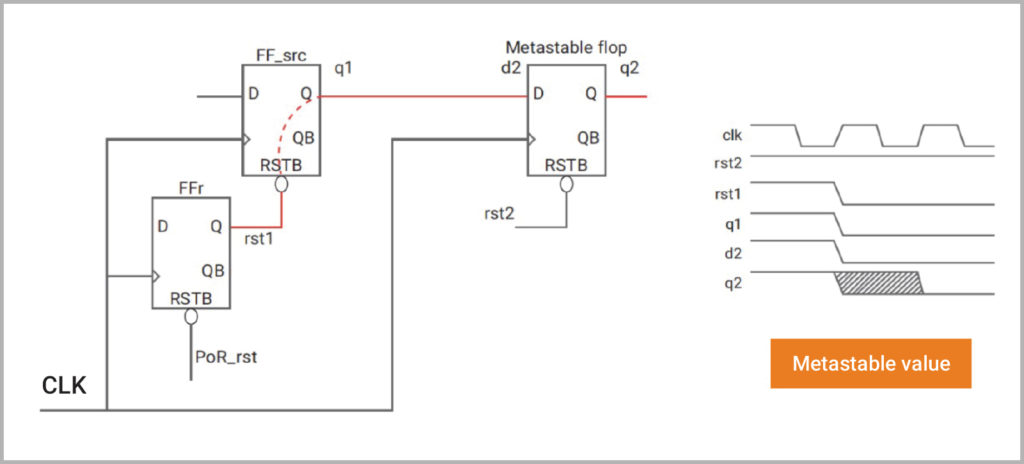

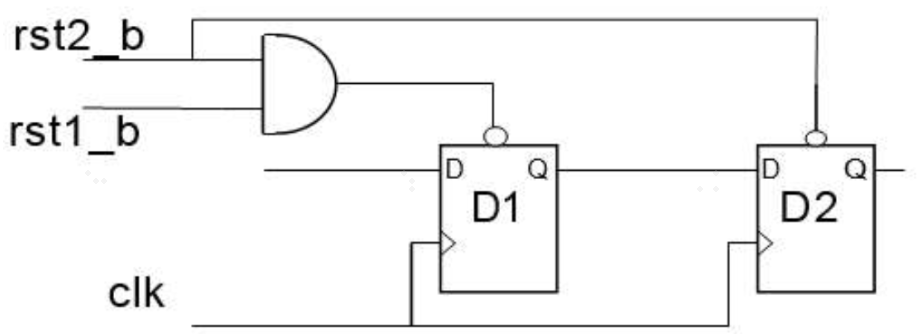

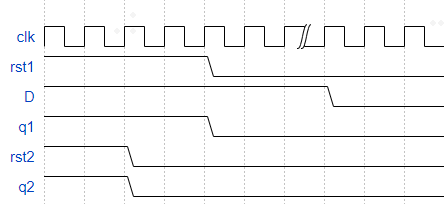

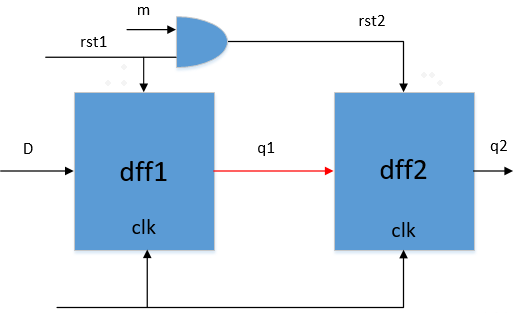

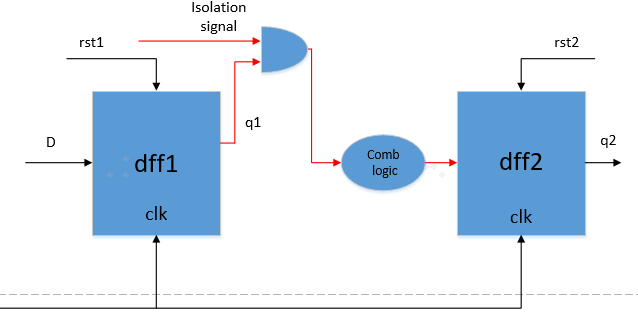

在芯片上,即使在单个时钟域内,源端触发器的异步复位端复位导致其输出跳变,该跳变传播到目的端触发器的数据输入端,就有可能会产生RDC,而RDC很容易导致亚稳态问题,当启动和捕获触发器的复位信号不同时,就会发生这种情况,称为复位域交叉(RDC)(如下图)。

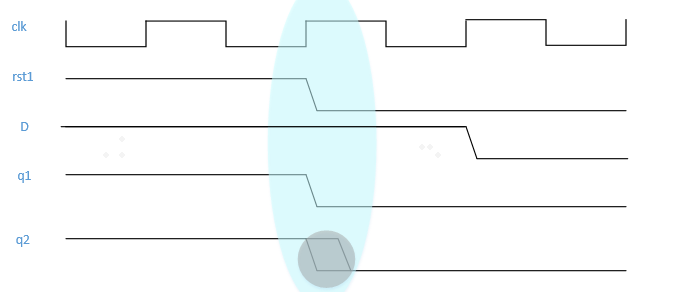

如上图所示,当信号从rst1复位域跨到rst2复位域时,如果rst1置低位复位的时刻恰好在时钟上升沿附近,那q2输出信号可能会出现亚稳态风险.因为异步复位信号rst1置低位的那个时刻,q1被立刻拉低,因为rst1在时钟上升沿附近被拉低,也就是说q1在时钟上升沿附近发生信号变化,对于dff2来说,可能会出现建立时间或者保持时间不满足导致q1信号不能被准确sample, 从而导致q2信号出现亚稳态。

FF2(dest)的rst2没有复位的时候,src的rst1不合适的复位触发时间,导致FF2(dest)的输入d2=q1不满足setup 和hold time,导致目的端触发器的数据输出端进入亚稳态。

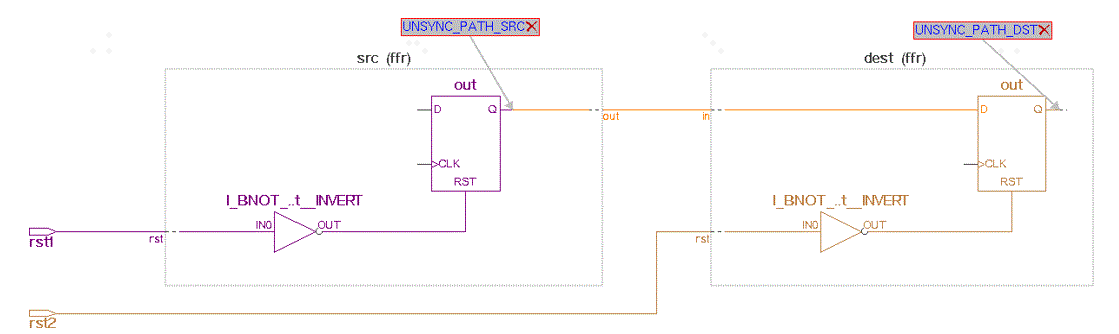

在上图中,当src的RST1解除复位时,q1上的解除复位值为相对于CLK时钟。因此,D2触发器上的输入值可以非常接近CLK时钟边缘。如果rst2上的值为“1”,DFF2处于活动状态,则可能导致输出D的亚稳态。

上面的电路中, 两个触发器都有不同的复位源,即rst1和rst2。rst1置为低电平(复位)而rst2保持高电平(不复位)可引起目的触发器的亚稳态,并且如果目的地触发器的输出向下行被进一步使用,那么可能会有一些功能故障。

1.1.2 无复位时序路径的跨异步复位域

目标触发器没有复位的情况和两个触发器的复位不同源的情况一样:当源触发器在不恰当的时间复位时,目标触发器的输入捕获到源触发器复位导致的源触发器的输处的数据变化,且该变化发生在目标触发器的时钟上升沿附近。目标触发器的输入可能会不满足建立时间或者保持时间要求,从而导致目标触发器的输出信号出现亚稳态。

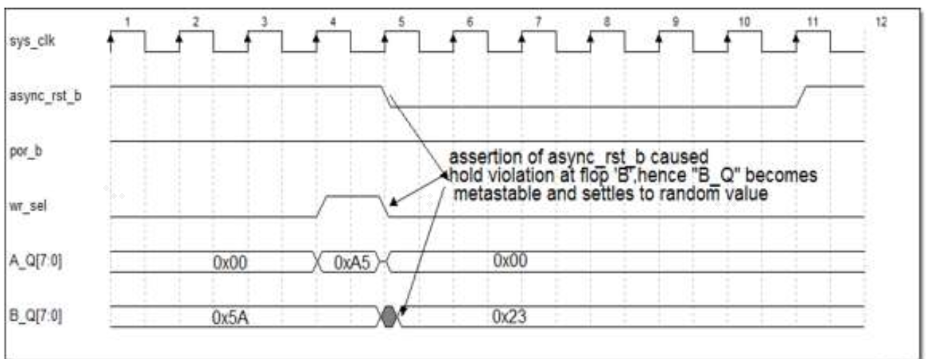

1.1.3 跨异步复位与门导致

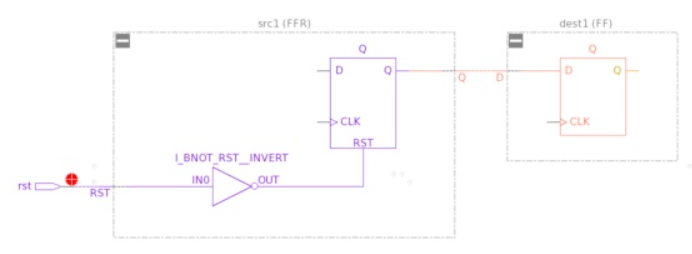

上图中我们有两个复位源rst1 和rst2。两者都“AND”连接到第一触发器D1的复位引脚,而第二触发器的复位仅连接到rst2。可以说源触发器的复位源实际上是目标触发器的复位源的超集。

因此,第二触发器的复位信号rst2_b由1变为0的低电平复位时,第一触发器一定复位,而第一触发器的复位信号rst1_b由1变为0的低电平复位时,第二触发器可能仍处于工作状态,因此可能会导致第二触发器进入亚稳态。

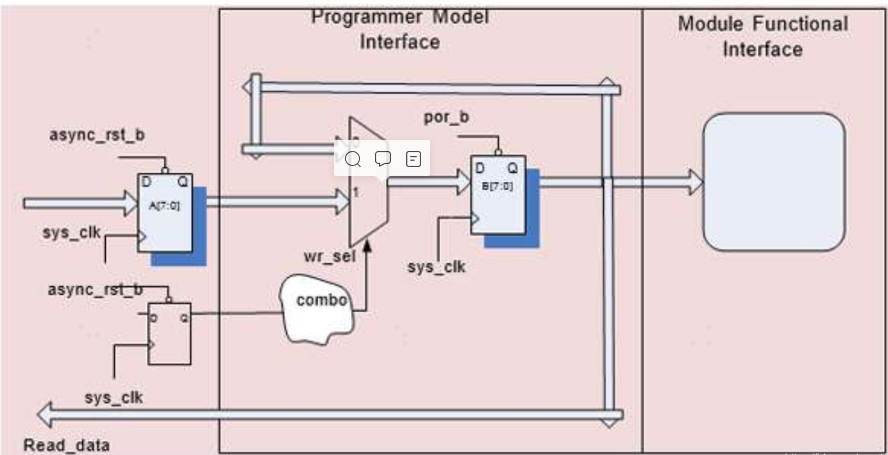

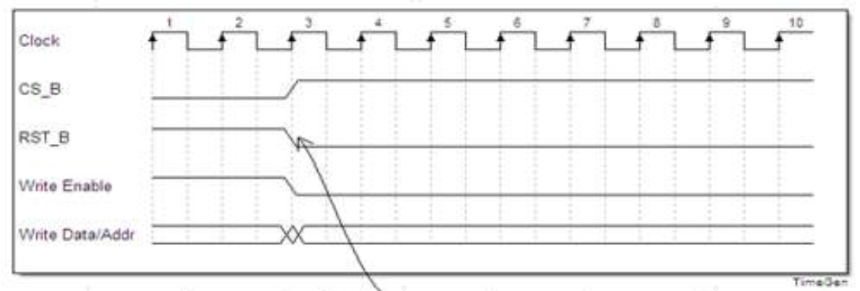

1.1.4 模块配置时的亚稳态

芯片中有些功能只能在POR期间复位,而在全局/热复位期间仍保持功能。因此,在全局复位期间,该功能的配置寄存器需要保持完整。但是,如果发生热复位,则在写入该特定寄存器时会破坏寄存器的内容,从而导致任何功能故障。下面的电路和波形图描述了这种情况。

在这种情况下,目标寄存器(B [7:0])是配置寄存器,只能通过POR复位。如果程序员正在写该寄存器,而源触发器突然复位,则目标触发器可能变得亚稳态,并可能稳定为未定义或不需要的值。

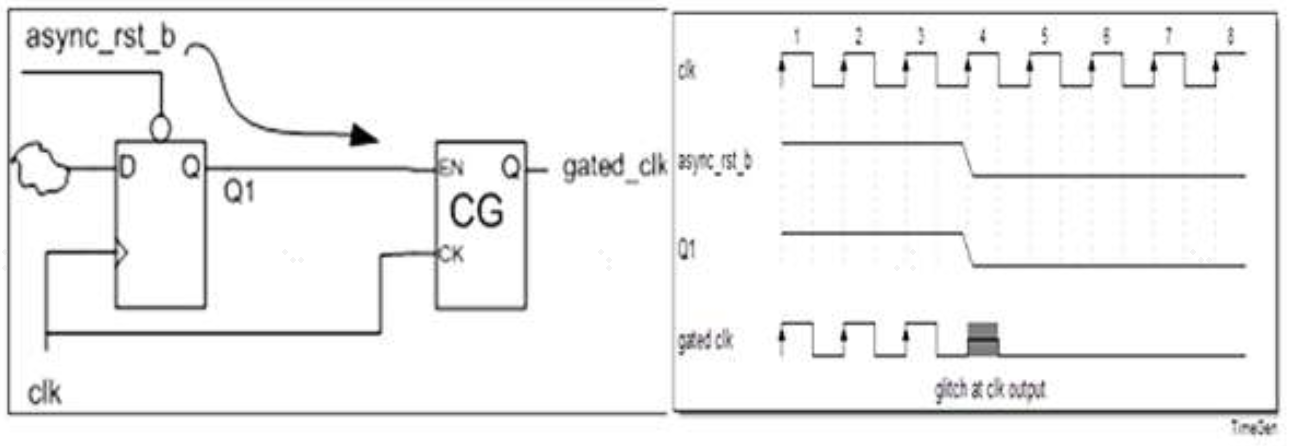

1.1.5 由于异步复位导致时钟故障

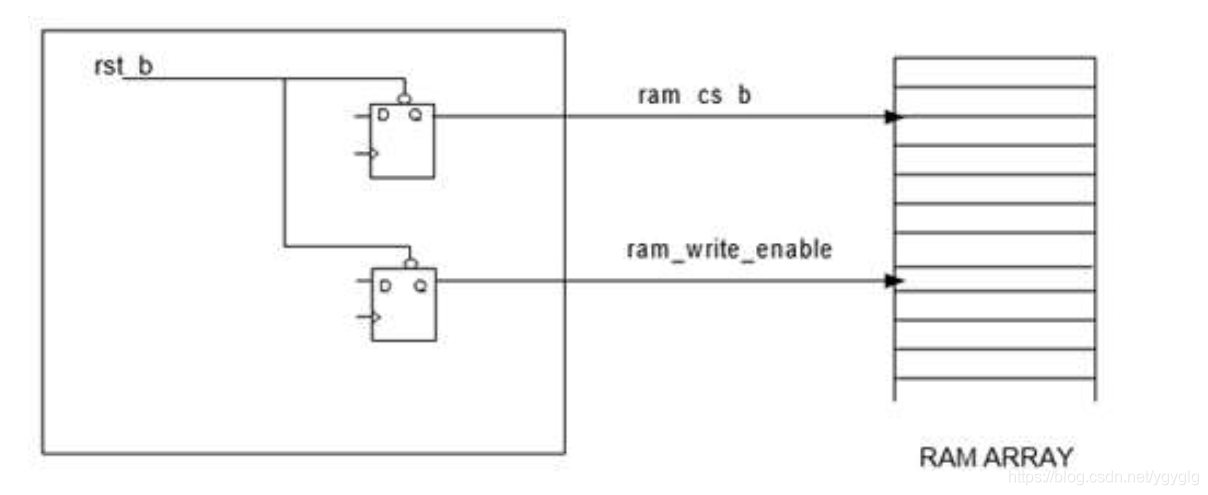

1.1.6 异步复位期间导致同步memory损坏

系统同步memory应在热复位期间保留其内容。但是由于复位域交叉问题,内存数据损坏的可能性很高。尽管在热复位过程中不会使存储器复位,但是控制存储器的存储器控制器逻辑可以异步进入复位状态。如下图所示,在此期间,如果使能了memory(使能了memory芯片选择并且正在进行某些memory写操作),则其同步接口将违反时序,并会损坏。

在时序图中,热复位(RST_B)在有效时钟沿附近断言,这将 异步更改存储器控制器输出chip_select,address,write_data,write_enable,从而导致存储器接口处的时序违规并导致数据损坏。

在memory写期间,由于时钟有效边沿附近的异步和异步复位断言,memory接口的控制和数据信号的立即变化所导致的亚稳态可能破坏memory的内容。

1.4 解决方案

1.4.1 解决方案1:reset assertion order

在图1和图2中,如果能保证,在rst1复位之前,rst2已经复位,或者说rst1复位的时候,rst2也一定在复位状态,这样可以保证q2信号不会出现亚稳态现象,这就是RDC中的reset assertion order, 这样可以过滤掉一些报告出来的RDC 路径,这些路径不存在亚稳态风险,这是从RDC分析的层面解决问题。

图4:没有问题的波形图

下面的图5电路就是一个典型的例子,rst1复位的时候,rst2一定在复位状态,这个电路就是安全的,q2不会出现亚稳态。

图5:安全的RDC

1.2.2 解决方案2:隔离法

(a)q1 数据隔离:如下图6,用一个isolation siganl 来隔离信号q1, 这个隔离信号可以是我们自己生成的一个控制信号,必须要保证隔离信号在rst1复位前就置位成低电平, 这样保证q1信号不会在时钟边沿附近发生电平变化, 就可以避免q2出现亚稳态。

图6 数据隔离方案

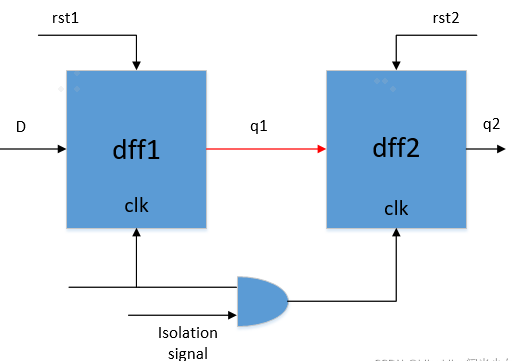

(b) 时钟clk隔离:如下图7,用一个isolation siganl 来隔离信号clk, 这个隔离信号也可以是我们自己生成的一个控制信号,必须要保证隔离信号在rst1复位前就置位成低电平,这样保证q1信号在时钟边沿附近的变化不会被sample, 因为clk已经被gate off了,就可以避免q2出现亚稳态。

图6:时钟隔离法

图7 时钟隔离方案

2. 模块间复位、解复位顺序

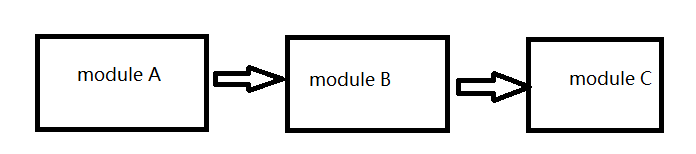

如图所示:模块A、B、C为芯片逻辑模块,数据流从模块A流向模块B、模块C。

1、复位顺序是怎样的?

如果需要对模块A、B、C进复位操作,复位操作顺序是什么样的呢?先复位哪个模块,后复位哪个模块?

复位顺序:C—>B—>A 按数据流的反方向复位

先复位C模块,最后复位A模块。复位的原则是保证复位完成后,数据通路中没有不稳定状态。

如果先复位模块A,最后复位模块C,则在模块A完成复位后的短暂时间内,模块A中之前的不稳定状态会依次传递到模块B和模块C,而B和C还处于非复位的工作状态,导致B和C接受到亚稳态的数据。

2、如果芯片上电完成后,模块A、B、C都处于复位状态,解复位的顺序是怎样的呢?

解复位:就是将复位信号置为无效状态,若上电后rst_n=0,解复位就是将rst_n=1。

解复位顺序:A—>B—>C 按数据流逆向解复位

先解复位模块A,最后解复位模块C,解复位后需要保证数据能够正常通路。

如果解复位顺序为C—>B—>A,在模块C解复位后,此时A和B仍处于复位状态,C暂时接收的数据是稳定的,但如果A和B在不恰当的时间解除复位,就会导致已经解复位的模块C采集到亚稳态的数据,使得电路进入错误的工作状态。

总得来说,后面的电路应该首先进行复位状态,或者最后进入解复位状态。

306

306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?