在电子设计领域,功耗优化是提升产品性能、降低成本和增强便携性的关键。

今天聊一聊Verilog设计中的功耗问题,提供具体的优化策略,并结合实例代码,指导如何在设计阶段有效降低FPGA的功耗。

一、功耗的多重影响

功耗是衡量电子产品能效的重要指标,它直接影响到设备的便携性、性能和成本。

低功耗设计不仅能够延长设备的使用时间,减少散热问题,还能降低生产成本,是现代数字设计的重要趋势。

二、功耗的分类与理解

在Verilog设计中,功耗主要分为动态功耗和静态功耗。

1、动态功耗

主要由CMOS电路中的充放电过程引起,包括开关功耗和短路功耗。

(1)开关功耗

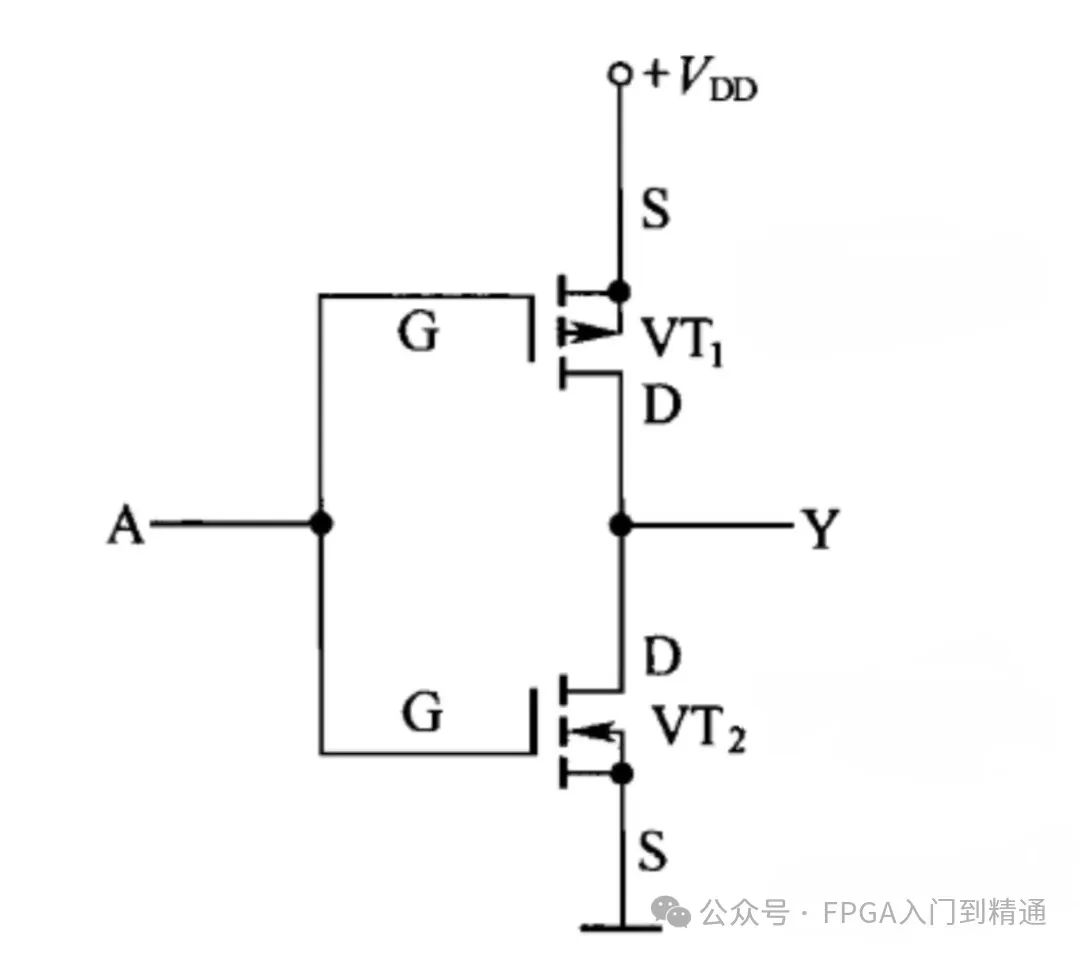

在CMOS电路中,每个逻辑门都可能带有负载电容(包括栅极电容、互连线电容等)。

当输入信号导致逻辑门输出发生翻转时(例如,从低电平变为高电平或反之),电源需要对负载电容进行充电或放电,从而在电容上存储或释放能量。

这个充放电过程就是开关功耗的来源。

开关功耗与负载电容、供电电压和输入信号的翻转率有关。

a、负载电容:负载电容越大,充放电过程需要的能量越多,功耗也就越大。

b、电源电压:电源电压越高,充放电的能量变化越大,功耗也越大。

c、翻转率:翻转率越高,单位时间内的充放电次数越多,功耗也就越大。

(2)短路功耗

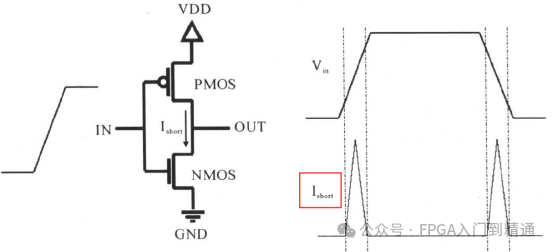

短路功耗则发生在输入信号翻转期间,PMOS和NMOS同时导通,形成短路电流。

在实际电路中,由于晶体管开关速度的非理想性,当输入信号在低电平和高电平之间变化时,会有一个短暂的时间段,使得PMOS和NMOS晶体管同时处于导通状态。

这时,电源和地之间形成了一个低阻通路,产生较大的短路电流,从而消耗能量,这就是短路功耗的来源。

2、静态功耗

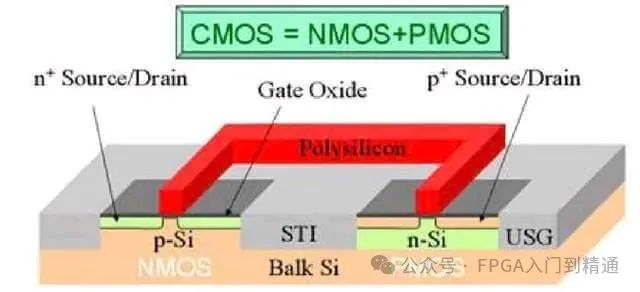

静态功耗,也称为待机功耗或漏电功耗,在CMOS集成电路中,即使在没有逻辑切换活动的情况下也会存在。

主要由CMOS电路中的漏电流引起,与工艺有关。

漏电流包括PN结反向电流、栅极漏电流和亚阈值漏电流等。

三、Verilog功耗优化策略

在Verilog设计中降低功耗的实用策略:

1、减少逻辑复杂度

简化设计逻辑,避免复杂的组合逻辑,减少不必要的触发器翻转。

2、优化时钟管理

使用门控时钟技术,只在需要时钟时激活相关逻辑,降低无效的时钟功耗。

3、状态机优化

使用格雷码作为状态机编码,减少状态转换时的触发器翻转数量。

4、数据表示优化

选择合适的数据表示方法,如独热编码,减少数据路径上的翻转。

四、实战代码示例

下面是一些Verilog代码示例,展示如何实现功耗优化:

示例1:门控时钟技术

// 定义一个模块,使用门控时钟减少功耗

module clock_gated_module(

input wire clk,

input wire clk_enable,

input wire reset,

output reg my_output

);

always @(posedge clk or posedge reset) begin

if (reset) begin

my_output <= 1'b0;

end else if (clk_enable) begin

my_output <= ~my_output; // 翻转输出

end

end

endmodule示例2:使用格雷码的状态机

// 使用格雷码的状态机减少状态转换时的功耗

module state_machine(

input wire clk,

input wire reset,

input [1:0] current_state, // 当前状态

output reg [1:0] next_state // 下一个状态

);

// 状态定义

localparam [1:0] S0 = 2'b00, S1 = 2'b01, S2 = 2'b11, S3 = 2'b10;

always @(posedge clk or posedge reset) begin

if (reset) begin

next_state <= S0;

end else case (current_state)

S0: next_state <= S1;

S1: next_state <= S2;

S2: next_state <= S3;

S3: next_state <= S0;

default: next_state <= S0;

endcase

end

endmodule五、总结

功耗优化是Verilog设计中不可忽视的一环。

通过本文提供的策略和示例,设计者可以在设计阶段就考虑到功耗问题,实现更高效、更环保的FPGA设计。

2330

2330

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?