根据在功耗分析的过程中是否有输入向量的提供,功耗估算方法可以分为仿真的方法(Simulative)和非仿真的方法(Non-simulative):

- 仿真的方法是根据用户所提供的大量输入向量来对电路进行模拟,利用功耗估算工具来估算具体功耗值。采用这种方法只需要仿真的时间足够长,功耗估算的精度就可以达到很高。但是由于受限于仿真时间和内存需求(对于大规模集成电路,不能在较短时间内得到一个精度较高的功耗估算值),只能适用于较小规模的集成电路。

- 非仿真的方法首先生成一些与电路相关的信息,这些信息可以是随机的,也可以是确定的,然后通过这些信息来计算电路的功耗,如信息论法、ATPG法、基于统计的方法等。非仿真的方法可以提高功耗估算的速度,但是功耗估算的准确度却没有仿真的方法高。

Synopsys公司的工具Power Compiler嵌入在Design Compiler之中,是一种可同时优化面积、功耗和时序的综合工具。它主要有以下两种功能:一是可以自动优化电路的功耗,使其最小化;二是在电路综合前预估功耗,使设计者可以更好地完成功耗分布的规划,在较短的时间内完成电路的低功耗设计。

用Power Compiler实现门级功耗估计的过程如下:

一 、获取SAIF(Switching Activity Interchange Format)文件;

使用工具Power Compiler进行功耗估算的时候会用到SAIF和VCD(Value Change Dump)这两种格式文件,它们都是用来记录设计中每个节点的翻转信息。SAIF文件只是保存了每个节点发生翻转的次数,而VCD文件详细地保存了每个节点发生翻转的时间。由于VCD格式文件记录了时间信息,所以它比SAIF格式文件大很多。

功耗估算的准确性主要取决于各节点的翻转信息是否可靠。使用工具Power Compiler估算功耗时通常会读入SAIF文件,以此获取各节点的翻转信息。在仿真工具中,设计者利用仿真程序或信号向量使设计中每个器件都发生跳变,把总跳变次数记录在SAIF文件中。SAIF格式文件可以通过以下两种方法产生:

1、通过仿真产生SAIF文件

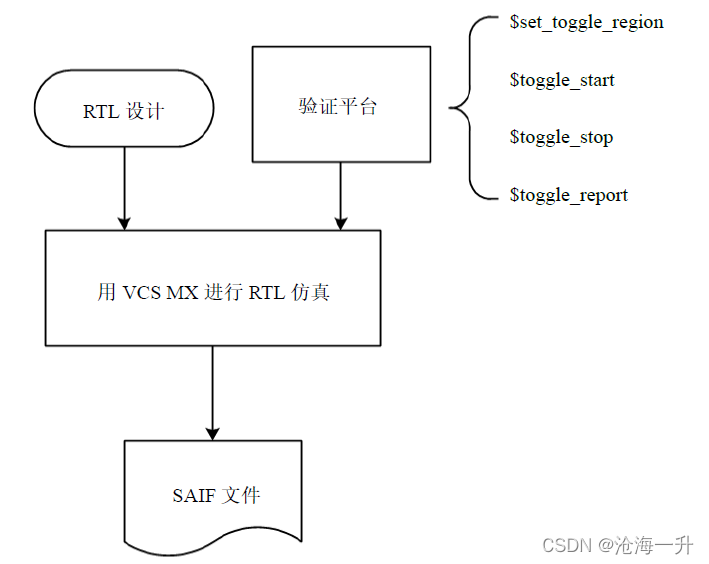

1)RTL仿真

如图所示为RTL仿真产生SAIF格式文件的流程图,只需在testbench里加$set_toggle_region, $toggle_start, $toggle_stop, $toggle_report这几个命令后再运行仿真程序即可。

一个简单的示例如下:

initial begin

$set_toggle_region(design_test.design_top);

$toggle_start();

….. //省略testbench中的测试语句

$toggle_stop();

$toggle_report("design.saif",1.0e-12,"design_test");

$finish;

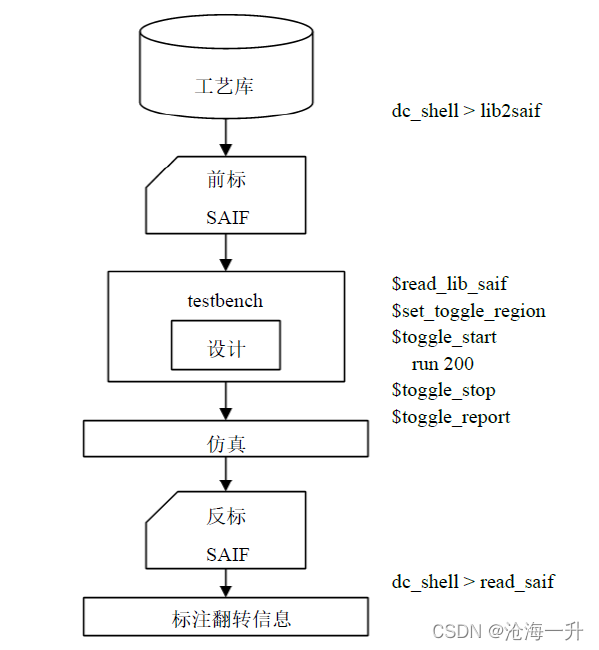

end2)门级仿真

下图为门级仿真产生SAIF格式文件的流程图。首先在Design Compiler里读入设计文件,通过命令lib2saif生成正向SAIF文件如forward.saif。然后通过VCS仿真生成反标的SAIF文件。在仿真之前,testbench里面除了需要加入RTL仿真生成SAIF格式文件时所需要的命令外,还必须在$set_toggle_region前加入命令$read_lib_saif(forward.saif)。

2、其他文件转换

1)用命令vcd2saif 把VCD格式文件转换成SAIF格式文件。

2)用命令fsdb2saif 把FSDB格式文件转换成SAIF格式文件。

二、Power Compiler读入SAIF格式文件进行功耗估计

生成了SAIF格式文件之后,就可以使用Power Compiler工具进行功耗估算了。具体步骤及主要脚本如下所示:

//=========在Design Compiler中读入设计文件=============

analyze -format verilog -library WORK /home/fxia/design/src/timescale.v

analyze -format verilog -library WORK /home/fxia/design/src/design_defines.v

…… //省略其他的设计文件

analyze -format verilog -library WORK /home/fxia/design/src/design_top.v

elaborate design_top -library WORK -architecture verilog

set current_design design_top

link

//=========定义时钟及各种约束=============

......

//=========读入前面产生的SAIF格式文件=============

read_saif -input design.saif -inst design_test/design_top

//=========生成设计的功耗报告=============

report_power -analysis_effort high -verbose > $report/design_add_sig.power_rpt

本文介绍了在集成电路设计过程中使用的两种功耗估算方法:仿真的方法和非仿真的方法,并重点讲解了如何使用Synopsys PowerCompiler工具进行门级功耗估计的具体步骤。

本文介绍了在集成电路设计过程中使用的两种功耗估算方法:仿真的方法和非仿真的方法,并重点讲解了如何使用Synopsys PowerCompiler工具进行门级功耗估计的具体步骤。

1240

1240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?