高速先生成员--周伟

我们经常遇到很多系统通过高速连接器相连,信号按照Pcie3或者Pcie4的协议来走线,往往很多连接器的阻抗通常是100ohm的标准,而Pcie3或者Pcie4按照协议或者芯片要求却是85ohm的标准,那么这个时候我们的线路阻抗到底是按照85还是100欧姆会比较好呢?

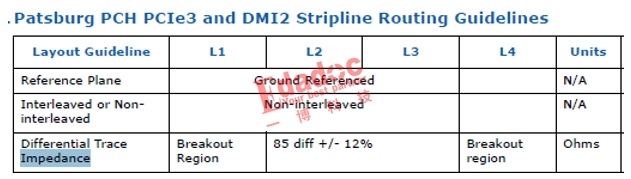

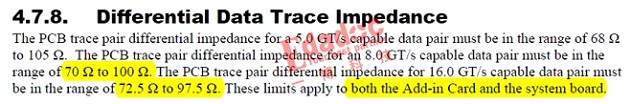

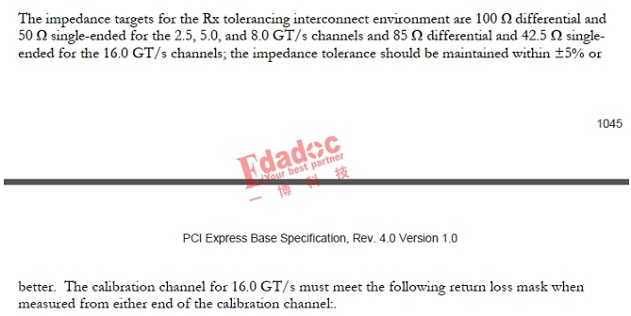

如下是关于线路阻抗的一些芯片要求或者协议要求。

总结起来就是Pcie3.0以下是100ohm,Pcie3或者以上就是85ohm的标准,速率越高,阻抗的公差要求就越严格。

现在我们的一个客户就遇到了一个上面的实际问题。客户的系统是由CPU板和FPGA板组成,其中CPU板上面有4个高速连接器分别与FPGA板上的一个连接器对接,中间的信号使用Pcie3.0协议,后面可能会升级支持到Pcie4.0协议,而中间的连接

本文探讨了PCIe 3.0及更高版本协议下,85欧姆与100欧姆阻抗控制的选择问题。在实际案例中,CPU板与FPGA板之间的高速连接遇到信号质量问题,通过分析阻抗测试结果,发现连接器阻抗偏高,与线路阻抗存在较大偏差,导致眼图不佳。问题集中在两个特定的连接器上,提示可能需要调整子板设计以匹配85欧姆阻抗标准。

本文探讨了PCIe 3.0及更高版本协议下,85欧姆与100欧姆阻抗控制的选择问题。在实际案例中,CPU板与FPGA板之间的高速连接遇到信号质量问题,通过分析阻抗测试结果,发现连接器阻抗偏高,与线路阻抗存在较大偏差,导致眼图不佳。问题集中在两个特定的连接器上,提示可能需要调整子板设计以匹配85欧姆阻抗标准。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2713

2713

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?