概述

本文记录一个简单的数字信号处理综合系统。在这个设计实例中,由DDS生成模拟中频信号与本振信号,使用DDC(Digital Down Converter,数字下变频)提取出同相分量i和正交分量q,计算两路信号之间的相位差,将测量结果通过串口发送至PC,使用Qt上位机做界面显示。

这是一些完成本文设计的参考文章:

1. DDS IP核的使用参考FPGA数字信号处理(一)数字混频(NCO与DDS的使用):

https://blog.csdn.net/fpgadesigner/article/details/80512067

2. 计算相位时arctan函数实现参考FPGA数字信号处理(十四)Vivado Cordic IP核计算arctan:

https://blog.csdn.net/FPGADesigner/article/details/80780088

3. Vivado FIR滤波器设计参考FPGA数字信号处理(五)Vivado FIR IP核实现:

https://blog.csdn.net/fpgadesigner/article/details/80621411

4. Qt上位机程序设计参考Qt程序设计(一):气象自动监测站-图形化搭建程序界面:

https://blog.csdn.net/fpgadesigner/article/details/74278934

Qt程序设计(二):气象自动监测站-串口通信与数据处理:

https://blog.csdn.net/fpgadesigner/article/details/74295083

环境与设备

Vivado 2017.2

Xilinx FPGA开发板

Qt 5.8(MSVC2015)

系统设计

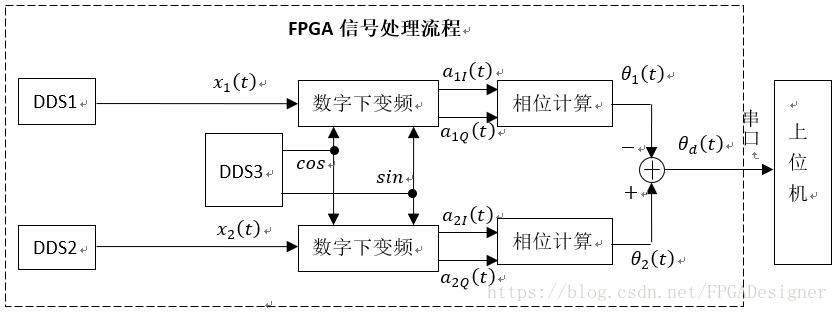

FPGA系统设计框图如下所示:

使用DDS Compile IP核生成两路余弦信号x1(t)和x2(t),这里设置采样率为100MHz,中频信号频率20MHz+500kHz。DDS1的相位固定为0°,DDS2的相位可以通过上位机调节。本系统的任务就是测量x1(t)与x2(t)之间的相位差。DDS3产生本振信号cos与-sin,频率为20MHz。

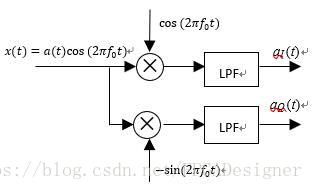

数字下变频模块(DDC)的原理框图如下所示:

与两路本振信号混频,经过LPF滤除高频分量,得到基带信号。滤波器的通带频率fp应大于基带信号的带宽(此处为500kHz),截止频率fc应小于载波信号频率(此处为20MHz)。经过LPF后得到相互正交的复基带信号的实部i和虚部q。

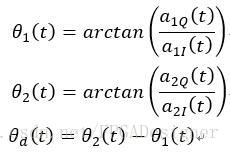

两路中频信号x1(t)和x2(t)分别通过数字下变频(DDC),可分别得到两路复基带信号的实部和虚部,设a1Q和a1I为第一路复基带信号虚部和实部,a2Q和a2I为第二路复基带信号虚部和实部,则两路复基带相位的相位估算θ1 (t)和θ2 (t)及两路信号之间的相位差θd (t)为:

需要注意的是,当信号经过LPF滤波后,提取出的基带信号带宽往往都远远低于系统的采样频率,可以抽取滤波来降低采样率。Vivado的FIR滤波器就提供抽取的功能,将“Filter Type”设置为Decimation。本设计LPF滤波后的信号只有500kHz(20.5MHz与20MHz信号混频后为差频500kHz与和频40.5MHz信号),抽取率Decimation Rate Value设置为10,输出数据速率为10MHz。

在FPGA中设计时,计算arctan函数的功能使用Vivado提供的CORDIC IP核实现,得到的数据范围为-π~π,不需要考虑象限模糊的问题(arctan函数的值域∈(-π/2,π/2),而相位的取值∈(-π,π),所以通常会有象限模糊的问题)。得到的两个信号相位相减则为相位差。

MATLAB仿真

按照设计要求,系统参数选择为(与FPGA保持一致):

●中频信号频率:用余弦信号模拟,频率为(20Mhz+500kHz);

●载波频率20MHz(本振);

●采样频率100Mhz;

●中频信号x1(t)固定相位0°,设置x2(t)相位。

设计包括:中频信号产生、本振信号产生、数字下变频(FDATOOL设计LPF并导出coe文件)、抽取滤波、象限模糊修复、相位差计算。

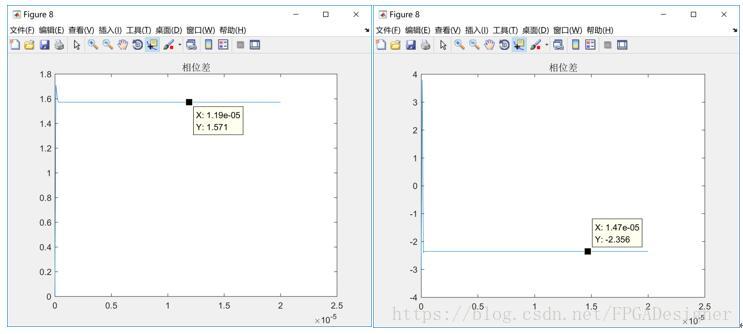

x2(t)相位设置为(0.5*pi=1.57),结果如下左图;x2(t)相位设置为(-0.75*pi=-2.35),结果如下右图。

FPGA设计

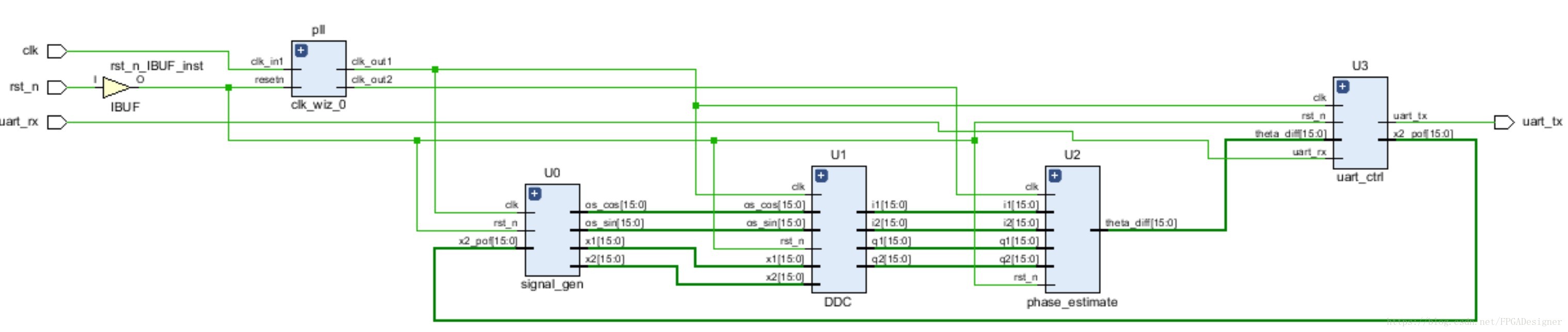

FPGA设计的RTL视图如下:

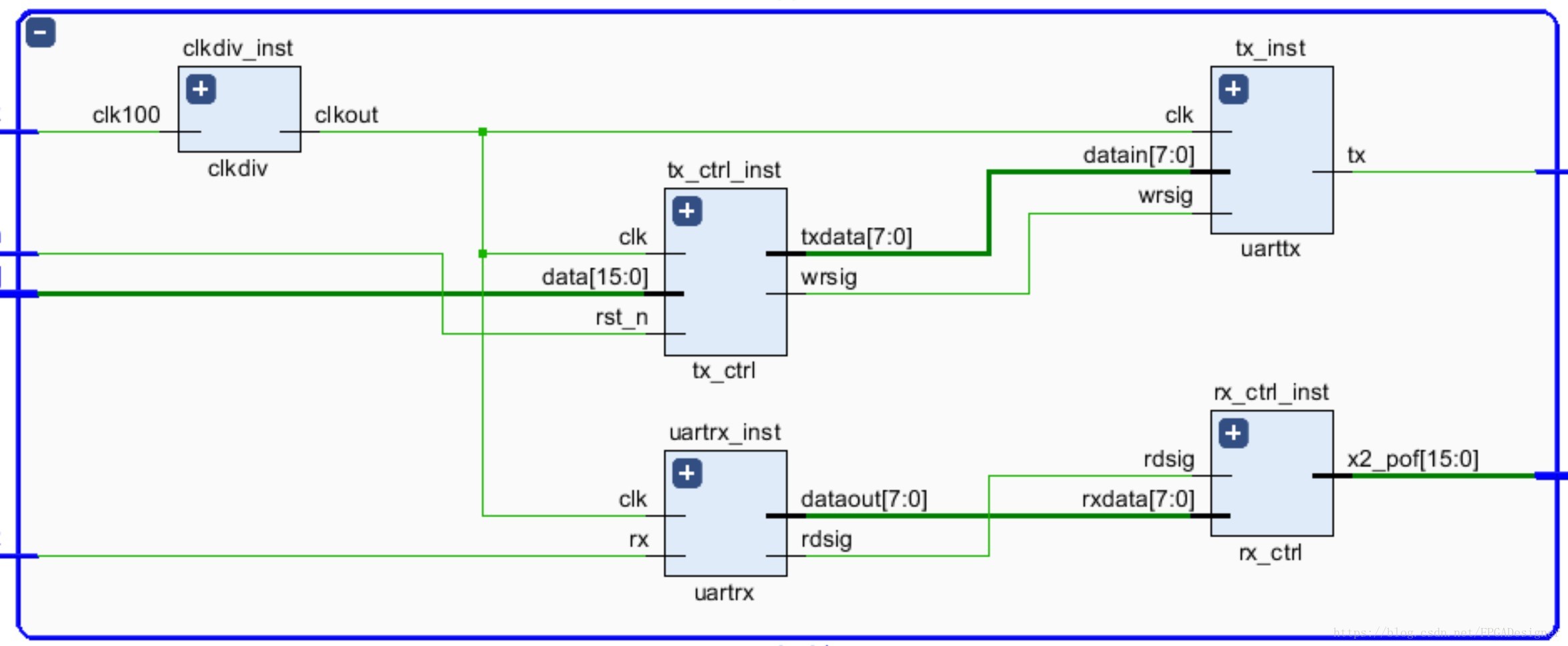

包括PLL模块(生成所需时钟信号)、信号生成模块signal_gen(产生中频信号与本振信号)、数字下变频模块DDC、相位估算模块phase_estimate和串口控制模块uart_ctrl。串口控制模块系统框图如下:

包括时钟分频模块clkdiv、串口发送模块uarttx、串口接收模块uart_rx、串口发送控制模块tx_ctrl和串口接收控制模块rx_ctrl。串口部分将需要发送的相位差数据按一定帧格式组织好发送;接收到的DDS2的初始相位也按预定的帧格式解析。串口数据刷新率设定为1秒。

值得注意的是,两路信号由于总存在一定的相位差,导致减法器输出的相位差结果不会限制在-pi~pi之间,必须做一定的修正以得到正确的结果(详情可参考下面的System Generator设计部分)。

仿真测试

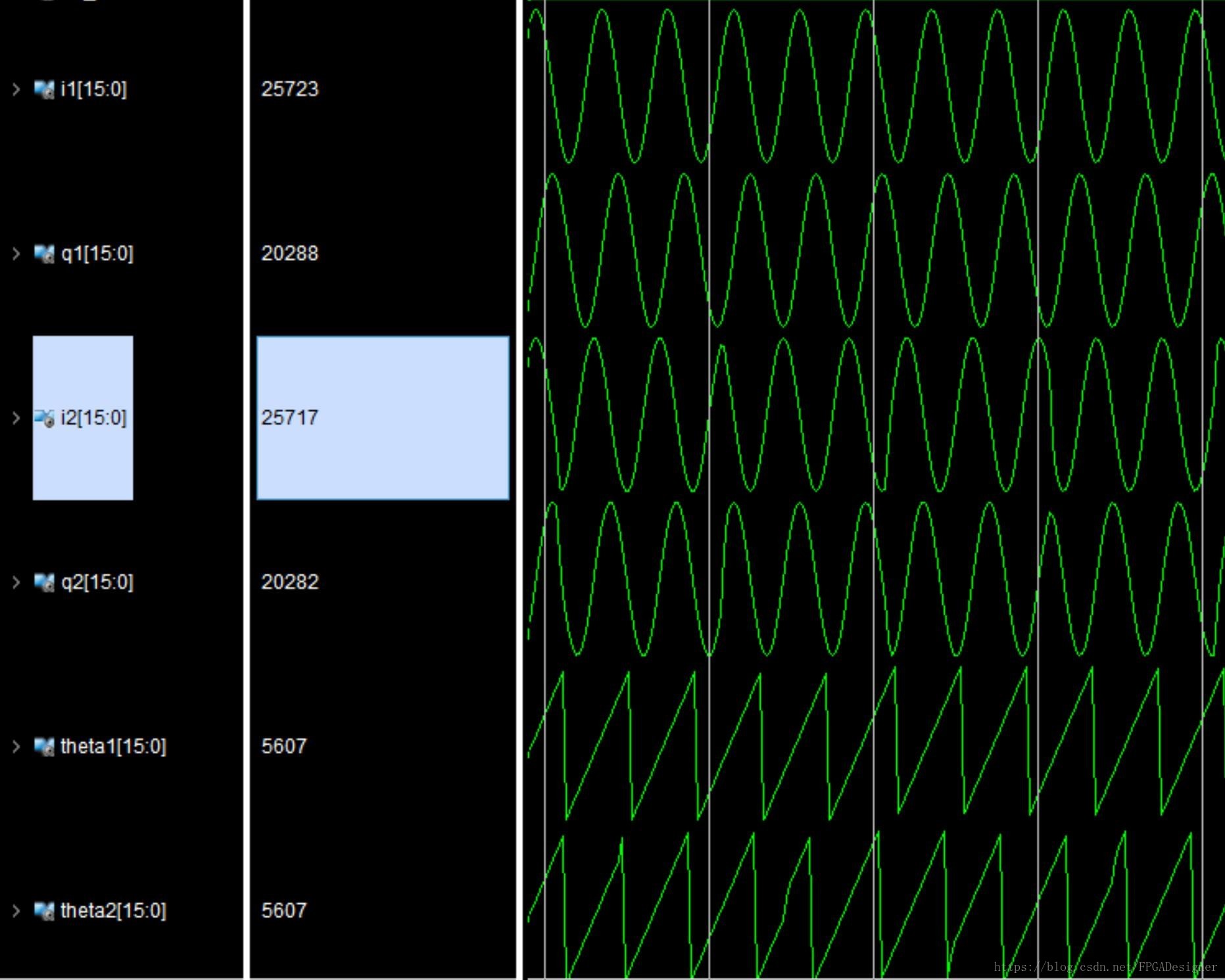

编写Testbench,在Vivado中进行仿真:

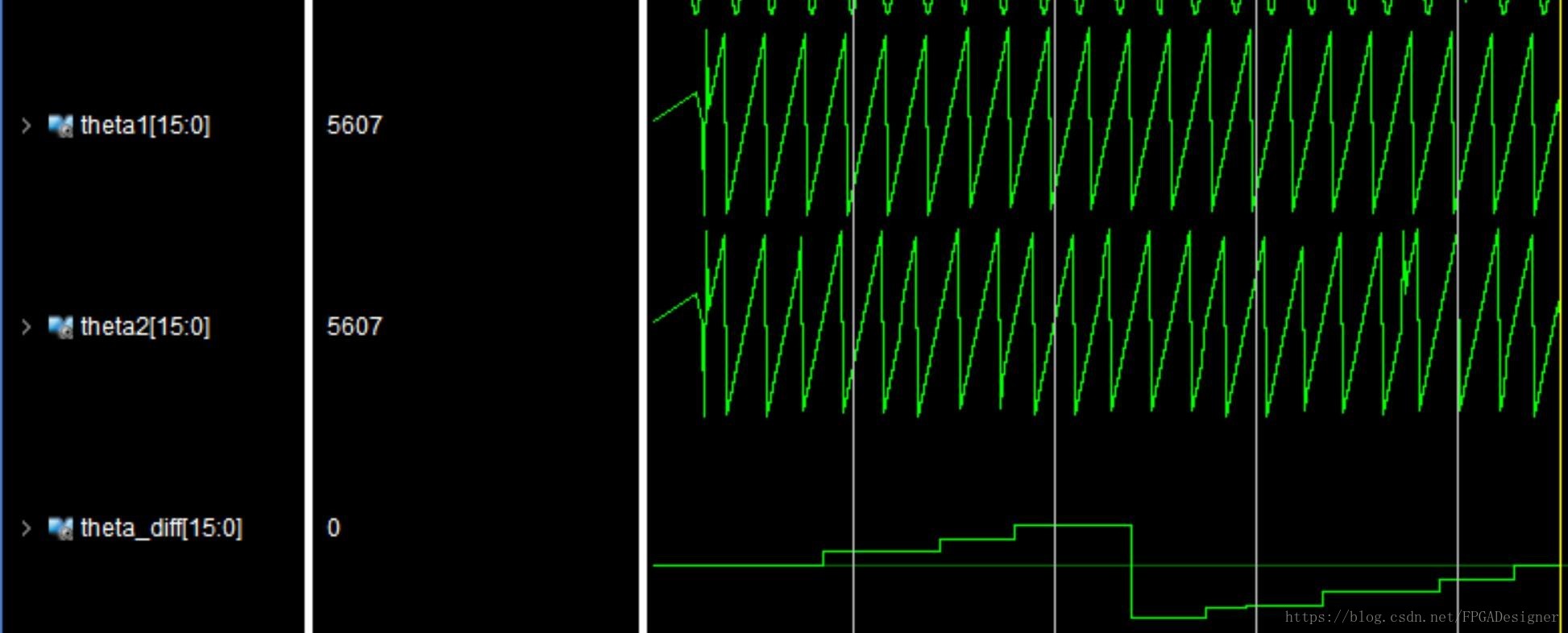

从上到下依次为信号1的i和q支路信号、信号2的i和q支路信号、信号1和信号2的相位估计(theta1与theta2)。

theta_diff为相位差。仿真中模拟了9种相位差情况,可以明显看到仿真图中的9个相位差值,经过验证结果正确。

上位机程序设计与实测

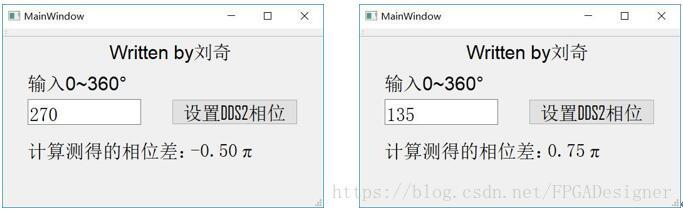

上位机使用Qt5.8(C++)开发,设计了一个简陋的界面,主要是串口通信与数据的解析处理。上位机程序可以控制DDS2的相位,并显示测得相位的结果。

FPGA工程配置完毕后,下载到FPGA开发板,与上位机连接实测,结果如下图:

0~180°即对应0~pi;180°~360度对应-pi~0。测试后功能正确。

System generator设计方法

这里在System Generator重现两路信号相位差检测的设计。这款工具可以借助Simulink平台搭建便捷强大的仿真环境,并将设计导出到Vivado工程。System Generator的使用方法可以参考博主的《学会System Generator系列》。

System Generator中搭建模型如下:

运行仿真,结果如下:

红框部分便是出错的原因,导致相位未能限制在-pi~pi之间。对减法器输出结果进行限制即可。这部分用block搭建比较麻烦,System Generator支持将部分MATLAB语法转换为HDL模型。编写一个MATLAB函数,完成相位差修正(超过pi,则减去2pi;低于-pi,则加上2pi),添加一个MCode block,导入该函数。模型连接图如下:

运行仿真,相位超前与滞后的两种情况的仿真分别如下:

都没有出现错误,结果修正正确。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?