两级运算放大器设计

cadence 电路设计

工艺tsmc18

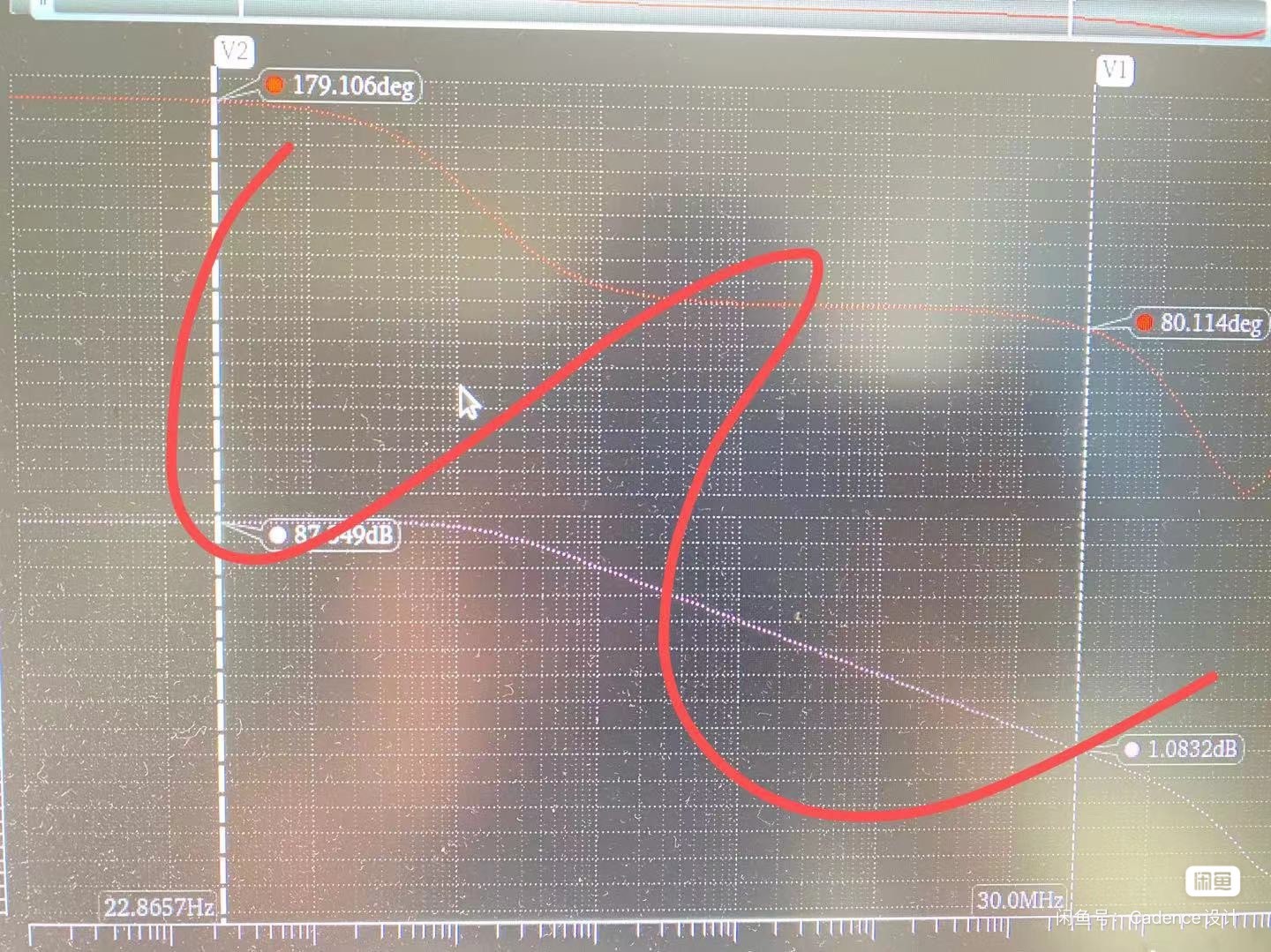

低频增益87dB

相位裕度80

单位增益带宽积GBW 30MHz

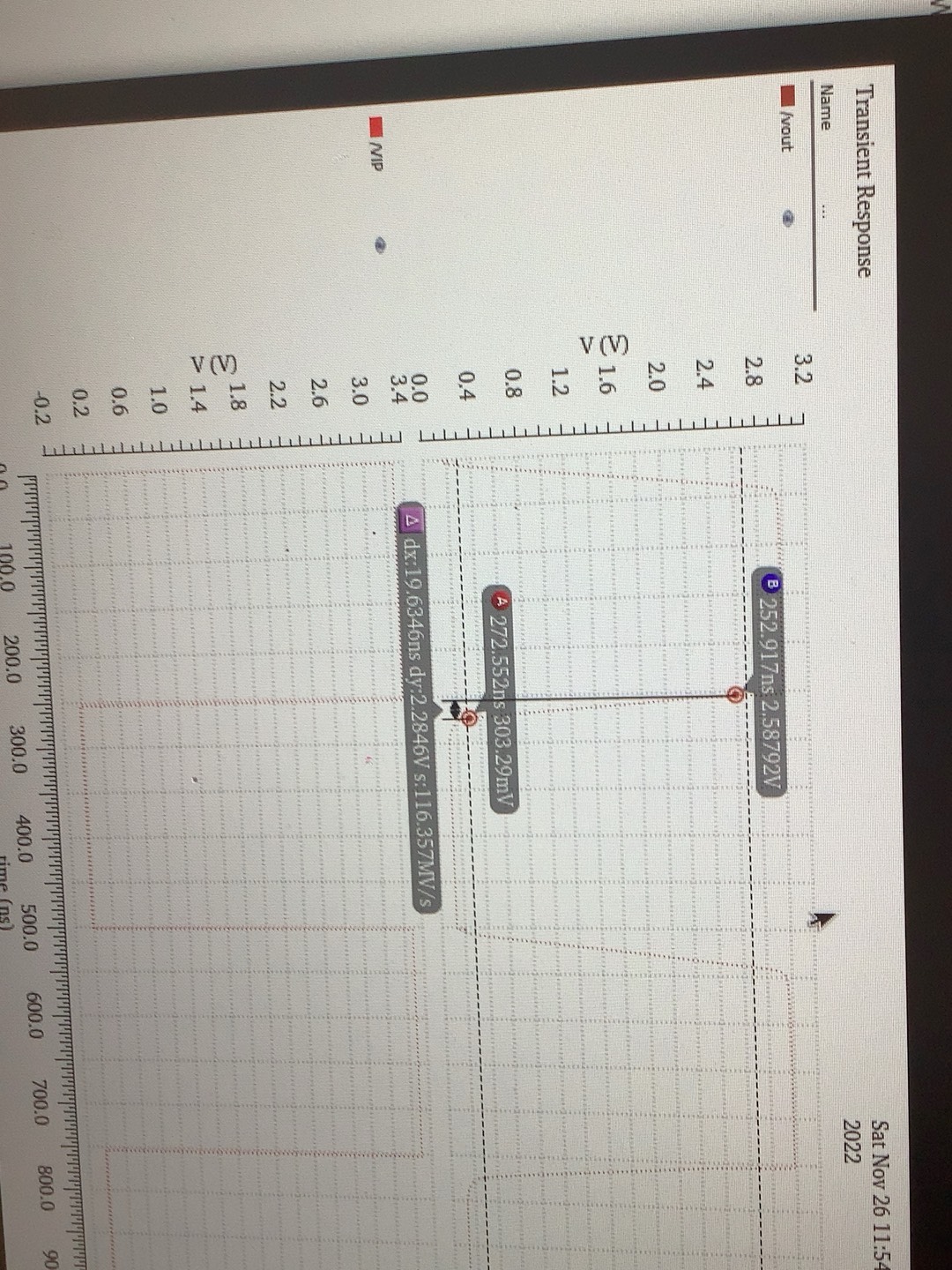

压摆率 116V us

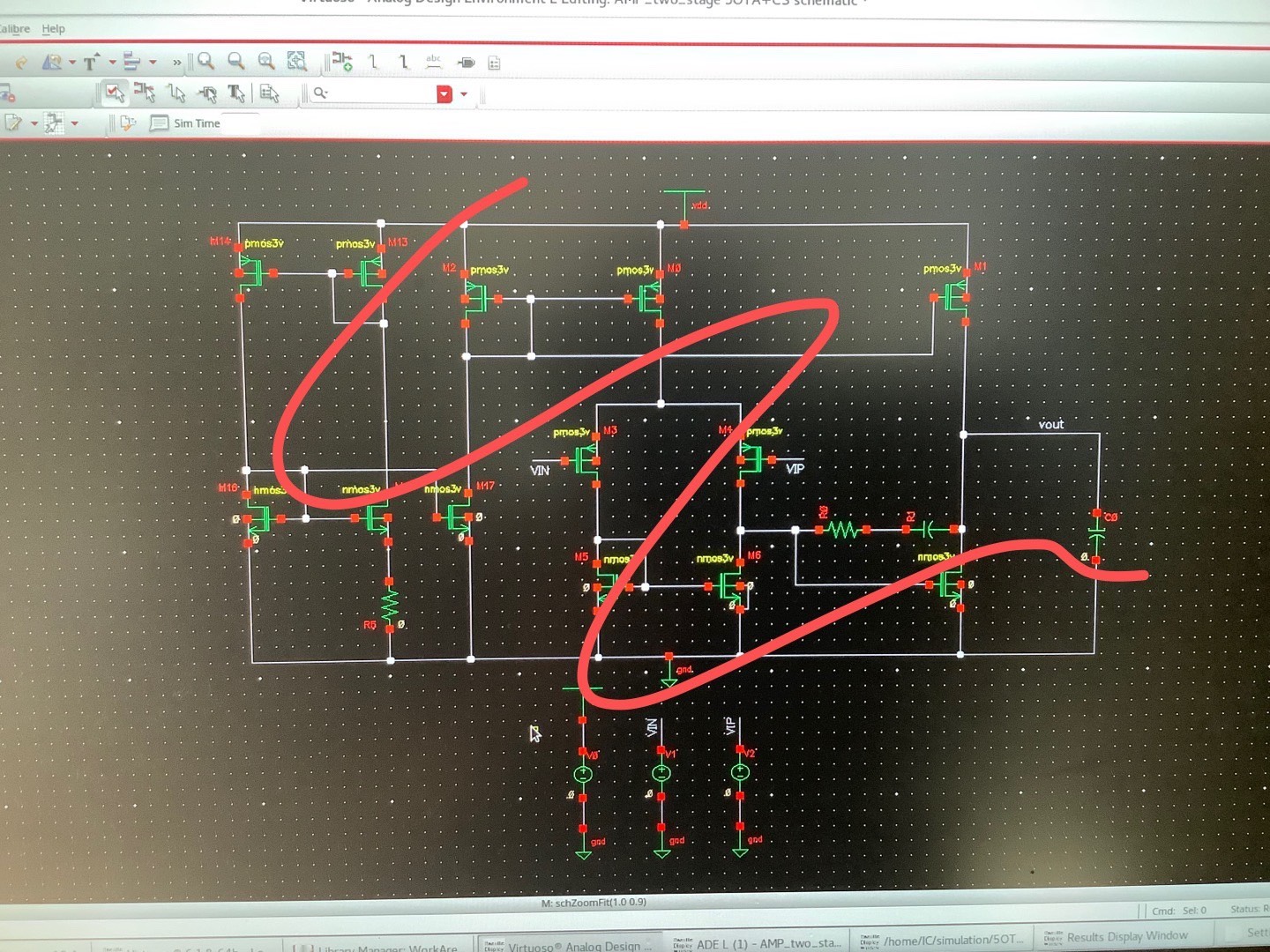

原理图带仿真状态

有版图过DRC lvs

ID:93188693525805813

老王模拟

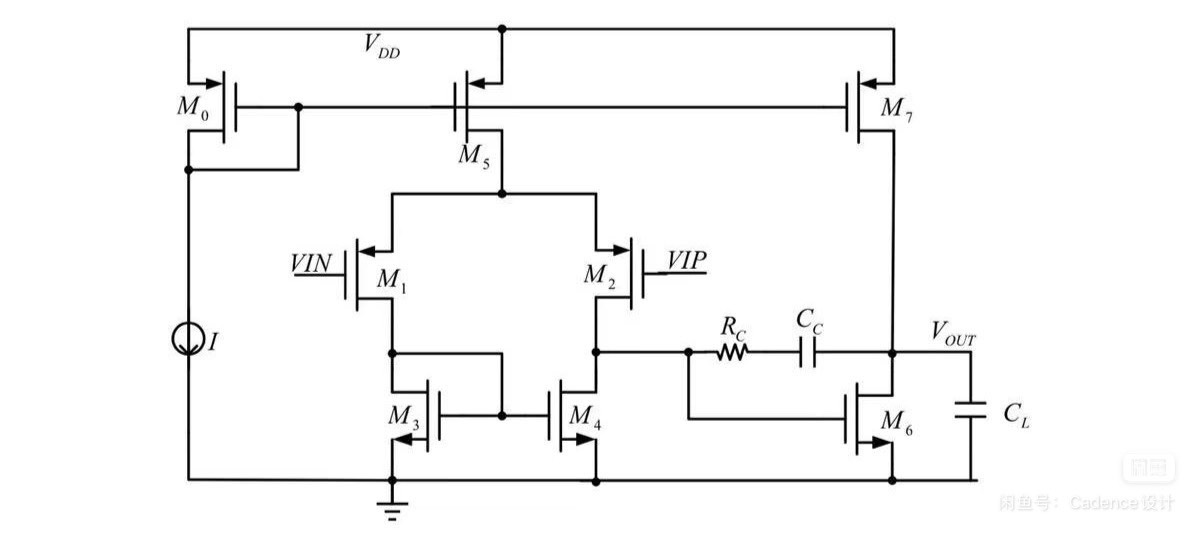

两级运算放大器设计是现代集成电路设计中的重要课题之一,它在各种电子设备中扮演着关键的角色。本文将围绕着cadence电路设计工具和tsmc18工艺展开讨论,详细介绍了低频增益、相位裕度、单位增益带宽积GBW和压摆率等重要参数的设计考虑和优化方法,并通过原理图和仿真状态演示了其工作原理。此外,本文还通过版图设计和DRC LVS验证,确保了所设计的运算放大器能够在实际制造过程中得到良好的性能。

在进行两级运算放大器设计之前,首先需要了解cadence电路设计工具的功能和使用方法。cadence是一款广泛应用于集成电路设计的软件,它提供了强大的设计和仿真功能,能够帮助工程师们进行复杂电路的设计与验证。对于两级运算放大器的设计来说,cadence的相关功能和工具十分重要,可以帮助工程师们实现设计参数的优化和性能的评估。

针对tsmc18工艺的选择,它是一种常用的CMOS工艺,具有较好的性能和可靠性。在两级运算放大器设计中,工艺的选择对性能和功耗等方面有着直接影响。tsmc18工艺的特点包括低功耗、高集成度和较高工作频率等,非常适合用于设计高性能的运算放大器。通过使用tsmc18工艺,可以在提供较高的低频增益、相位裕度和单位增益带宽积的同时,保证运算放大器的压摆率达到116V/us的设计要求。

低频增益是运算放大器设计中的一个关键指标,它反映了放大器在低频范围内的放大能力。在本设计中,通过合理的电路结构和参数选择,成功地实现了87dB的低频增益。通过对电路的优化和仿真,确保了低频增益的稳定性和可靠性,使得运算放大器能够在不同工作条件下达到一致的放大效果。

相位裕度是判断运算放大器稳定性的重要参数之一,它反映了放大器在不同频率下的相位保持能力。在本设计中,相位裕度达到了80,表明运算放大器具备较好的相位稳定性。通过设计合适的频率补偿电路和相位裕度增强电路,成功地实现了相位裕度的优化,为运算放大器提供了更好的性能和稳定性。

单位增益带宽积GBW是衡量运算放大器带宽和增益性能的重要指标之一,它是运算放大器的截止频率和增益之积。在本设计中,通过合理的电路结构和参数优化,成功地实现了30MHz的单位增益带宽积。通过仿真和分析,验证了单位增益带宽积的稳定性和可靠性,使得运算放大器能够在设计要求的工作频率范围内提供稳定的放大性能。

压摆率是运算放大器的响应速度指标,它反映了运算放大器对输入信号变化的敏感程度。在本设计中,通过适当的电路结构和参数调整,成功地实现了116V/us的压摆率。通过电路仿真和分析,验证了运算放大器对快速变化信号的高速响应能力,为运算放大器的多样化应用提供了良好的基础。

最后,在两级运算放大器的设计过程中,除了对电路参数进行仿真和优化以外,还需要进行版图设计和DRC LVS验证。版图设计是将原理图转化为实际电路的过程,需要考虑电路的布局和连线,以确保电路的良好性能和可靠性。DRC和LVS是对版图的两种验证方法,DRC验证主要检查版图与工艺规则的符合性,LVS验证主要检查原理图和版图之间的一致性。通过版图设计和DRC LVS验证,确保了所设计的两级运算放大器能够在实际制造过程中得到良好的性能

【相关代码 程序地址】: http://nodep.cn/693525805813.html

本文详细介绍了如何使用Cadence电路设计工具和TSMC18工艺设计两级运算放大器,关注低频增益、相位裕度、GBW和压摆率等关键参数,通过实例展示设计过程和仿真结果,以及版图设计和DRCLVS验证确保实际性能。

本文详细介绍了如何使用Cadence电路设计工具和TSMC18工艺设计两级运算放大器,关注低频增益、相位裕度、GBW和压摆率等关键参数,通过实例展示设计过程和仿真结果,以及版图设计和DRCLVS验证确保实际性能。

9万+

9万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?