1.设计参数

低频增益大于100dB,GBW≥1MHz,相位裕度大于60°,IVDD<3uA,CL=1pF,VDD=1.8V

2.电路结构与参数分析

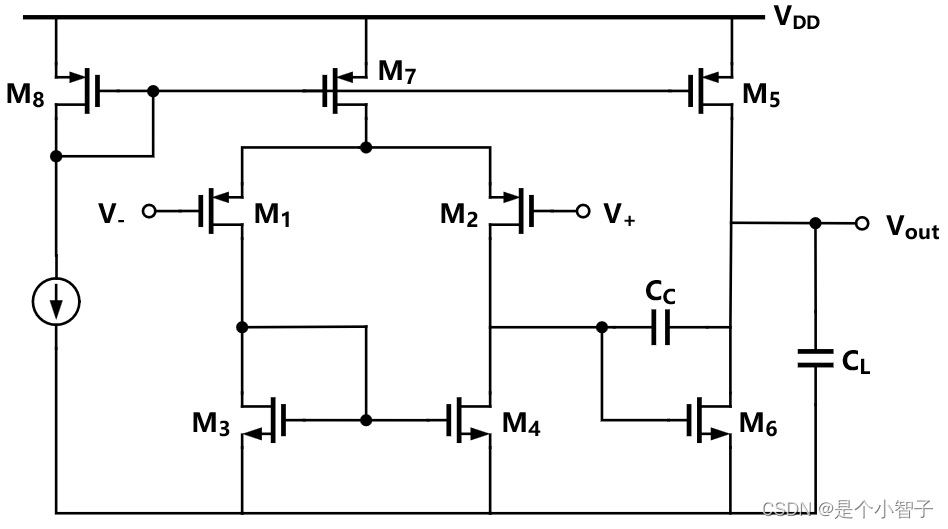

2.1.电路结构

电路的增益:

A

v

≈

g

m

1

(

r

o

2

∣

∣

r

o

4

)

g

m

6

(

r

o

5

∣

∣

r

o

6

)

\ A_v ≈ g_{m1}(r_{o2}||r_{o4})g_{m6}(r_{o5}||r_{o6})

Av≈gm1(ro2∣∣ro4)gm6(ro5∣∣ro6)

运放带宽(主极点):

f

d

=

B

W

=

1

2

π

C

C

(

1

+

A

v

2

)

(

r

o

2

∣

∣

r

o

4

)

\ f_{d}=BW=\frac{1}{2 \pi C_C(1+A_{v2})(r_{o2}||r_{o4})}

fd=BW=2πCC(1+Av2)(ro2∣∣ro4)1

增益带宽积:

G

B

W

=

B

W

×

∣

A

v

∣

=

g

m

1

2

π

C

C

\ GBW=BW\times |A_{v}|=\frac{g_{m1}}{2 \pi C_C}

GBW=BW×∣Av∣=2πCCgm1

次极点fnd与CL和运放输出电阻有关,在fnd处CC近似短路:

f

n

d

=

1

2

π

C

L

1

g

m

6

=

g

m

6

2

π

C

L

\ f_{nd}=\frac{1}{2\pi C_L\frac{1}{g_{m6}}} =\frac{g_{m6}}{2\pi C_L}

fnd=2πCLgm611=2πCLgm6

密勒电容CC还会引入正零点:

f

z

=

g

m

6

2

π

C

C

\ f_{z}=\frac{g_{m6}}{2\pi C_C}

fz=2πCCgm6

两个极点分别会产生90度相位下降。而正零点不仅会造成90度相位下降,还会使产生每十倍频+20dB的增益。因此,零极点位置不合适会导致相位裕度恶化,放大器不稳定。

2.1.频率响应分析

首先看一个最简单的单极点系统,图2.2毫无疑问是无条件稳定的。极点位置为10Hz,增益100dB,GBW=1MHz。

如果在单极点系统加入一个正零点呢?图2.3(a)正零点位置为0.5MHz,图2.3(b)正零点位置为5MHz。正零点不仅会造成90度相位下降,还会使产生每十倍频+20dB的增益。图2.3(a)由于正零点的存在,增益降到0dB前,相位已经变化了180度,系统一定不稳定。解决方法:如图2.3(b)可以将正零点远大于GBW,或者通过一些手段使其变成负零点。

二级运放有两个极点,一个零点,设置主极点fd=10Hz,次极点fnd=3MHz,零点fz=5MHz,得到图2.4系统。GBW=990KHz,相位裕度=60°。

3.gm/ID法设计步骤

当晶体管的L确定之后,后面参数均不会随着W改变:gm/ID、特征频率gm/Cgg、本征增益gmro、电流密度ID/W、过驱动电压VO。

运放设计就是设计晶体管参数VGS、VDS、W、L。VDS操作空间不大,于是就剩下VGS、W、L。而VGS又与gm和ID相关:

g

m

=

2

I

D

V

G

S

−

V

T

H

g

m

I

D

=

2

V

G

S

−

V

T

H

\begin{aligned} g_{m}=\frac{2I_{D}}{V_{GS}-V_{TH}} \\[2.8ex] \frac{g_{m}}{I_{D}}=\frac{2}{V_{GS}-V_{TH}} \end{aligned}

gm=VGS−VTH2IDIDgm=VGS−VTH2 可见,确定了gm/id,就可以得到VGS。于是设计步骤大致为:根据频率特性确定gm;根据功耗和摆率确定id;根据增益确定L;当VGS和L都找到之后W也就被唯一确定。

(1)确定放大管gm

前面2.1节分析了二级运放频率特性,得到了相位裕度60°的结果,按照之前分析结果列出下面方程:

{

g

m

1

2

π

C

C

=

G

B

W

f

n

d

=

g

m

6

2

π

C

L

=

3

G

B

W

f

z

=

g

m

6

2

π

C

C

=

5

G

B

W

\left\{ \begin{aligned} &\frac{g_{m1}}{2πC_{C}}=GBW \\[2.5ex] &f_{nd}=\frac{g_{m6}}{2πC_{L}}=3GBW \\[2.5ex] &f_{z}=\frac{g_{m6}}{2πC_{C}}=5GBW \end{aligned} \right.

⎩

⎨

⎧2πCCgm1=GBWfnd=2πCLgm6=3GBWfz=2πCCgm6=5GBW设计要求GBW为1MHz,这里留出一定裕度,令GBW=1.5MHz。这就是一个三元一次方程,求解得到:

{

g

m

1

=

5.6

μ

S

g

m

6

=

28

μ

S

C

C

=

0.6

p

F

\left\{ \begin{aligned} &g_{m1}=5.6μS \\[2.5ex] &g_{m6}=28μS \\[2.5ex] &C_{C}=0.6pF \end{aligned} \right.

⎩

⎨

⎧gm1=5.6μSgm6=28μSCC=0.6pF (2)确定支路电流

可以根据摆率大小来分配每一级电流大小。参数指标并没有规定摆率大小,但是IVDD<3μA,暂定第二级约为1.8μA,第一级0.7μA。(根据计算结果gm6=5gm1,流过第二级M6的电流不能太小)

(3)到这里就可以得到放大管M1、M6的gm/id≈16

两级电流分配不同,放大管gm/id值也会不同,根据具体指标作出改变。电流管的gm/id值一般小于放大管,当MOS管作为电流源时,gm越小输出电流噪声越小,可以取gm/id=10。

(4)得到电流管gm

第一级电流管gm3 =gm4=3.5μS,第二级电流管gm6 =16μS。

(5)根据增益要求选择L

(6)选择 W

仿真得到 ID/W~ gm/id 的曲线得到 ID/W 的值,然后得到 W。其他参数固定后,改变W,并不会影响晶体管本征增益gmro和特征频率fT。

4.运放第一级设计

第一级运放PMOS作为放大管,NMOS作为电流管。按照第3节的步骤来设计,(1)-(4)步找到了放大管gm/id=16,电流管gm/id=10,也确定了每个管子的gm 。

4.1.选择L

晶体管的本征增益为gmro,与L相关。

设计要求低频增益大于100dB,平分到每一级就要大于50dB。转换为放大倍数,并留出一定的余量得到每一级放大管本征增益self_gain=gmro≥800。

以PMOS为例,将其W、L、Vds、Vgs设置为变量。

仿真输出的横轴设置为gm/id,纵轴设置为self_gain。也就是PMOS管的增益随gm/id变化的趋势。然后对L从5um~15um扫描,然后选取合适的L。

取放大管gm/id=16,电流管gm/id=10,然后得到放大管PMOS的L=12um,电流管NMOS的L=15um。

4.2.选择W

当gm/id和L确定之后,MOS管的电流密度也就随之确定。每个MOS管的电流也已知,就可以将W计算出来。

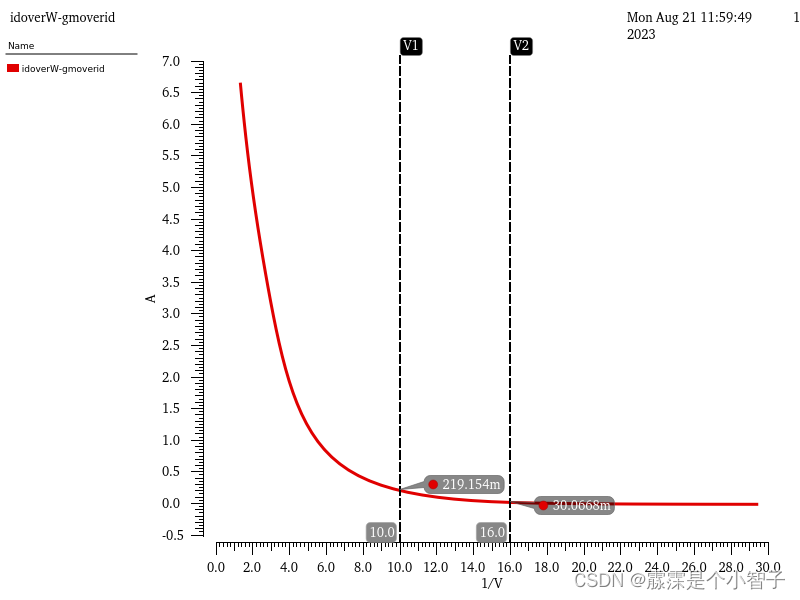

图4.3是PMOS电流密度仿真,根据仿真结果可以计算M1、M2的W。

W

1

,

2

=

I

D

1

,

2

0.024

≈

17

u

m

\ W_{1,2}=\frac{I_{D1,2}}{0.024}≈17um

W1,2=0.024ID1,2≈17um

图4.4是NMOS电流密度仿真,根据仿真结果可以计算M3、M4的W。

W

3

,

4

=

I

D

1

,

2

0.219

≈

1.8

u

m

\ W_{3,4}=\frac{I_{D1,2}}{0.219}≈1.8um

W3,4=0.219ID1,2≈1.8um

4.5.第一级仿真

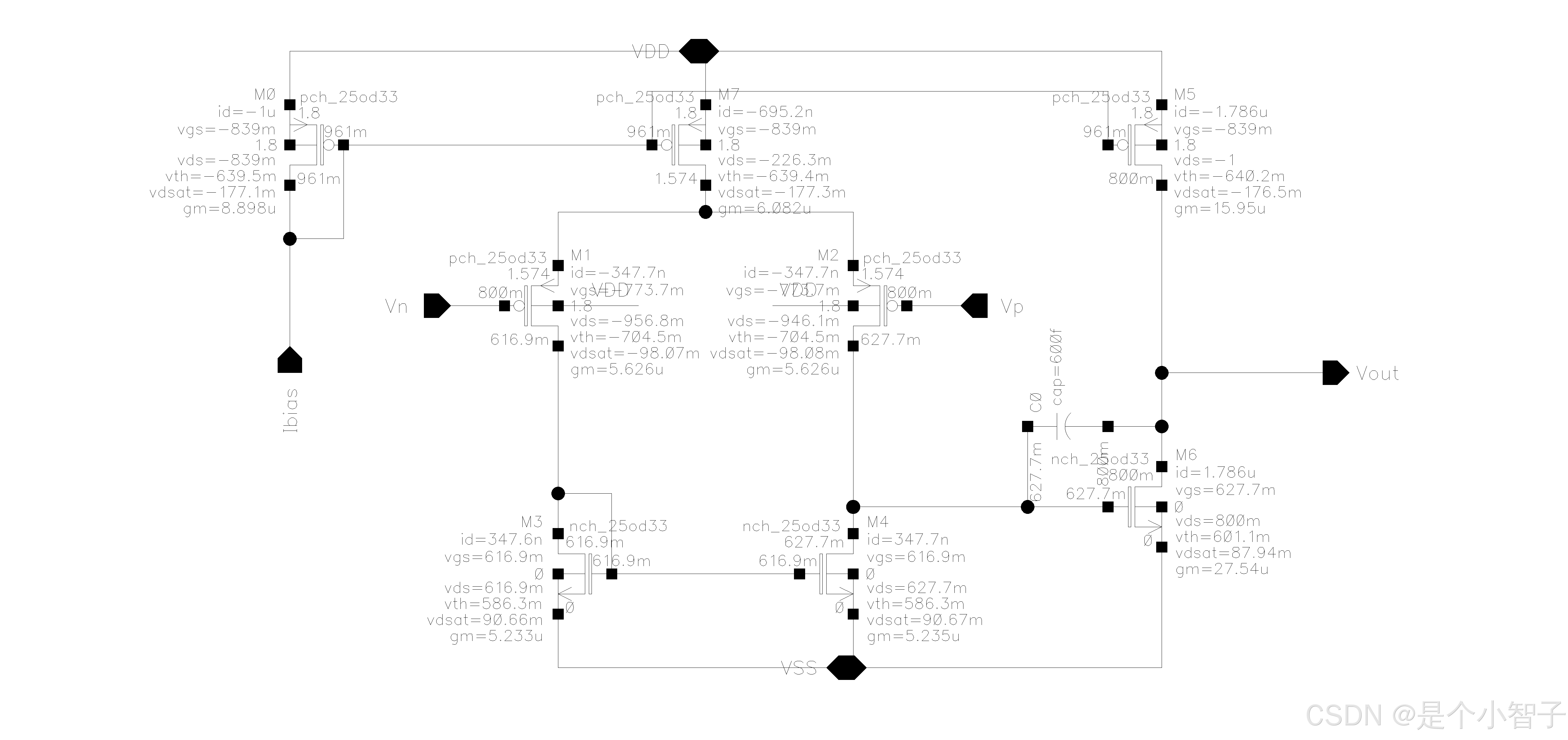

图4.5为直流仿真结果,VDD=1.8V,放大管的偏置电压vp=vn=800mV。

5.运放第二级设计

第二级放大器NMOS晶体管M6为放大管,PMOS晶体管M5为电流管。和第一级一样,先确定L,再确定W。

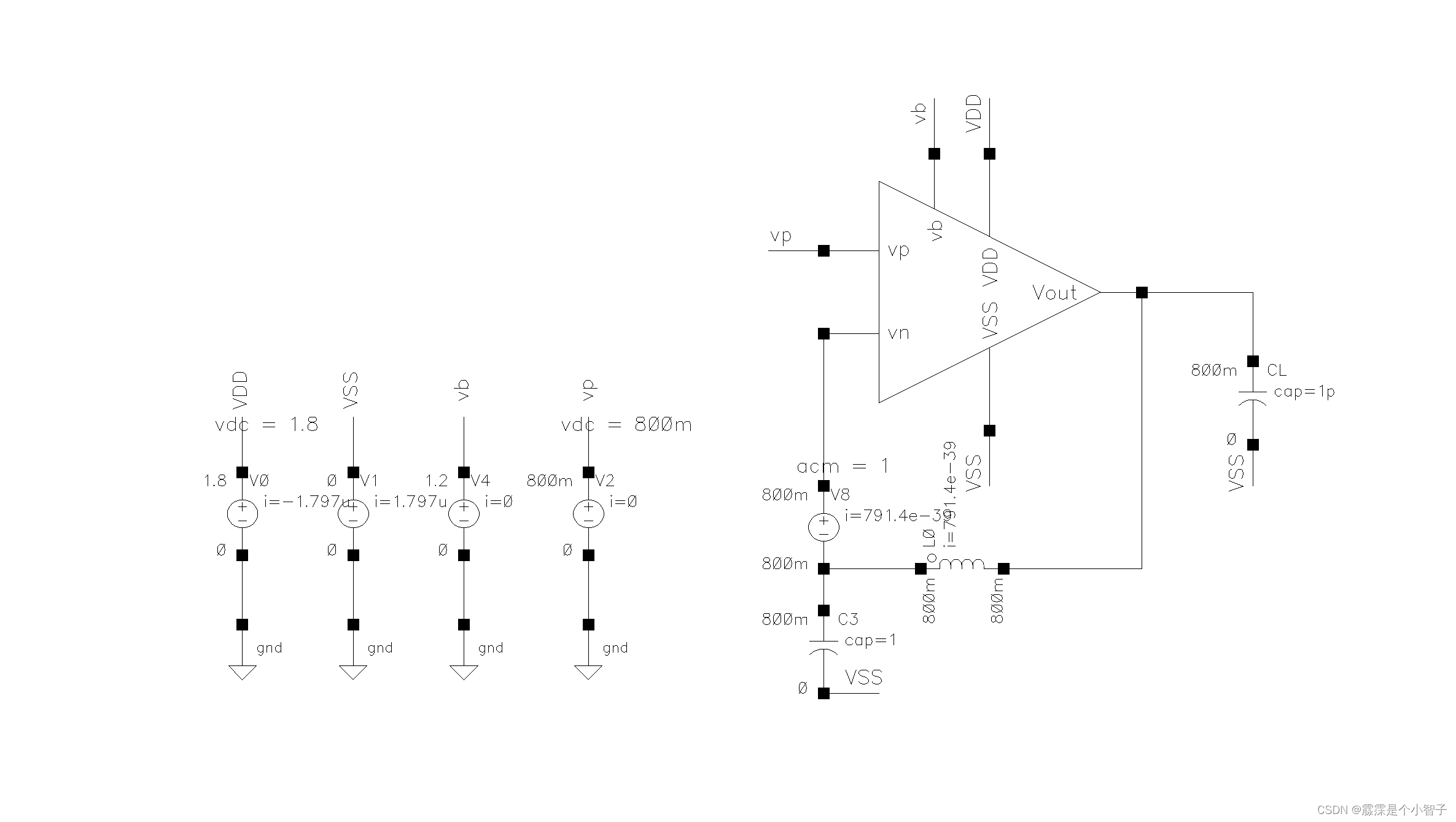

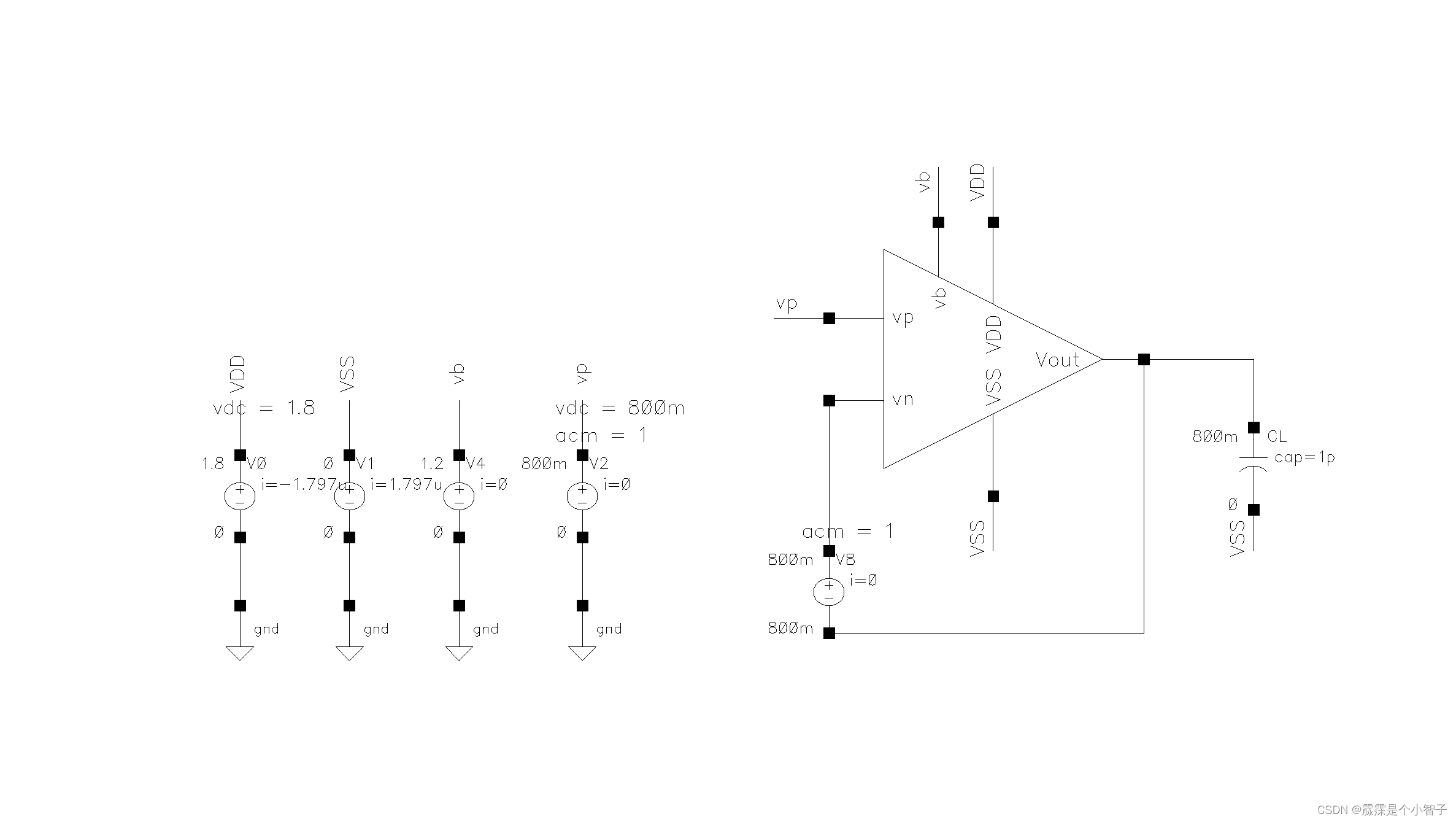

6.运放仿真与分析

6.1.dc仿真

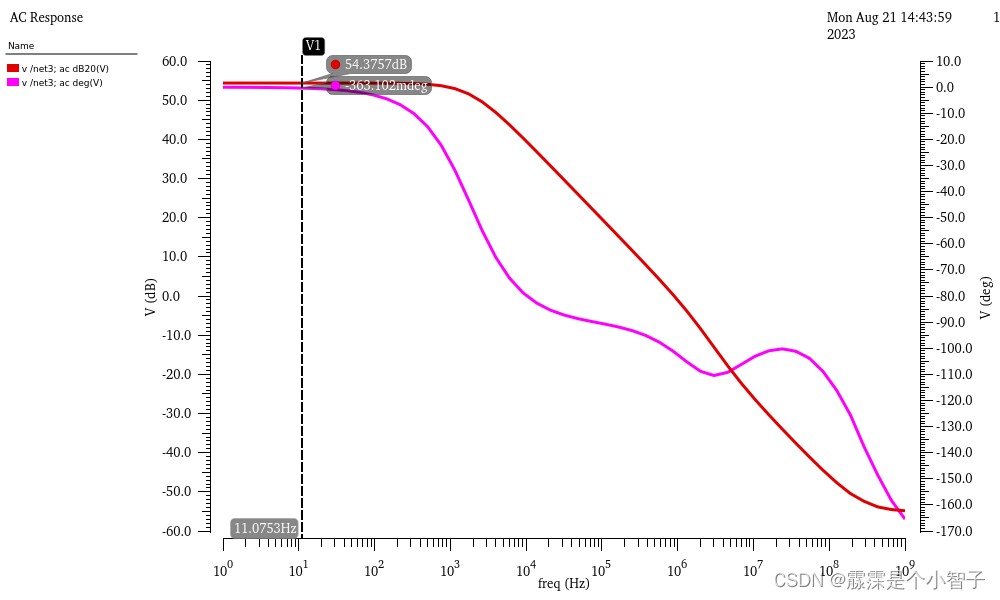

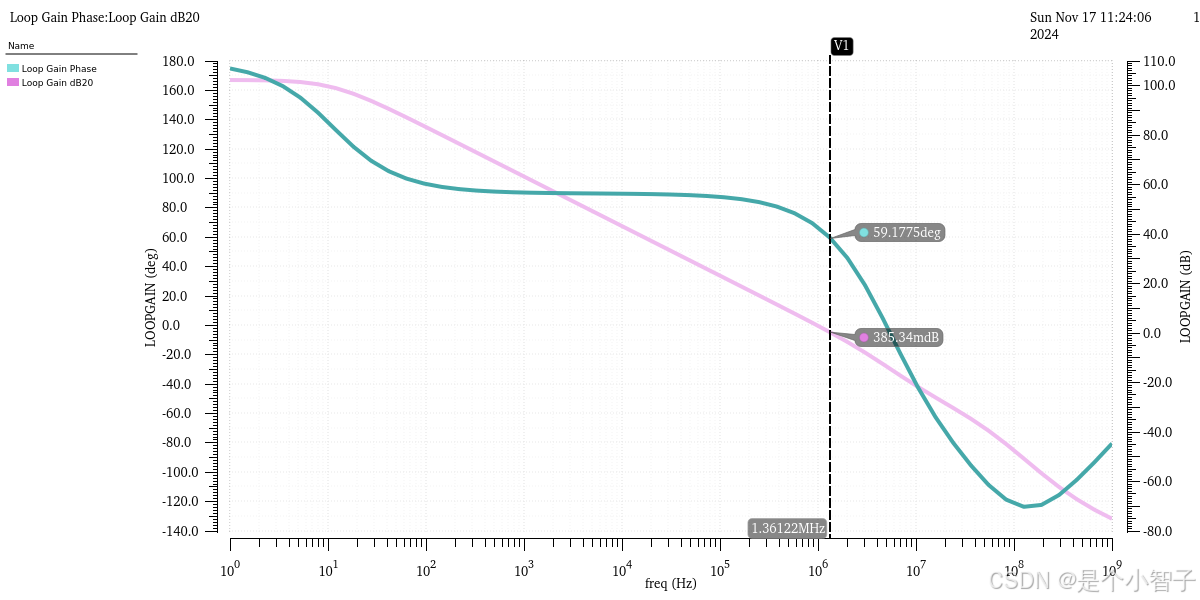

6.2.ac仿真

从仿真结果来看,低频增益大于100dB,GBW=1.36MHz,相位裕度59°,与之前的分析是基本一致的。

6.3.PSRR仿真

电源抑制比:

P

S

R

R

=

A

V

∣

v

d

d

=

0

A

D

D

∣

v

i

n

=

0

PSRR=\frac{A_V|_{v_{dd}=0}}{A_{DD}|_{v_{in}=0}}

PSRR=ADD∣vin=0AV∣vdd=0

式中vdd是电源上的交流小信号,vin是输入端的交流小信号。

按照图6.3将运算放大器连接成单位增益负反馈结构,即反相输入端和输出端短接。将差分输入信号设为 0,在电源电压源添加1V的交流分量vdd,这时的小信号输出可以表示为:

A

V

(

v

p

−

v

o

u

t

)

+

A

D

D

⋅

v

d

d

=

v

o

u

t

v

o

u

t

v

d

d

≈

A

D

D

A

V

=

1

P

S

R

R

20

l

g

P

S

R

R

=

−

20

l

g

v

o

u

t

v

d

d

\begin{aligned} A_V(v_p-&v_{out})+A_{DD}·v_{dd}=v_{out} \\[2.5ex] \frac{v_{out}}{v_{dd}}&≈\frac{A_{DD}}{A_{V}}=\frac{1}{PSRR} \\[2.5ex] 20lg_{}&{PSRR}=-20lg_{}{\frac{v_{out}}{v_{dd}}} \end{aligned}

AV(vp−vddvout20lgvout)+ADD⋅vdd=vout≈AVADD=PSRR1PSRR=−20lgvddvout

得到输出端的增益曲线取负数就是PSRR特性曲线。

6.4.CMRR仿真

共模抑制比(Common Mode Reject Ratio,CMRR)的定义为运算放大器差分输入增益与共模增益的比值:

C

M

R

R

=

A

V

A

C

M

CMRR=\frac{A_V}{A_{CM}}

CMRR=ACMAV

按照图6.5将运算放大器连接成单位增益负反馈结构。在运算放大器的同相和反相输入端加上相同的小信号电压vcm,这时的小信号输出可以表示为:

A

C

M

v

c

m

+

A

V

[

v

c

m

−

(

v

c

m

+

v

o

u

t

)

]

=

v

o

u

t

v

o

u

t

v

c

m

≈

A

C

M

A

V

=

1

C

M

R

R

\begin{aligned} A_{CM}v_{cm}+A_V[v_{cm}-&(v_{cm}+v_{out})]=v_{out} \\[2.5ex] \frac{v_{out}}{v_{cm}}≈\frac{A_{CM}}{A_{V}}&=\frac{1}{CMRR} \\[2.5ex] \end{aligned}

ACMvcm+AV[vcm−vcmvout≈AVACM(vcm+vout)]=vout=CMRR1

得到输出端的增益曲线取负数就是CMRR特性曲线。

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?