目录

1、应用74161和必要的门电路设计实现“2421BCD码”十进制加法计数器。

2、应用74161和必要的门电路设计实现“5421BCD码”十进制加法计数器。

3、应用74161和必要的门电路设计实现“余3码”十进制加法计数器。

5、应用1片74390同时实现 “8421BCD码”和“5421BCD码”十进制计数器设计。

6、应用74138和必要的门电路设计一个1位全加器电路(变量自己合理设置)。

7、应用74138和必要的门电路设计一个1位全减器电路((变量自己合理设置)。

常见的BCD码

| 十进制数 | 8421码 | 2421码 | 5421码 | 余3码 |

|---|---|---|---|---|

| 0 | 0000 | 0000 | 0000 | 0011 |

| 1 | 0001 | 0001 | 0001 | 0100 |

| 2 | 0010 | 0010 | 0010 | 0101 |

| 3 | 0011 | 0011 | 0011 | 0110 |

| 4 | 0100 | 0100 | 0100 | 0111 |

| 5 | 0101 | 1011 | 1000 | 1000 |

| 6 | 0110 | 1100 | 1001 | 1001 |

| 7 | 0111 | 1101 | 1010 | 1010 |

| 8 | 1000 | 1110 | 1011 | 1011 |

| 9 | 1001 | 1111 | 1100 | 1100 |

1、应用74161和必要的门电路设计实现“2421BCD码”十进制加法计数器。

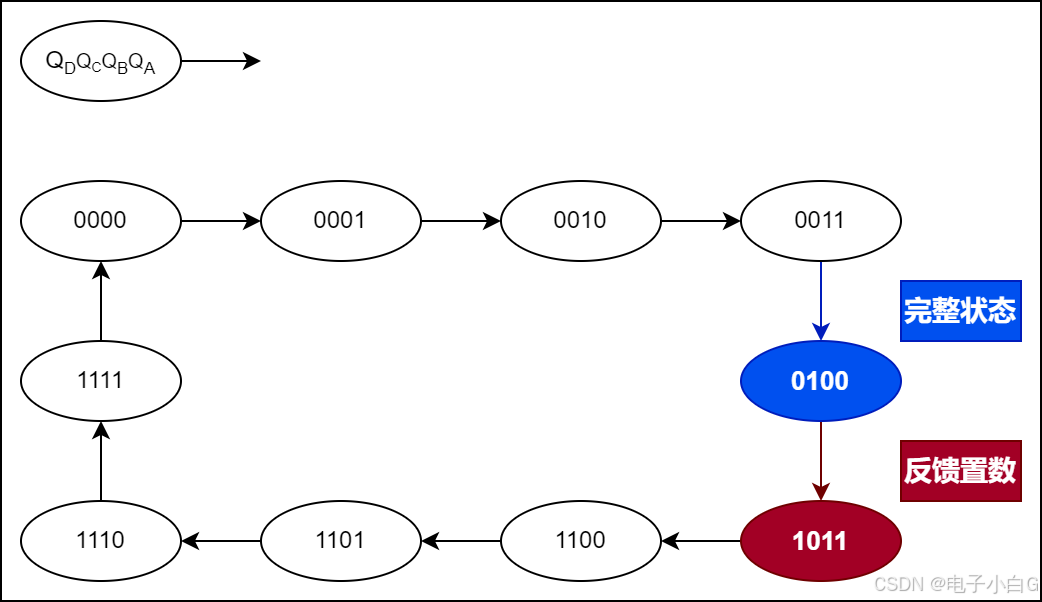

状态图:

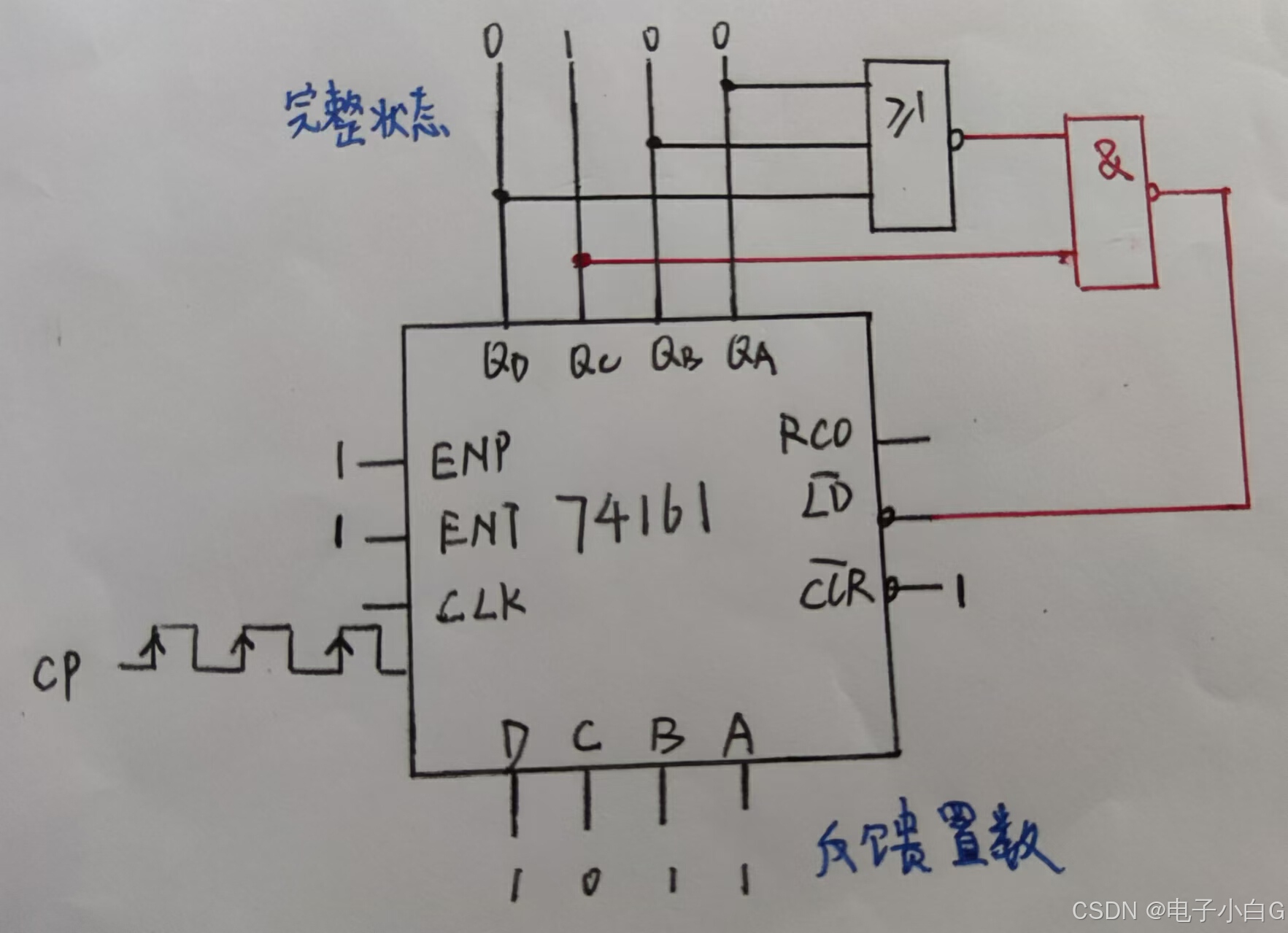

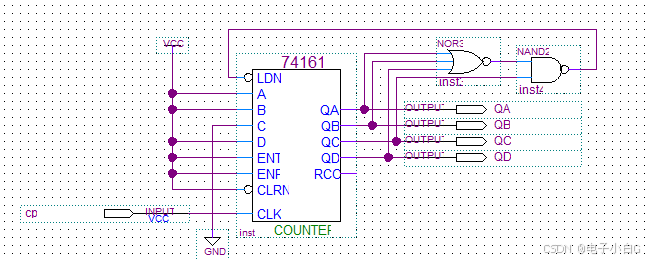

电路图:

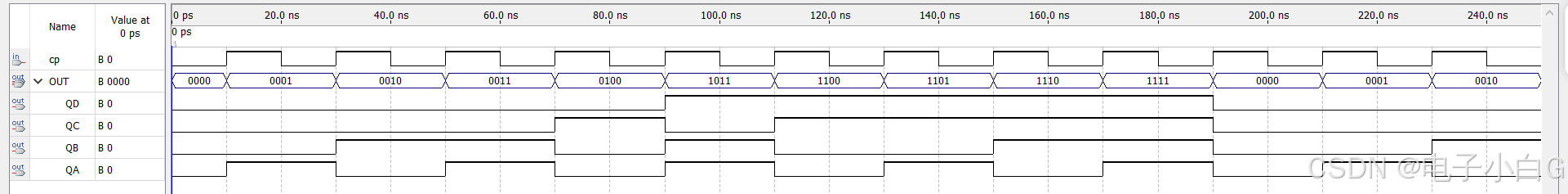

仿真结果:

2、应用74161和必要的门电路设计实现“5421BCD码”十进制加法计数器。

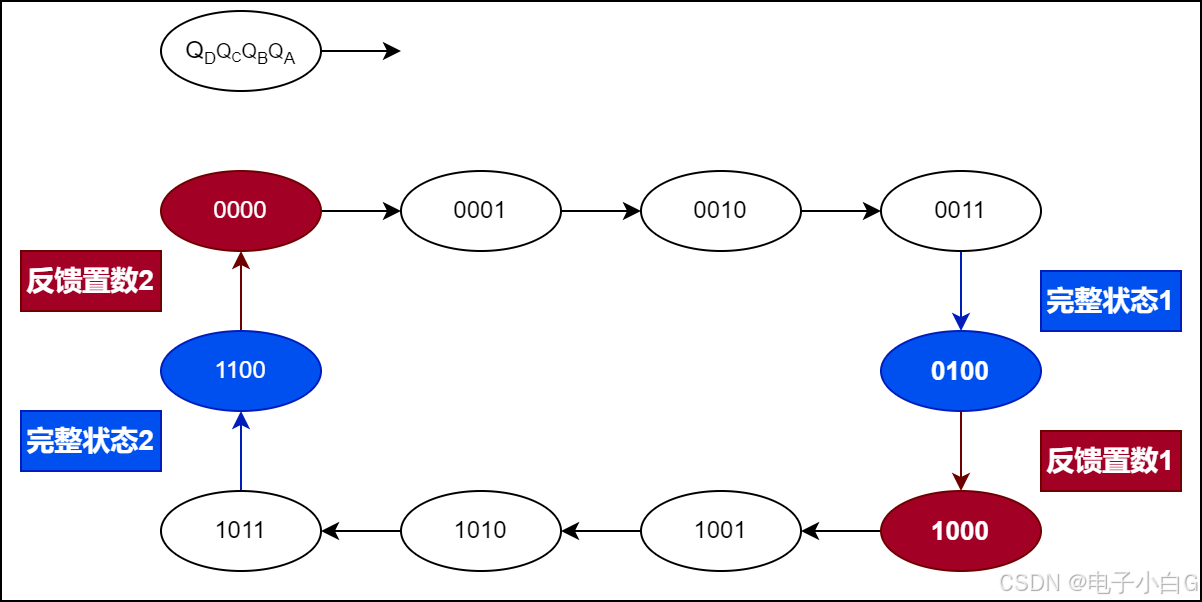

状态图:

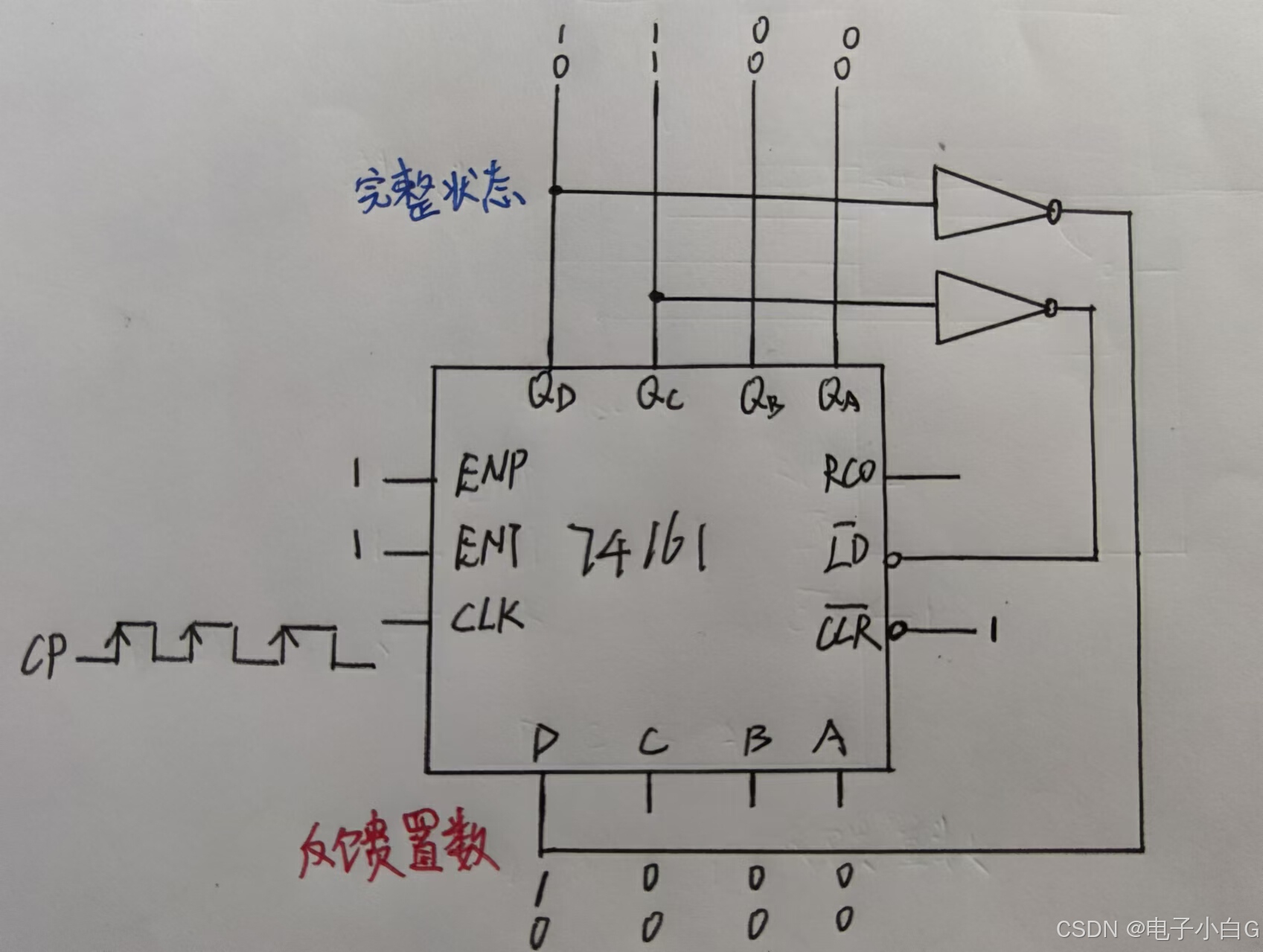

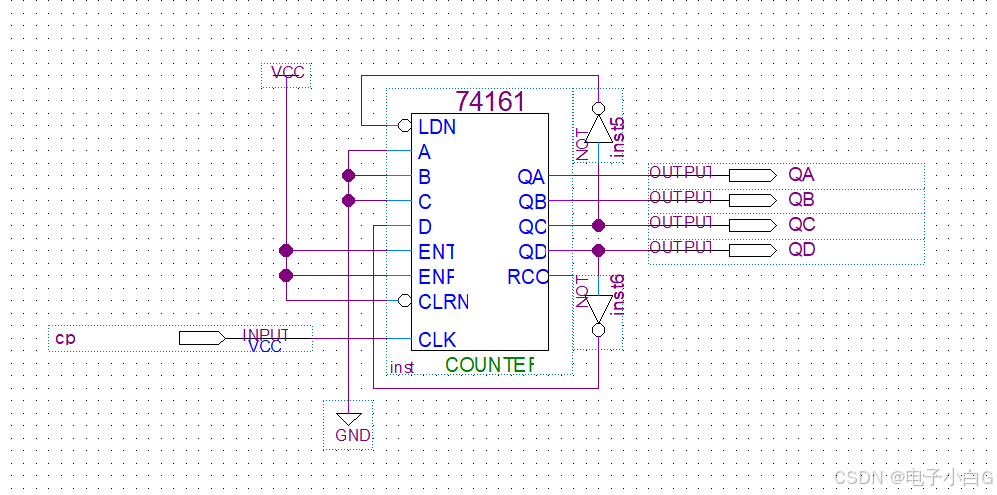

电路图:

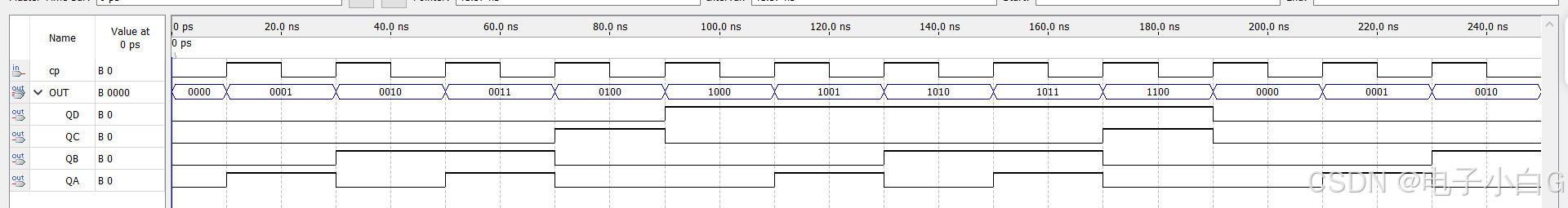

仿真结果:

3、应用74161和必要的门电路设计实现“余3码”十进制加法计数器。

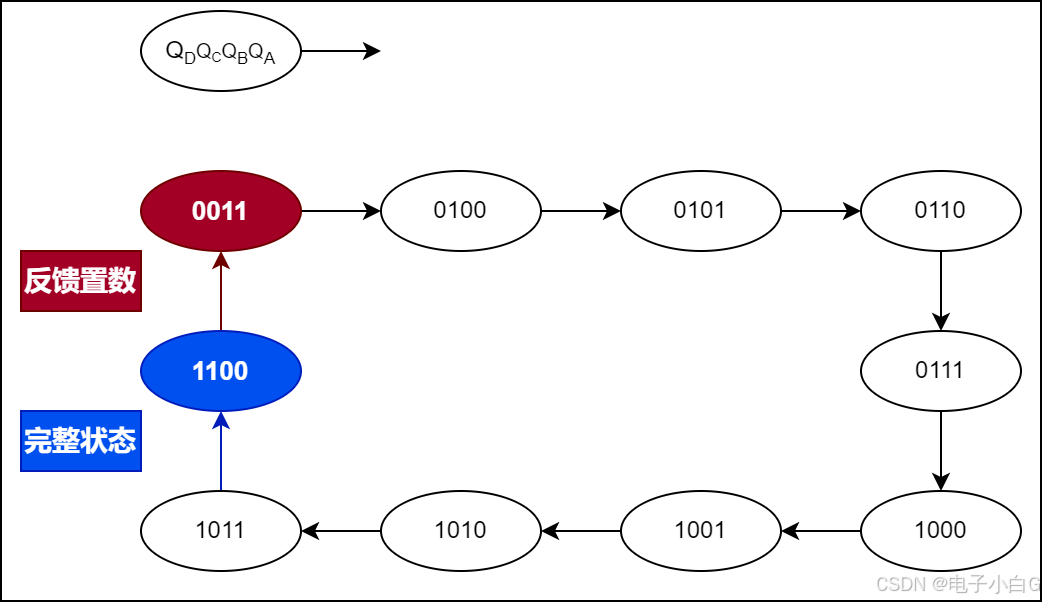

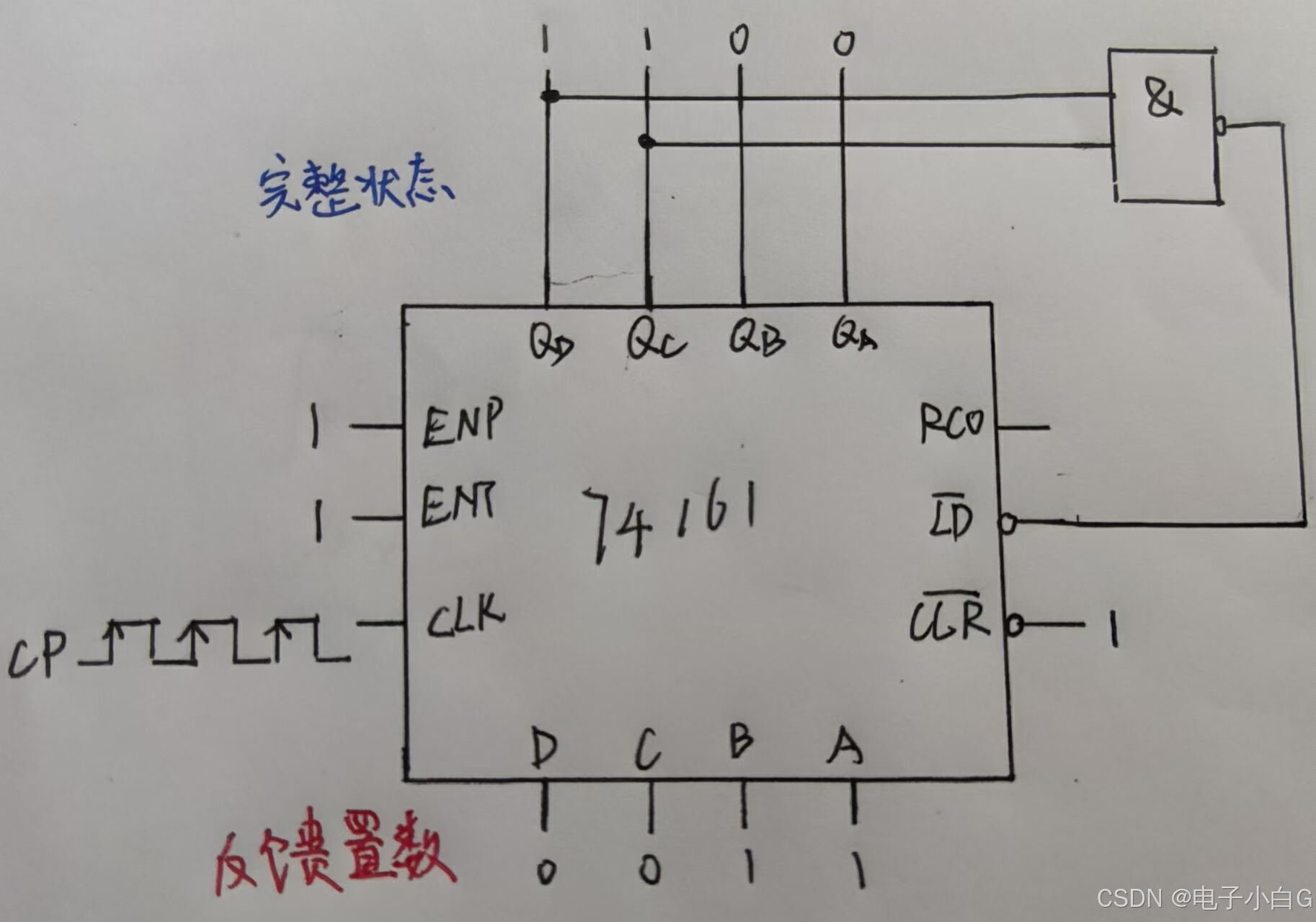

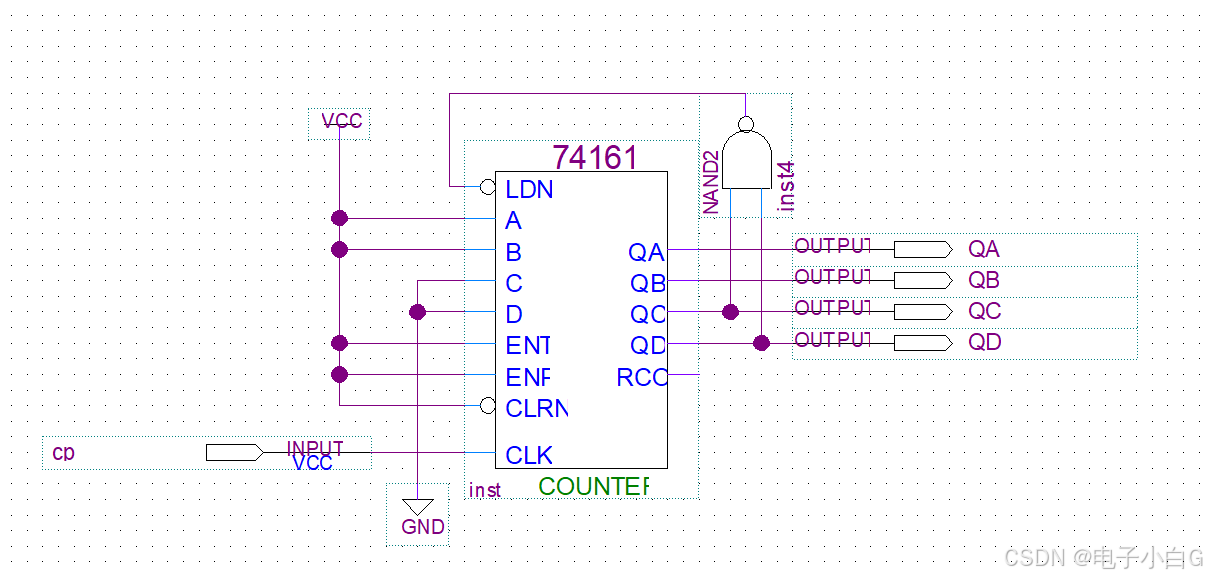

状态图:

电路图:

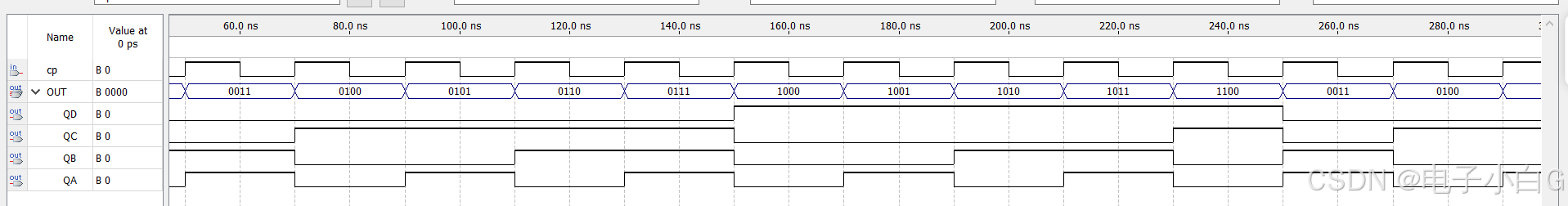

仿真结果:

4、应用下降沿触发的JK触发器实现4位二进制计数电路设计。

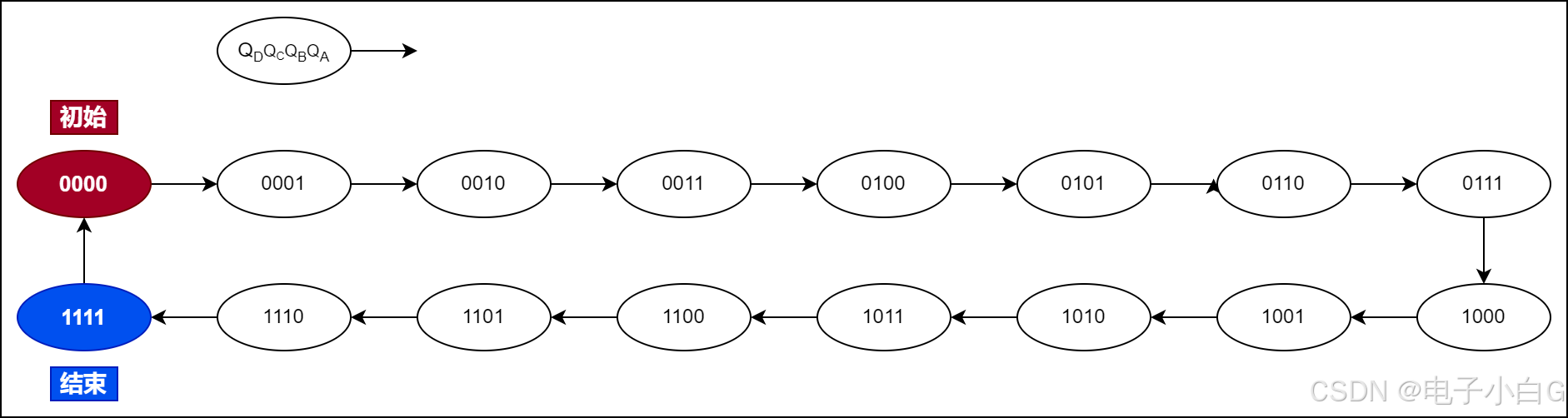

状态图:

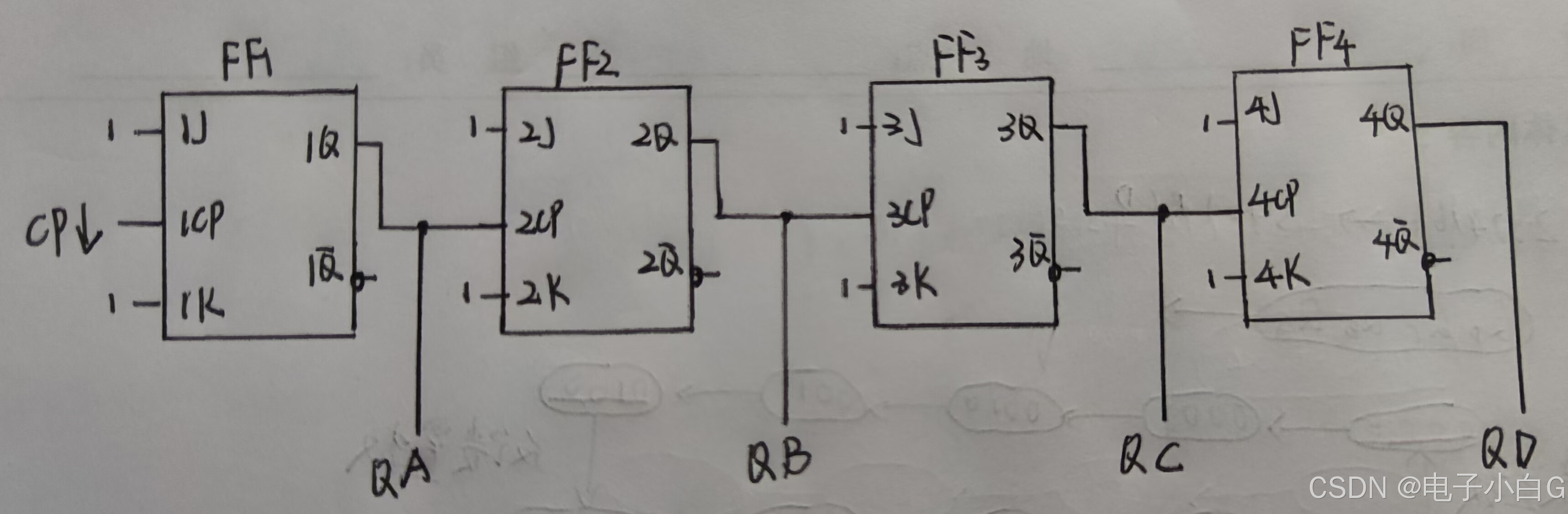

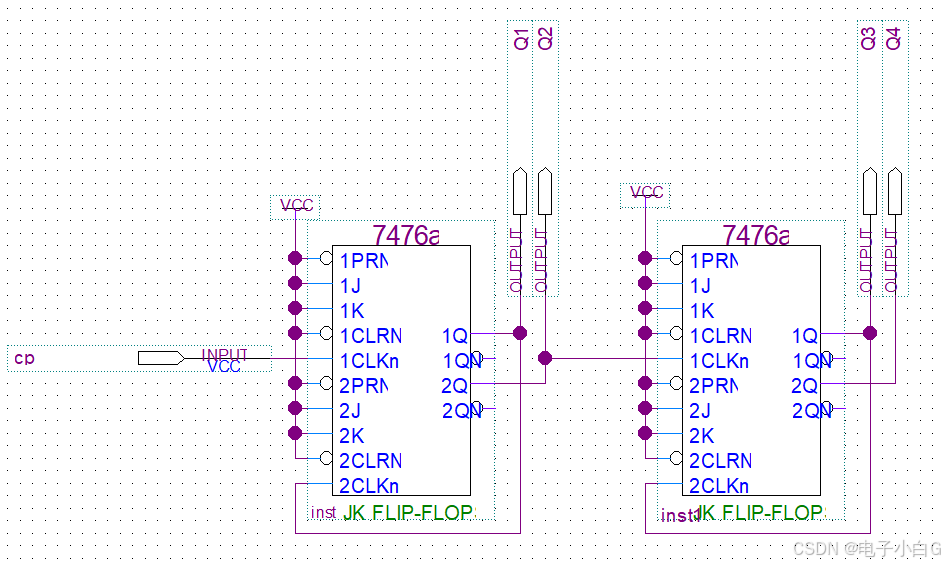

电路图:

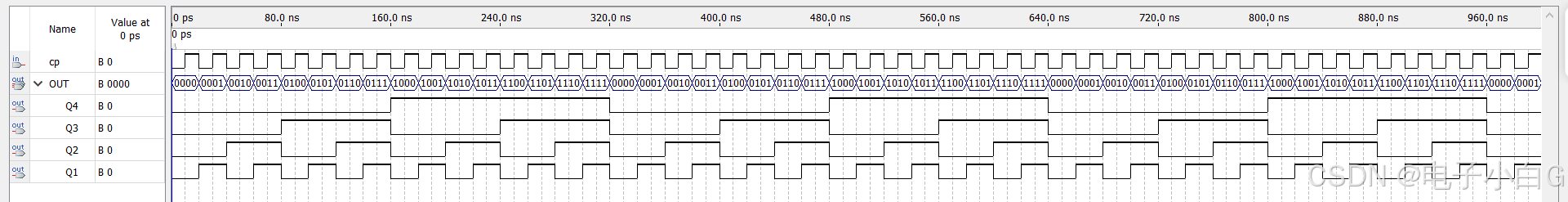

仿真结果:

5、应用1片74390同时实现 “8421BCD码”和“5421BCD码”十进制计数器设计。

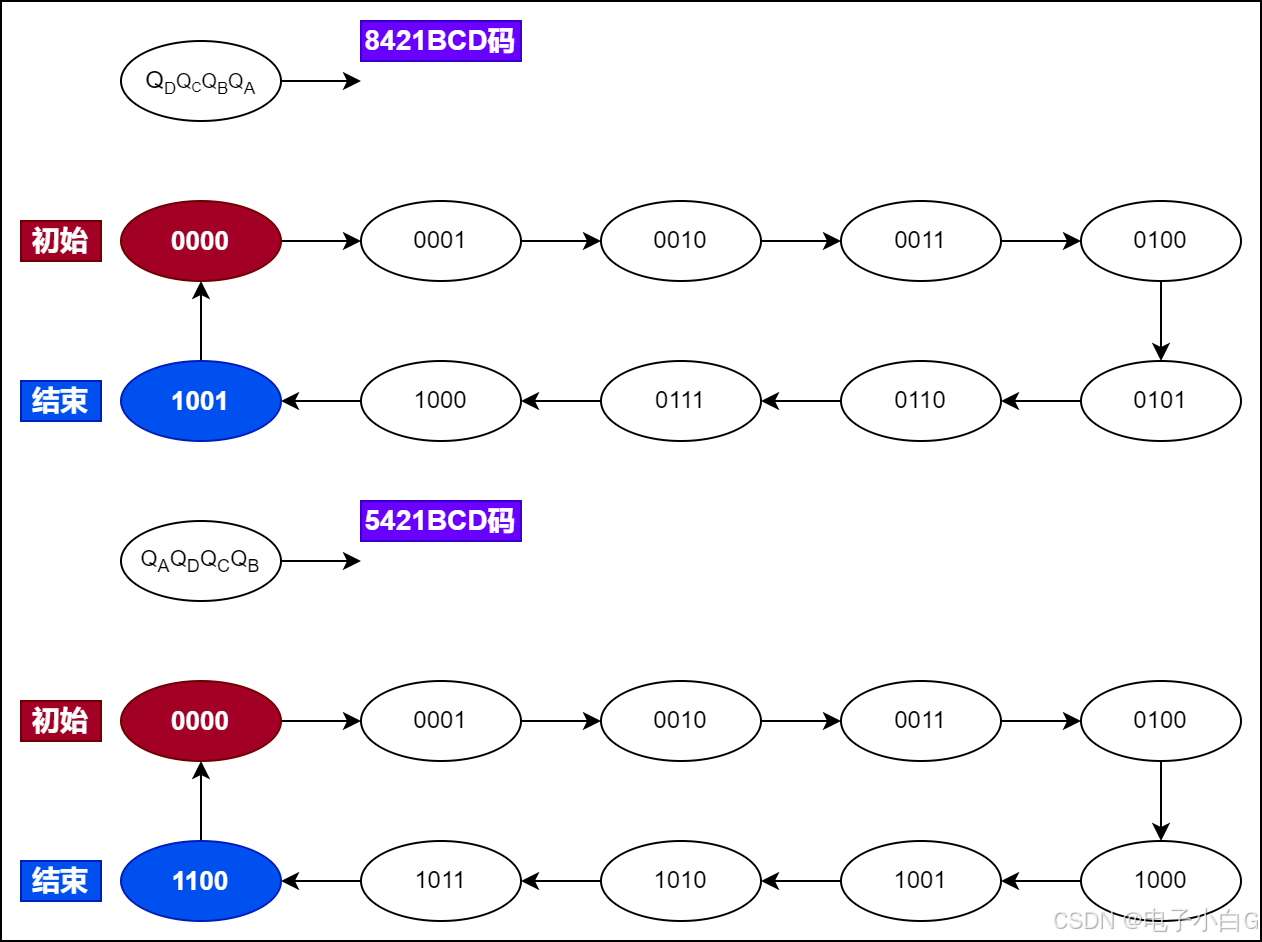

状态图:

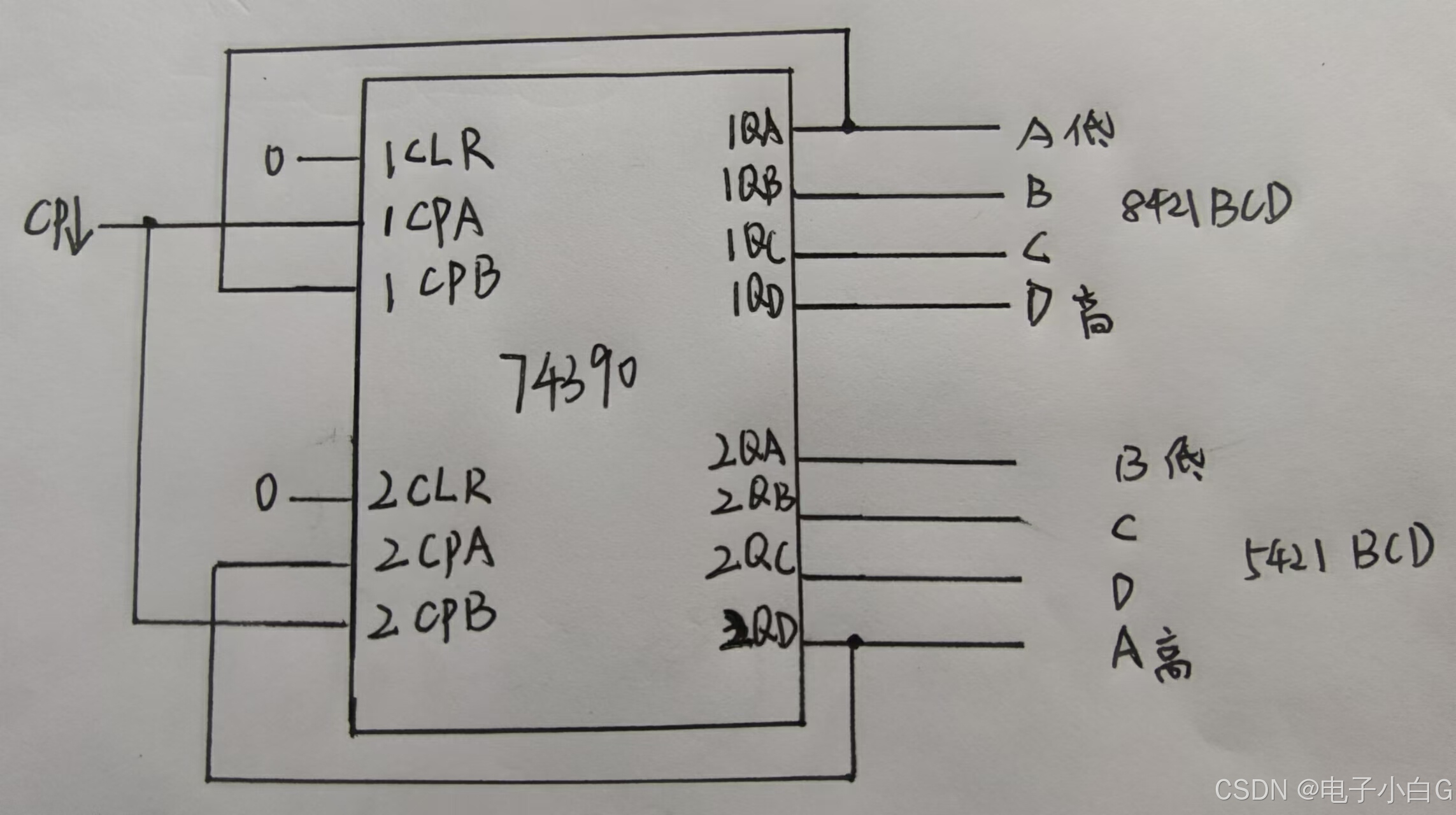

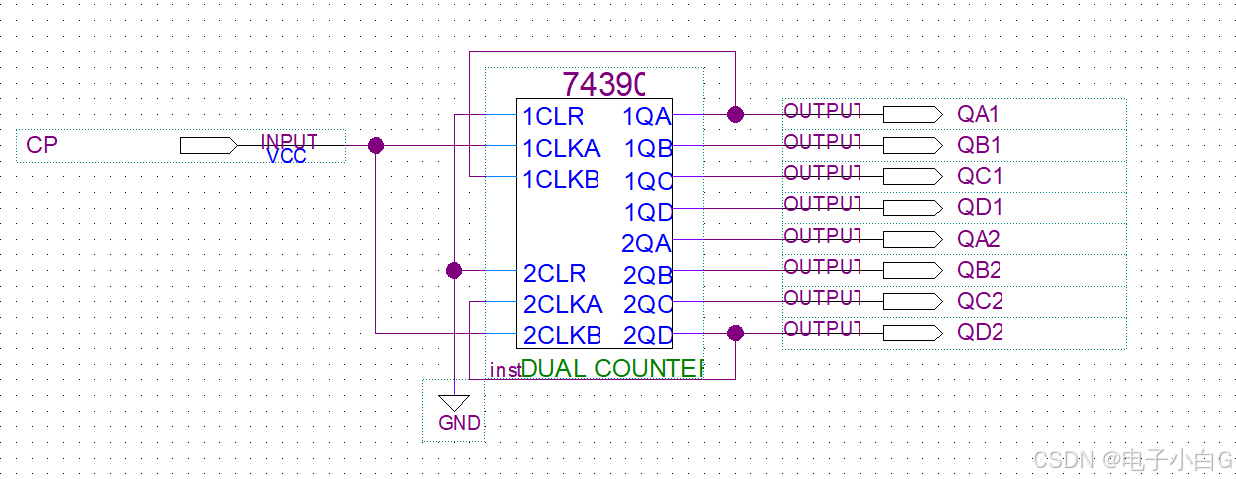

电路图:

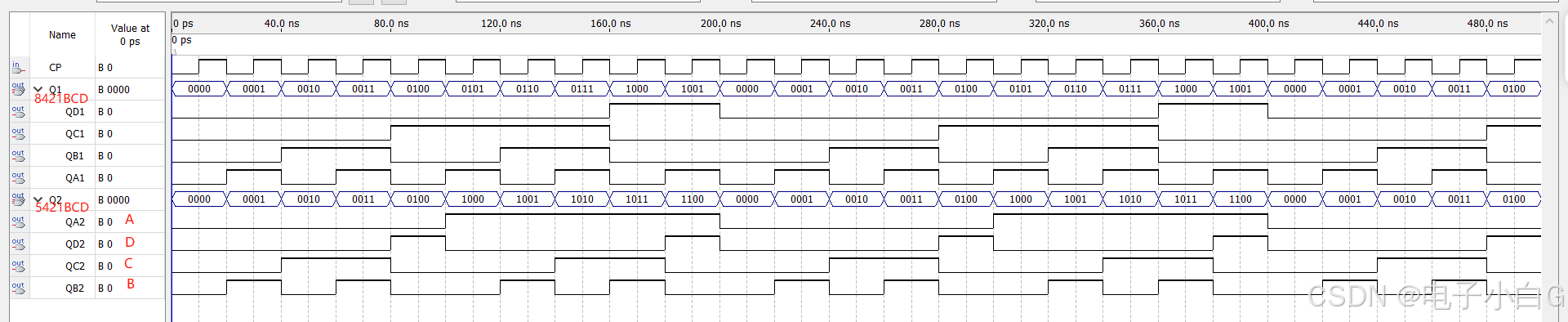

仿真结果:

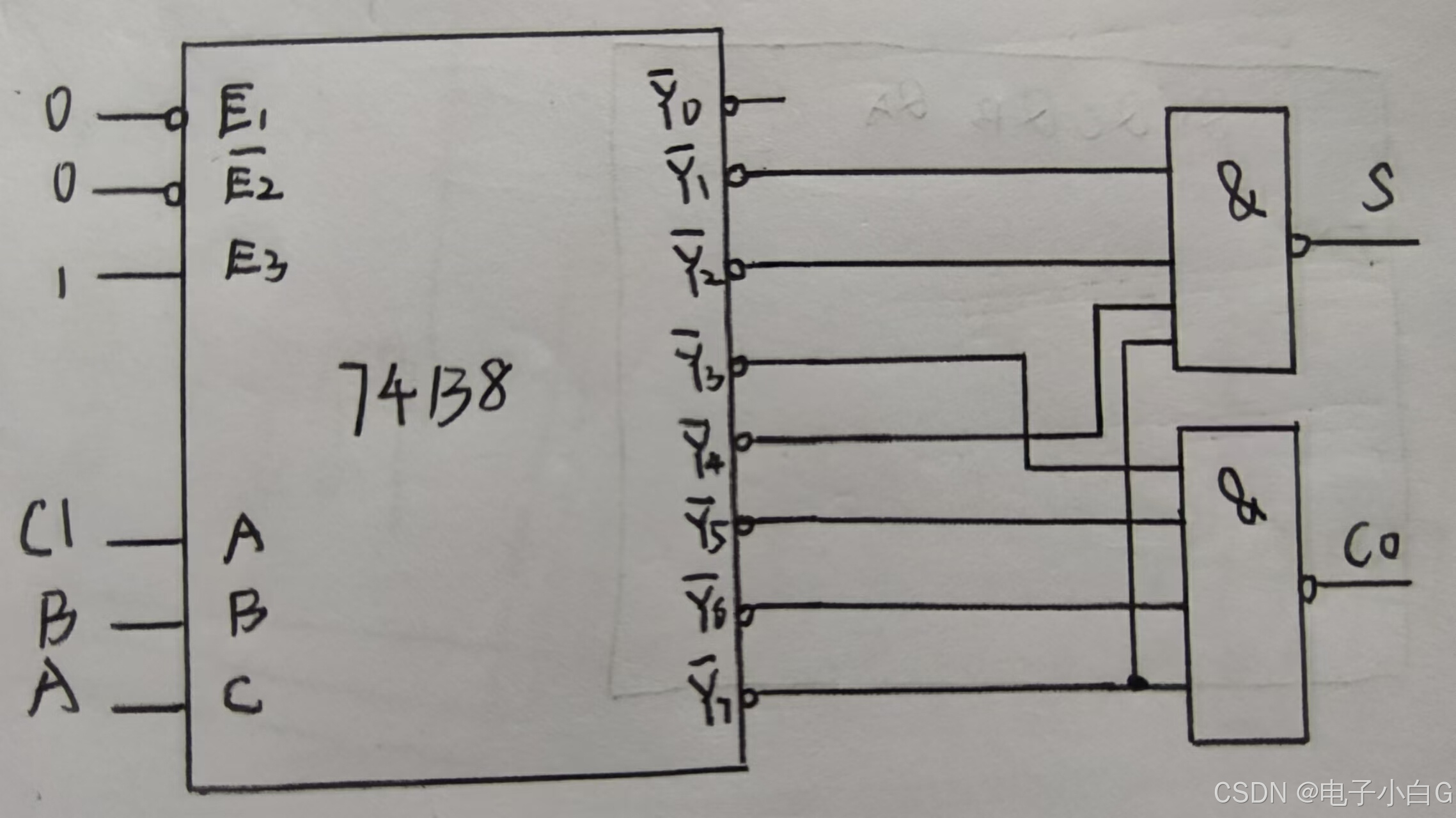

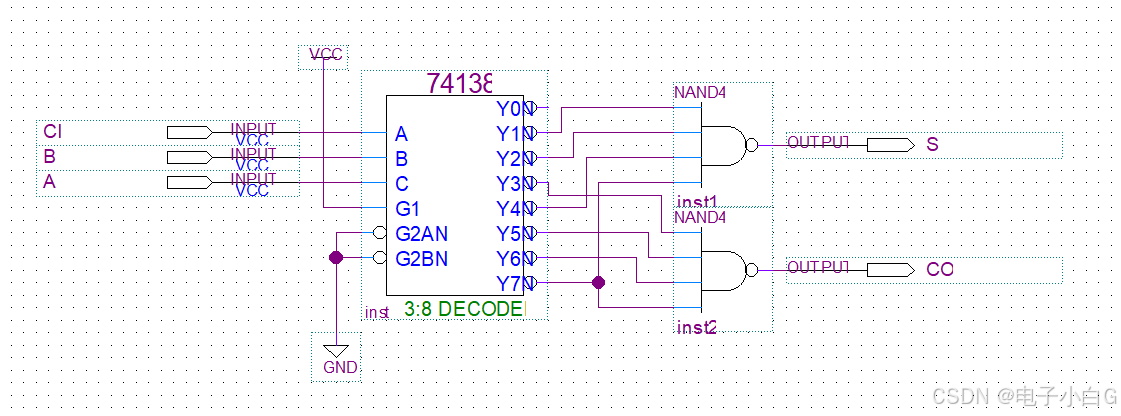

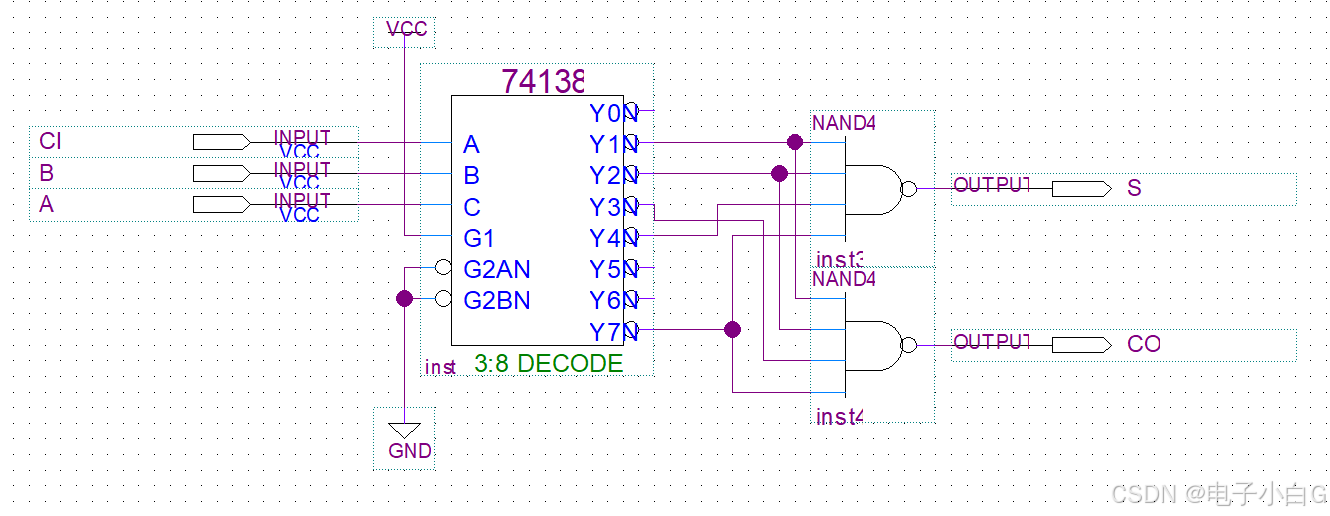

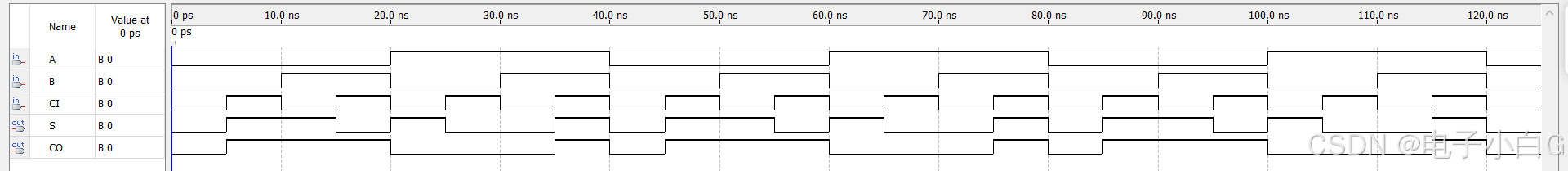

6、应用74138和必要的门电路设计一个1位全加器电路(变量自己合理设置)。

功能图:

A-加数;B-加数;CI-低位进位输入;S-和;CO-向高位进位输出

| A | B | CI | S | CO |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

电路图:

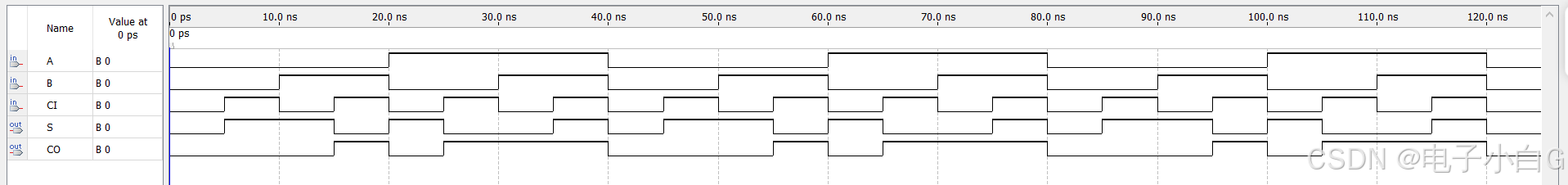

仿真结果:

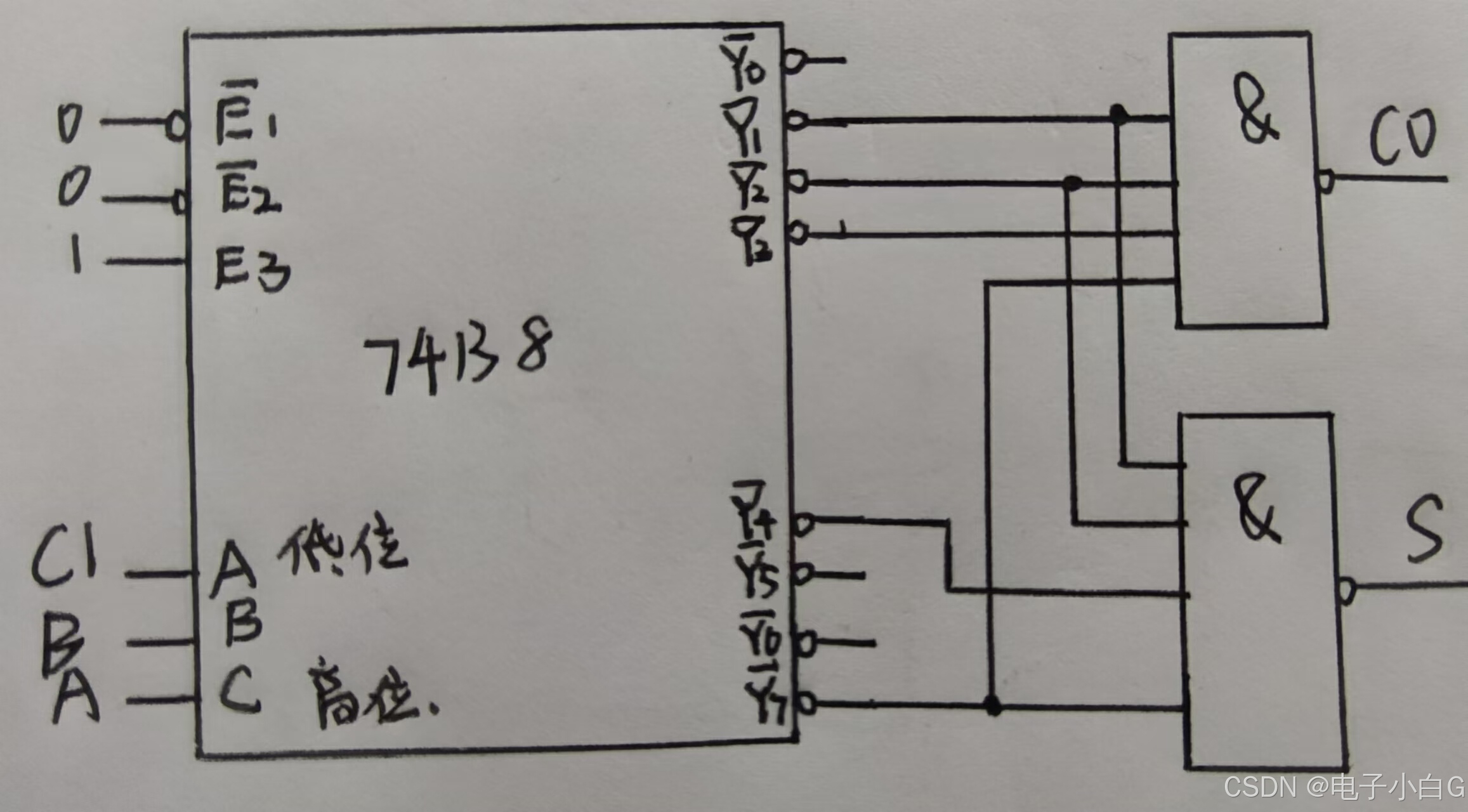

7、应用74138和必要的门电路设计一个1位全减器电路((变量自己合理设置)。

功能图:

A-被减数;B-减数;CI-低位借位输入;S-差;CO-向高位借位输出

| A | B | CI | S | CO |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

电路图:

仿真结果:

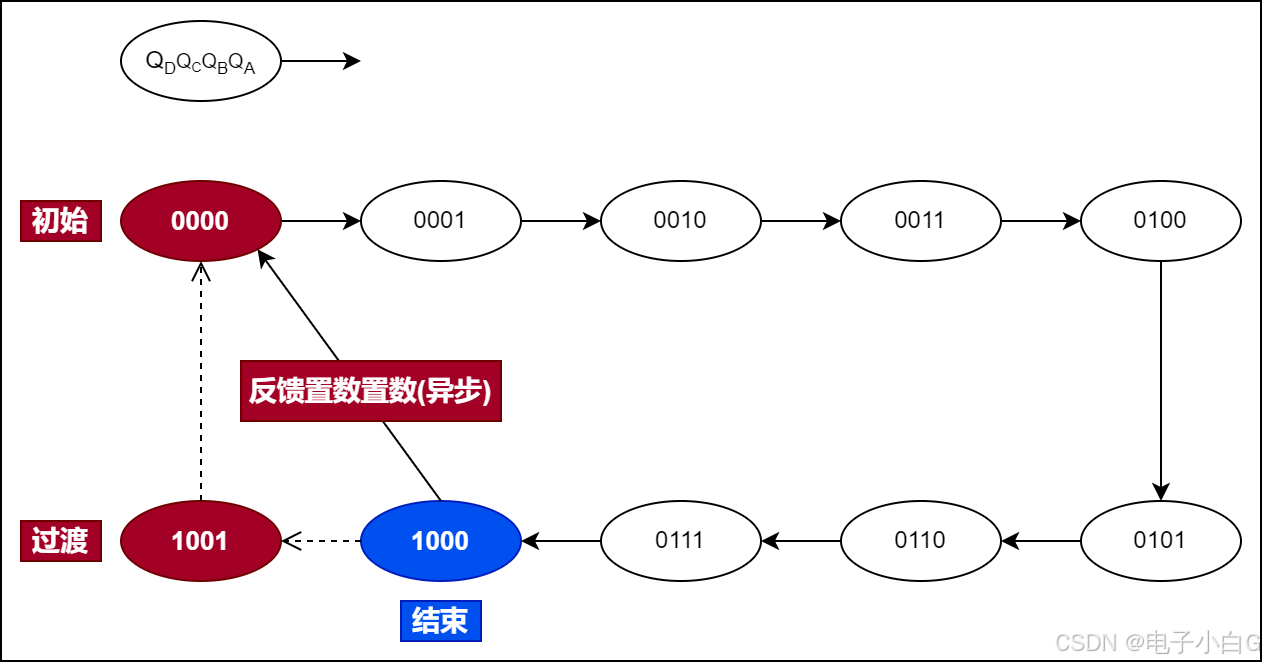

8、应用74192设计实现九进制加法计数器。

状态图:

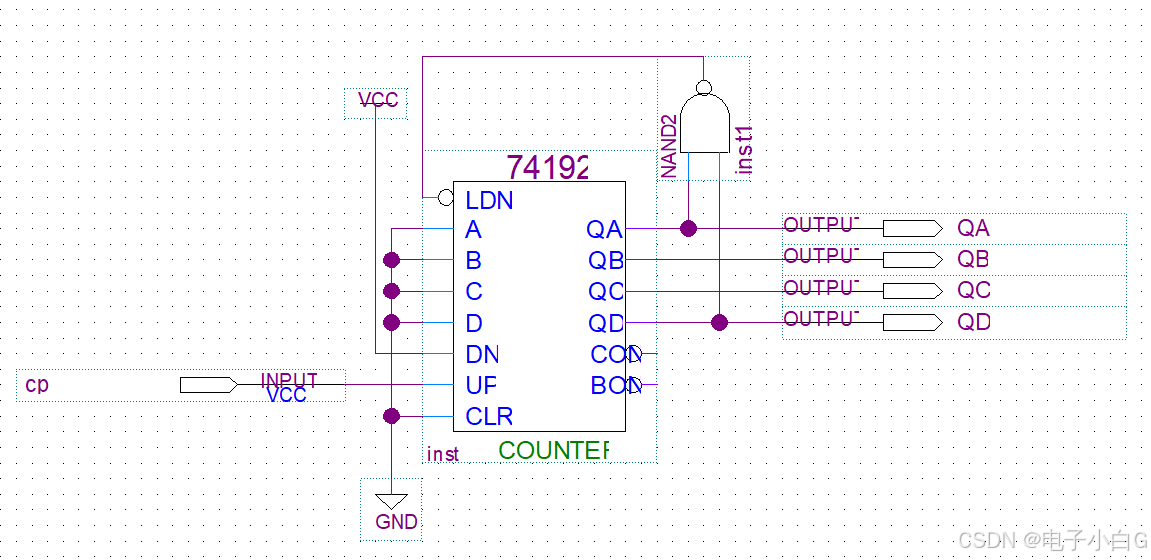

电路图:

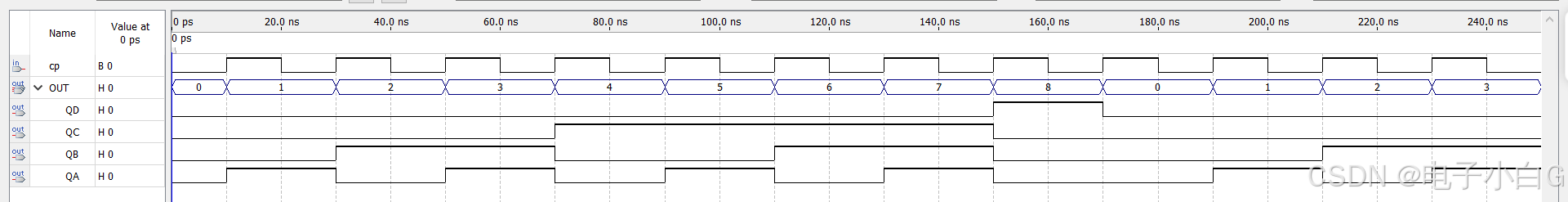

仿真结果:

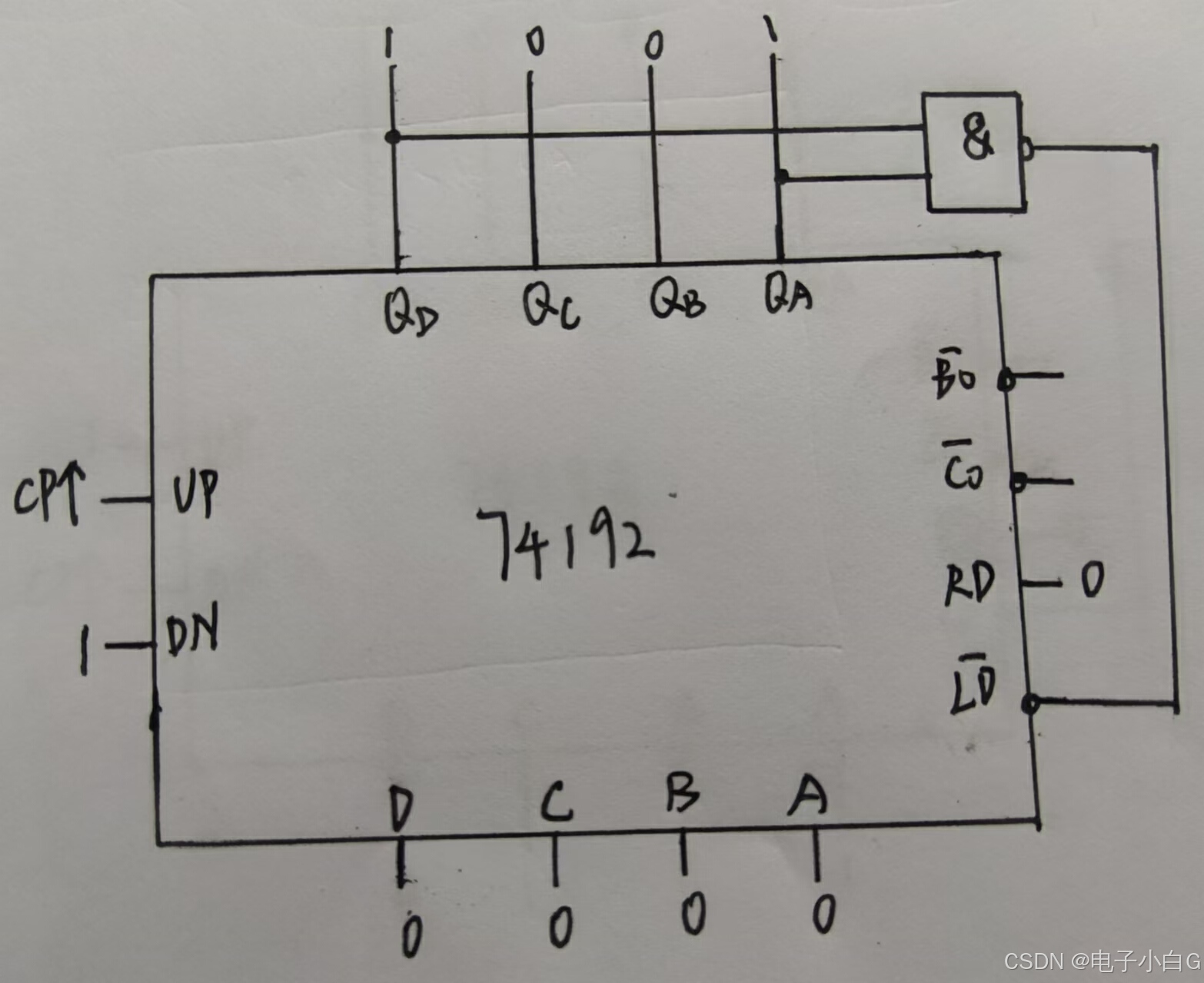

9、应用74192设计实现八进制减法计数器。

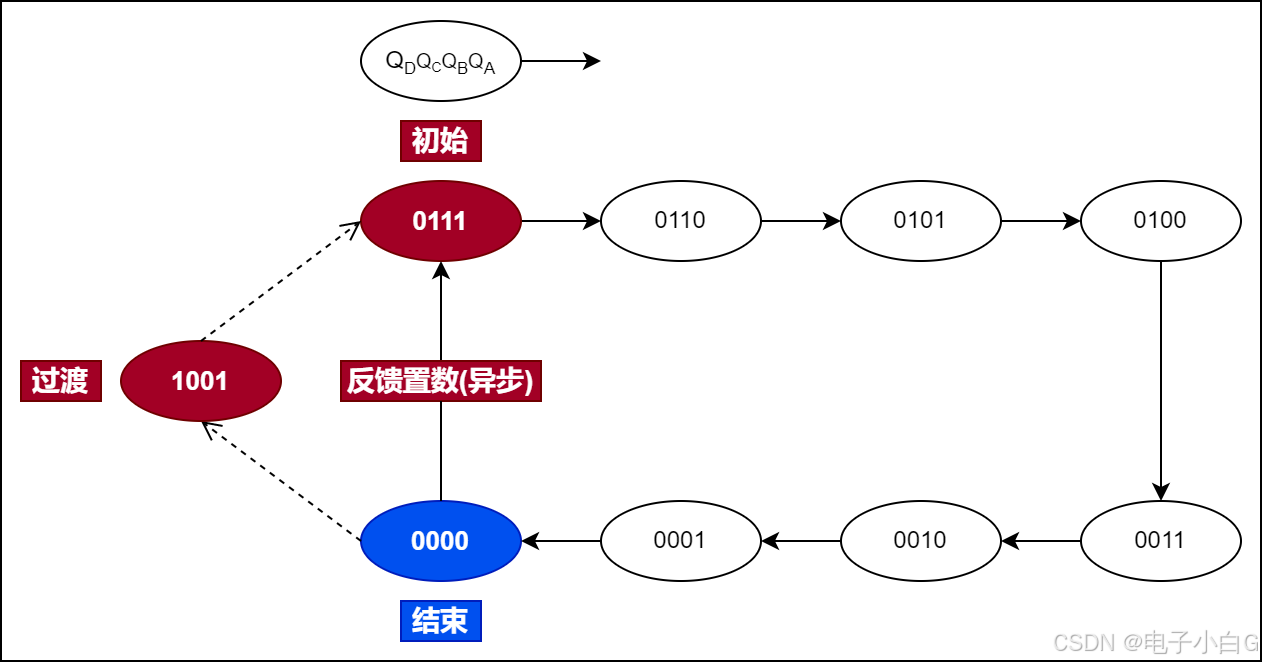

状态图:

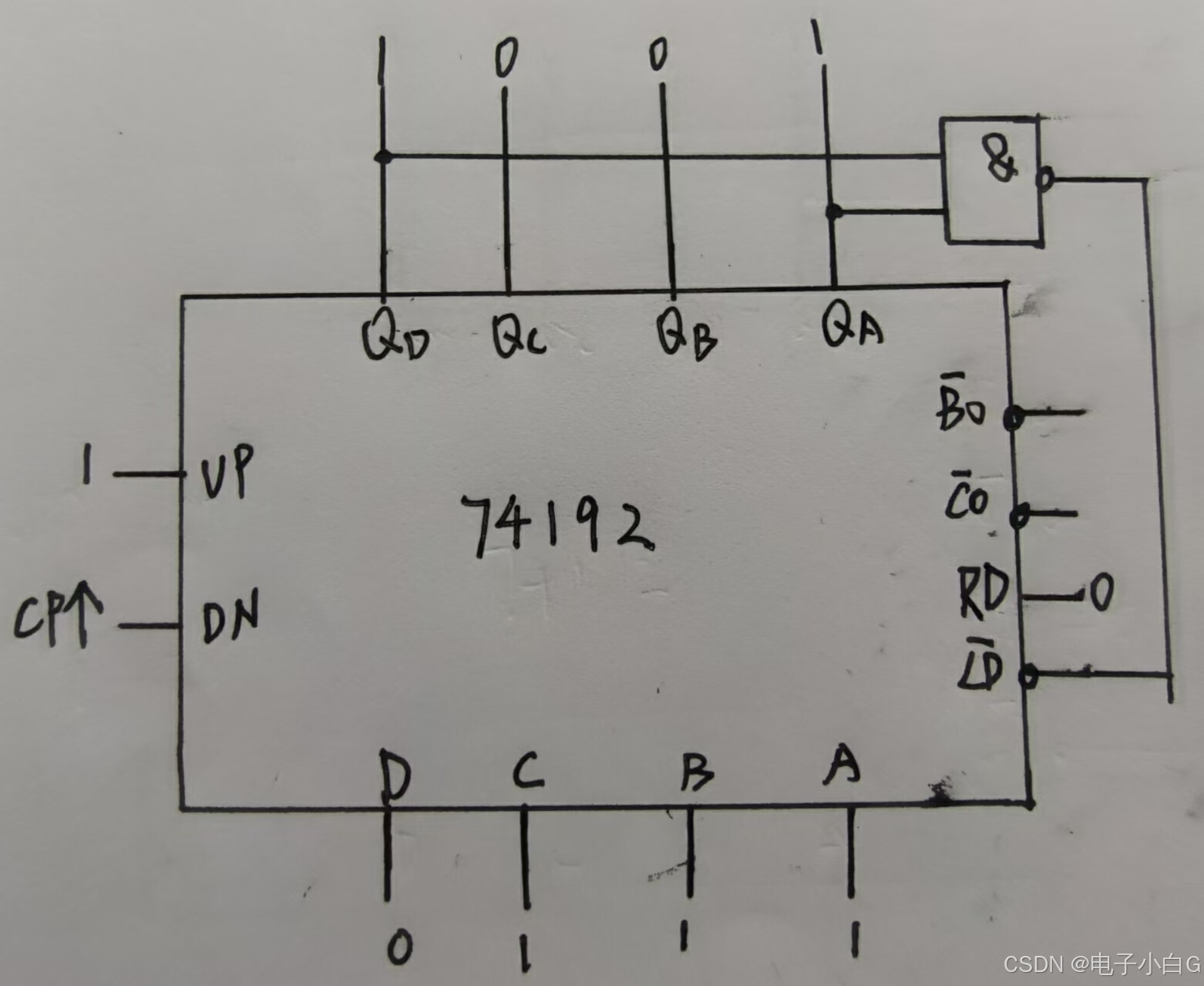

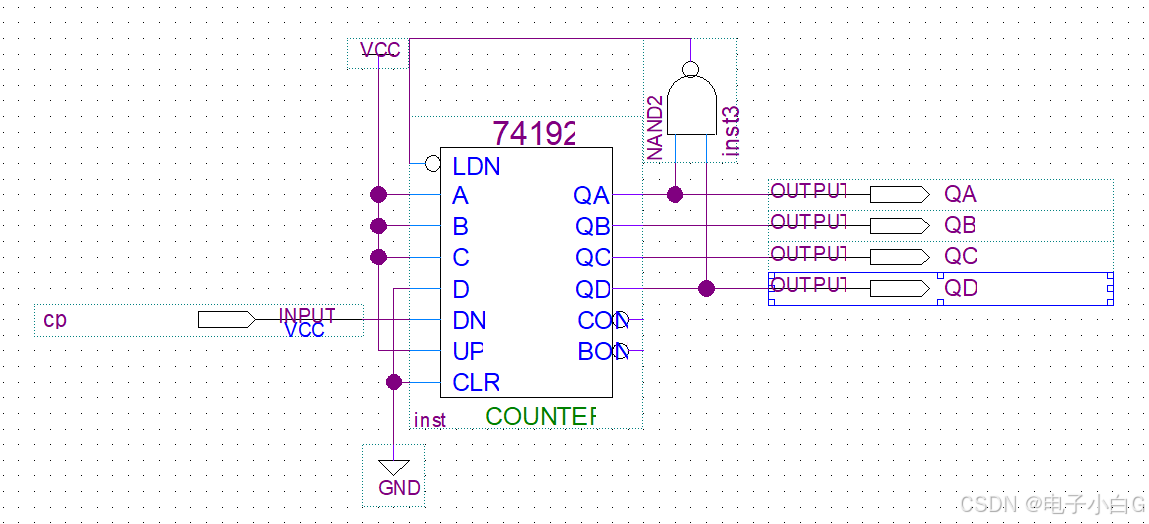

电路图:

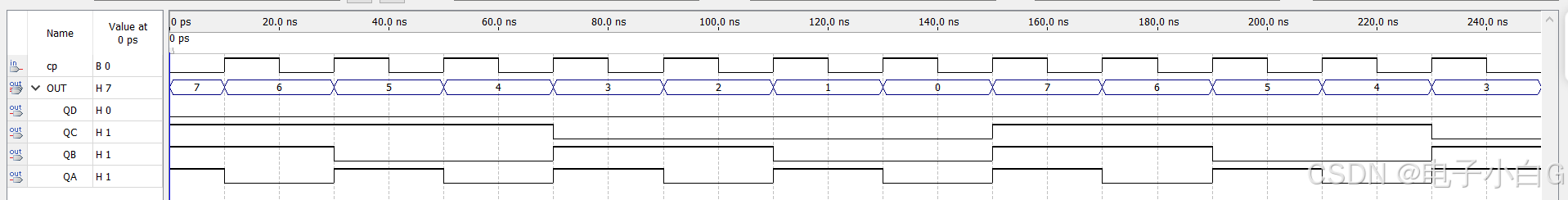

仿真结果:

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?