全部学习汇总: GreyZhang/g_TC275: happy hacking for TC275! (github.com)

这个章节看的信息应该是针对内核设计实现上TC275的具体实现特点,应该是覆盖了很多内核中的实施相关的特性的。

1. 在上下文功能支持上,P和更灵活一些。E核只支持DSPR存储CSA。不过,在DSPR存储CSA应该是最好的方案,不管是P核还是E核,在这个存储块存储CSA效率都是最高的。

2. 对于PC寄存器的写入,只有在CPU停止的时候才能够执行。

1. 总线有一个缓冲机制,主要是为了提升性能。

2. 缓冲一般来说对于用户是不可见的,但是可以通过DSYNC来进行同步,写入到存储。

3. P核有6级缓冲,而E和有2级缓冲。

4. 这个缓冲机制是可以关闭的,通常来说不能这么做。否则,性能会严重受损。

1. 这里的中断系统没有提到DMA,是因为在这个MCU上没有这样的实施吗?

2. P/E CPU都实现了一个快速中断机制,可以在特定的场景之下避免不要的上下文切换。

这里出现了熟悉的DSE,如果访问的地址不存在其实是可以触发这个trap的。

1. 这个TIN4对应的信息可能是违反了MPU的保护机制之后触发的。

2. 关于存储完整性相关介绍,内核手册中介绍的非常少。

3. P CPU按照64bits来检查,而E CPU按照32bits来检查。

当时看内核手册的时候,一直好奇是不是这样的保护机制就是ECC。当时,猜测了一个结论,至少ECC会是一种实现方式。现在看来,在TC275上这个机制就是ECC。

这里有一个很值得关注的信息:RAM的初始化其实是可以通过PMU来实现的。

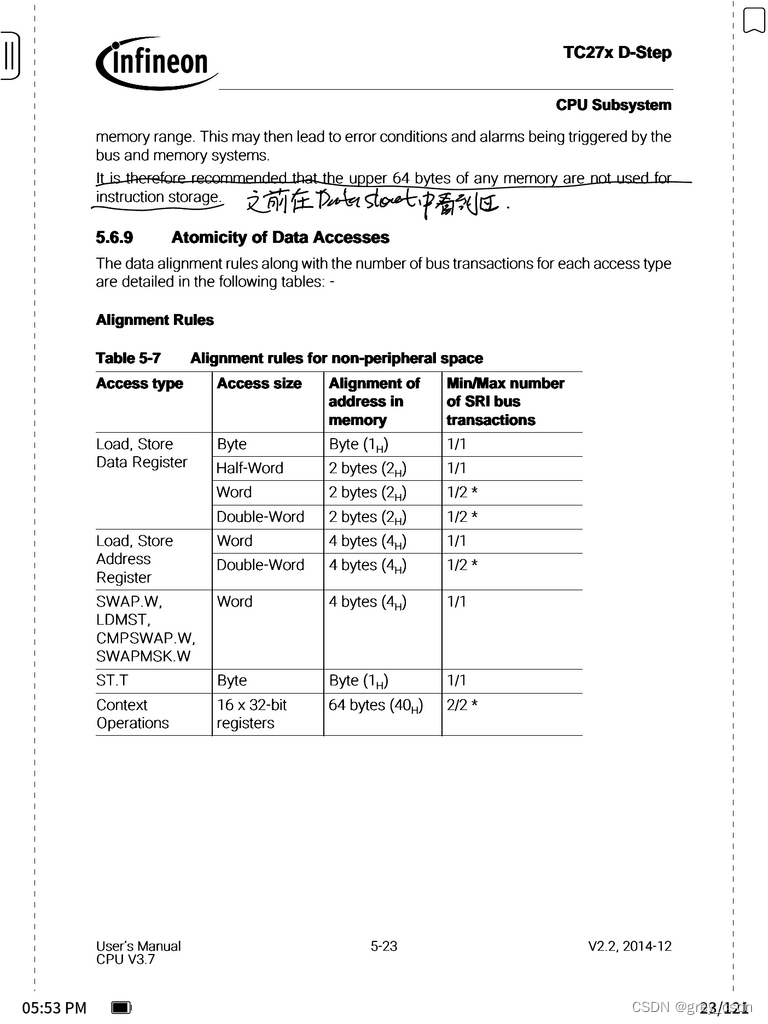

之前在DateSheet中看到的一个提示,在这里再次看到了。当时还以为是文档编排有问题,RM手册中没有写。现在看来,算是特殊考虑两个文档其实都有。

1. 上面的这些指令同步等相关的功能,看上去实现角度太细腻了。一般的软件设计,可能并不会关注到这么细的粒度。

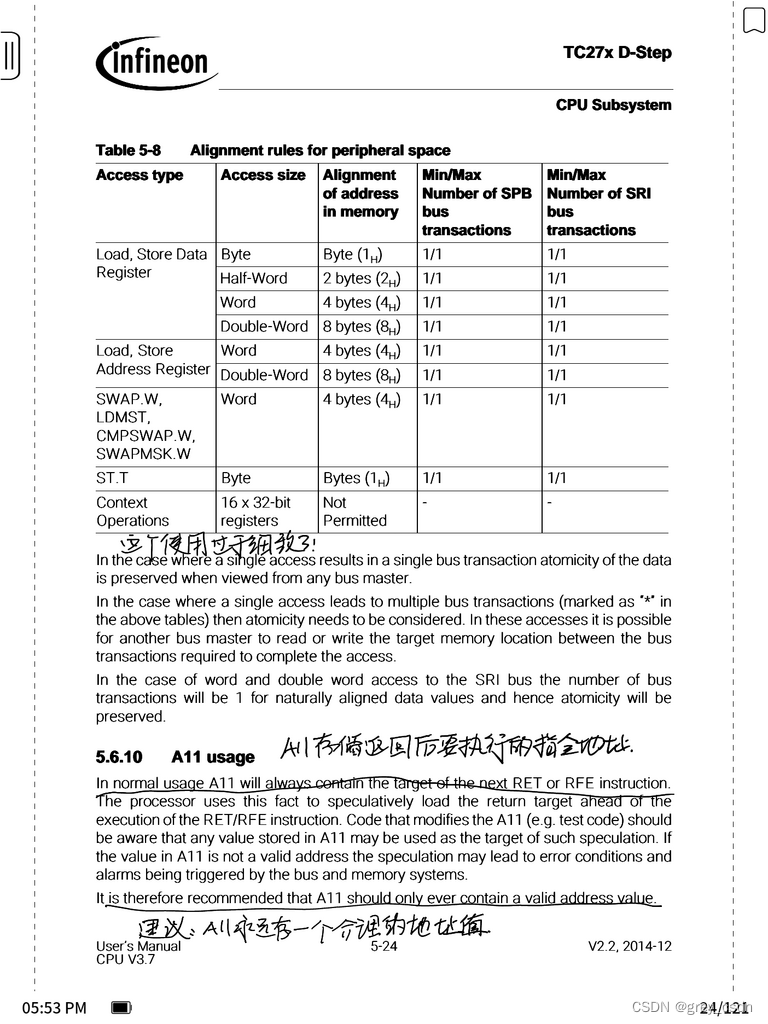

2. A11寄存器存储的是几种返回之后接下来要执行的一条指令的存储地址。建议不管什么时候,A11永远存储一个合理的地址数值。

这样,TC275在CPU内核设计上的实现特性基本就看完了。

705

705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?