全部学习汇总: GreyZhang/g_TC275: happy hacking for TC275! (github.com)

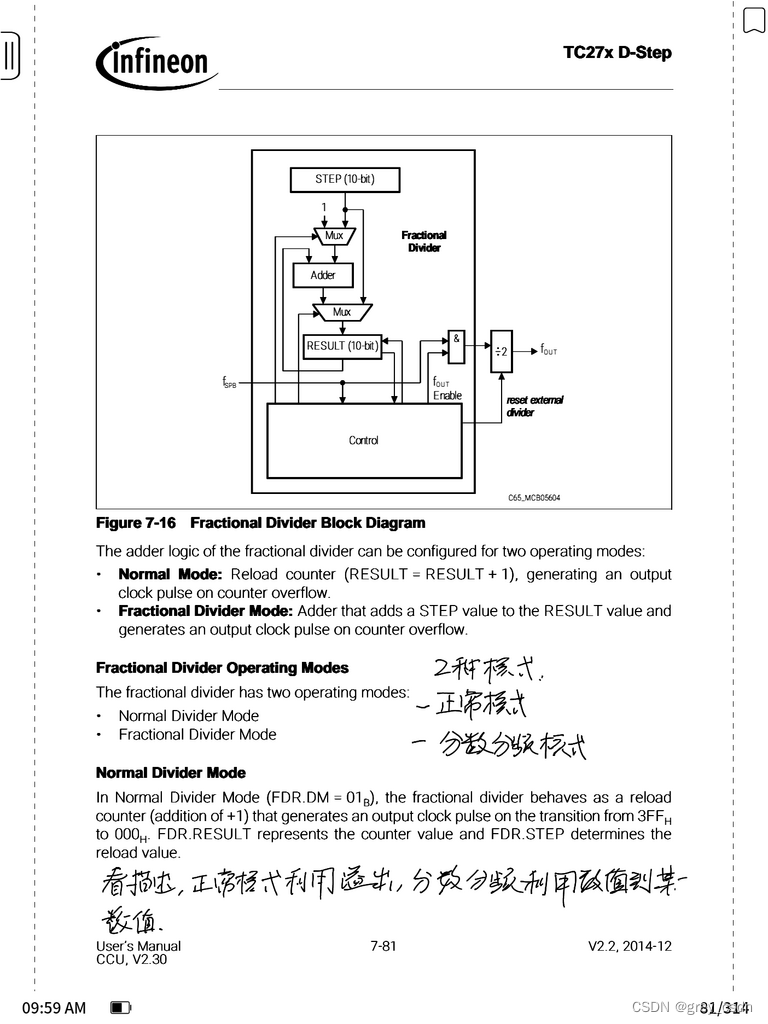

1. 外部时钟的生成有两种模式:正常模式以及分数分频模式。

2. 看描述,正常模式利用了溢出实现,而分数分频其实是利用步长进行了信号产生的判断。

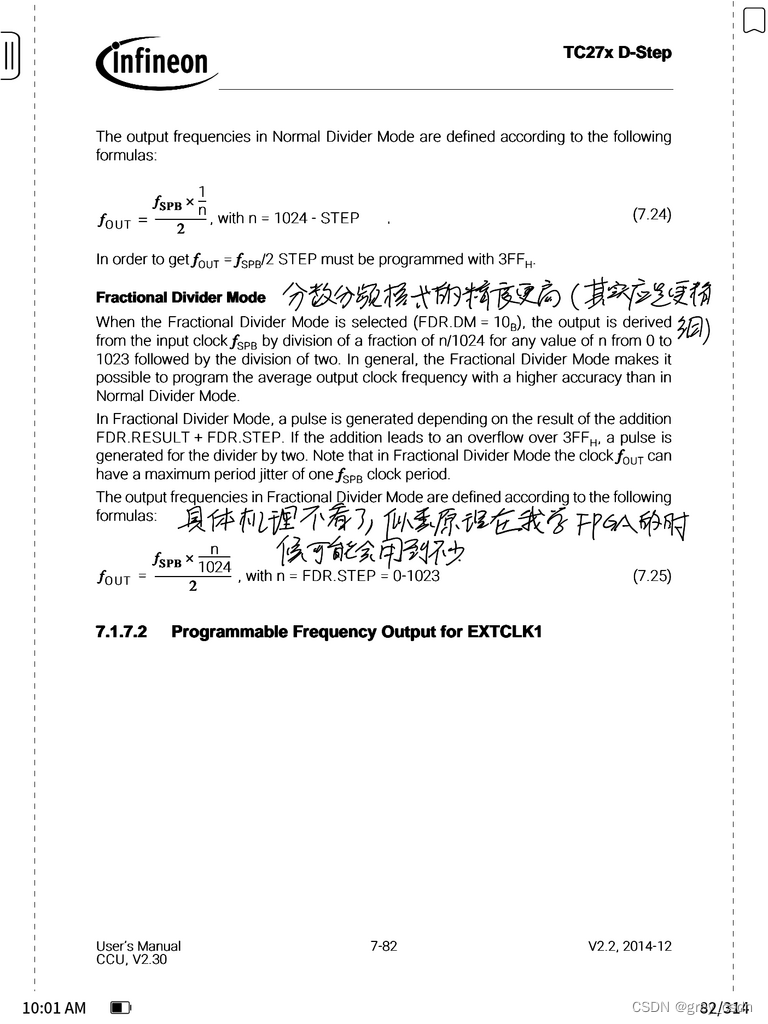

1. 分数分频模式的精度更高,这里的精度更高我觉得可以从另一个角度来考虑,其实是他的控制更加灵活。

2. 关于逻辑实现上,不去仔细看了。接下来我还会专门找时间学习FPGA,我觉得在学习FPGA的时候这样的原理会接触不少。

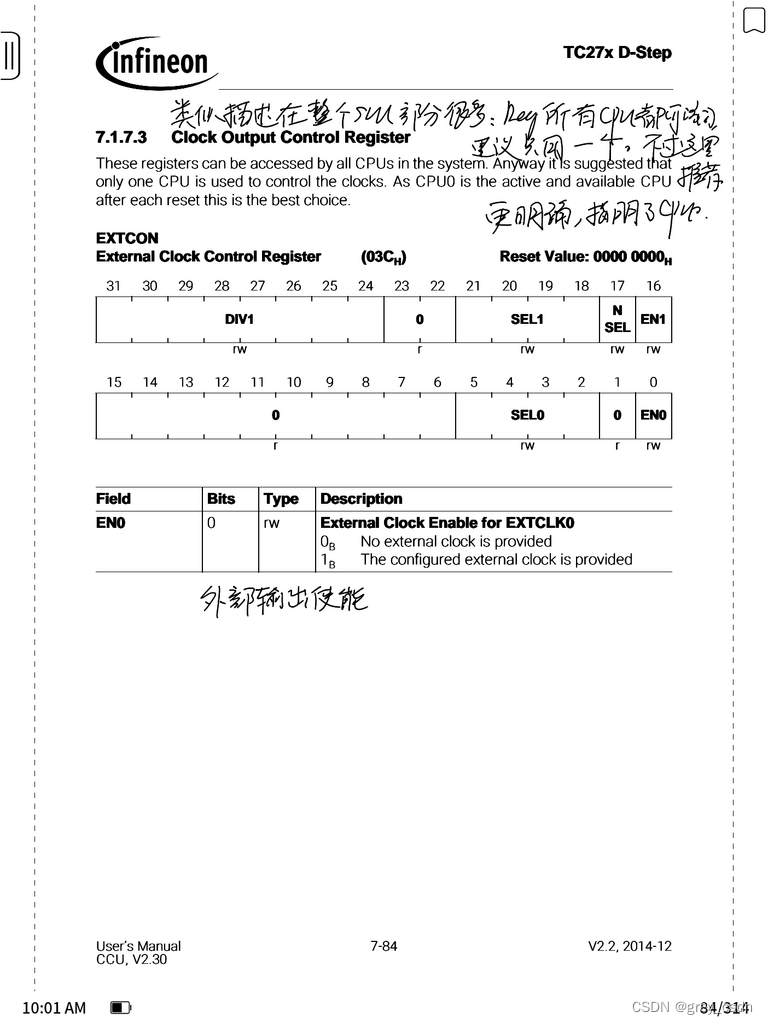

关于寄存器的相关描述看起来在SCU模块算是一个模板形式的描述,都是类似的。全都是寄存器可以让所有的CPU访问处理,但是建议只由一个来处理。不过,相比其他的地方这里的建议更加明确了一些,直接建议了CPU0。

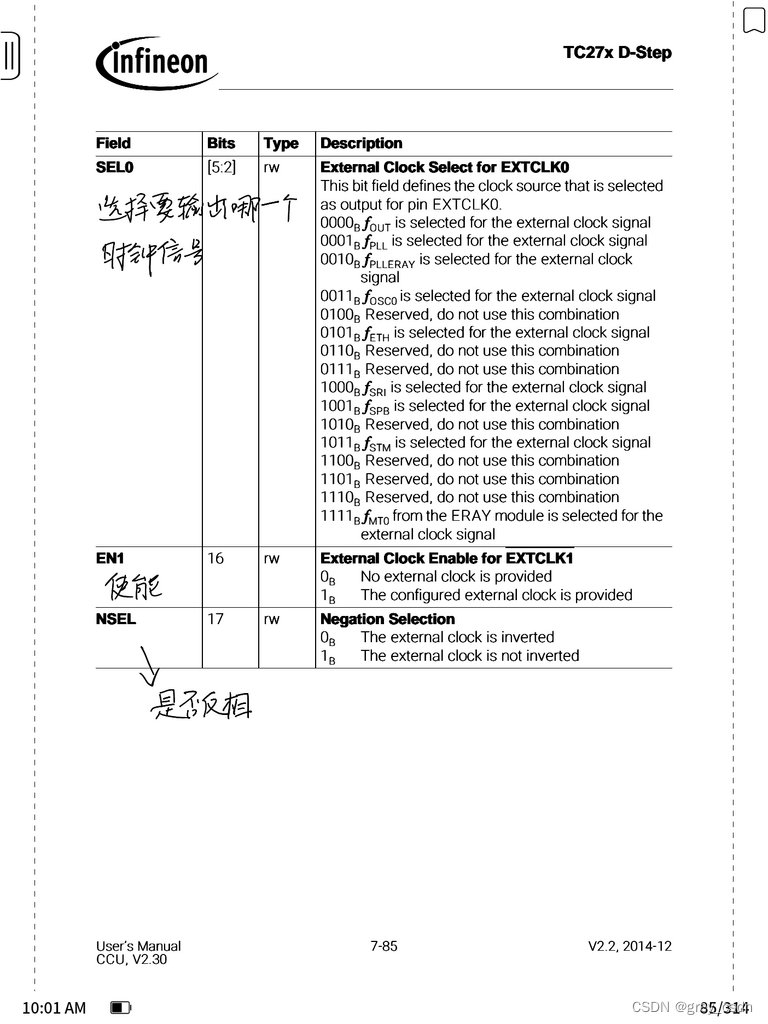

1. 整个时钟系统中的时钟信号有很多个,究竟要输出哪一个其实是可以设置的。

2. 另外,输出还有使能以及反相等控制。

1. 外部的时钟输出一共可以输出2个,第二个看起来带有分频的配置,输出更加灵活。

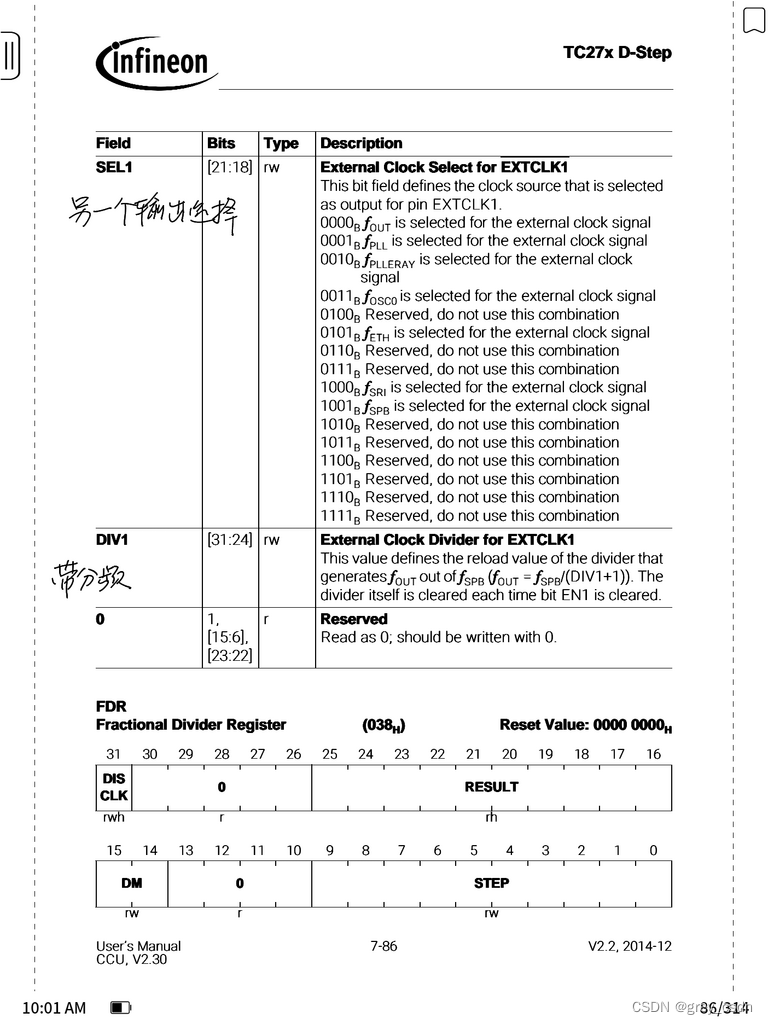

这里的寄存器相关的配置涉及到步长控制、模式选择以及使能的选择。

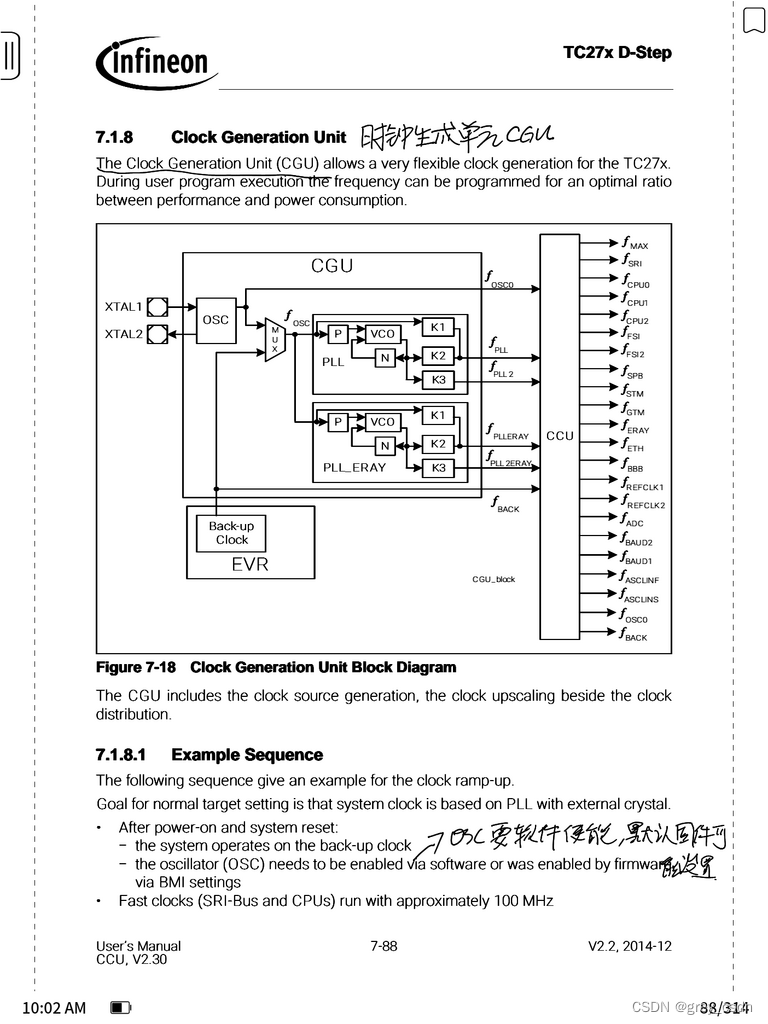

1. 时钟生成模块,简称是CGU。灵活的配置可以让用户在性能以及功耗之间找到比较好的平衡。

2. OSC的使能需要软件处理,或者可能默认开启动作在固件中实现了。看到这里,基本明白了为什么有些板子没有程序的时候晶振就已经有了信号。

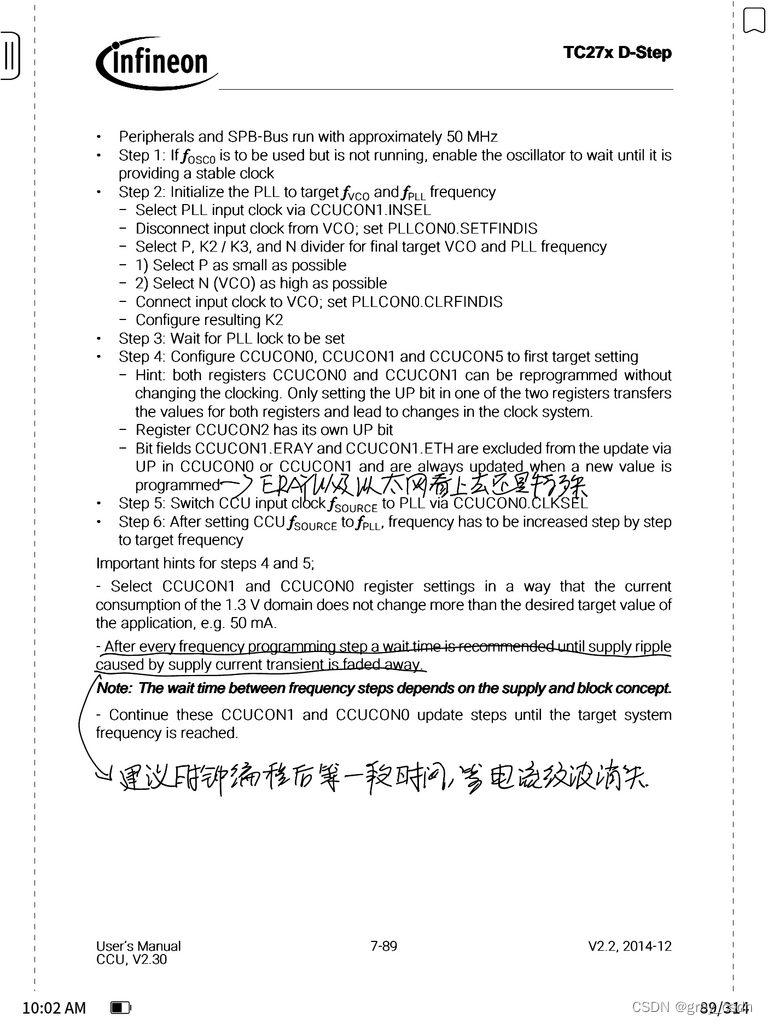

1. 从给出来的例子看,ERAY以及ETH的时钟是比较特殊的。

2. 时钟编程后建议稍微等一点时间,等待电流纹波消失。由此可知,这个过程中其实涉及到电源功耗的波动。

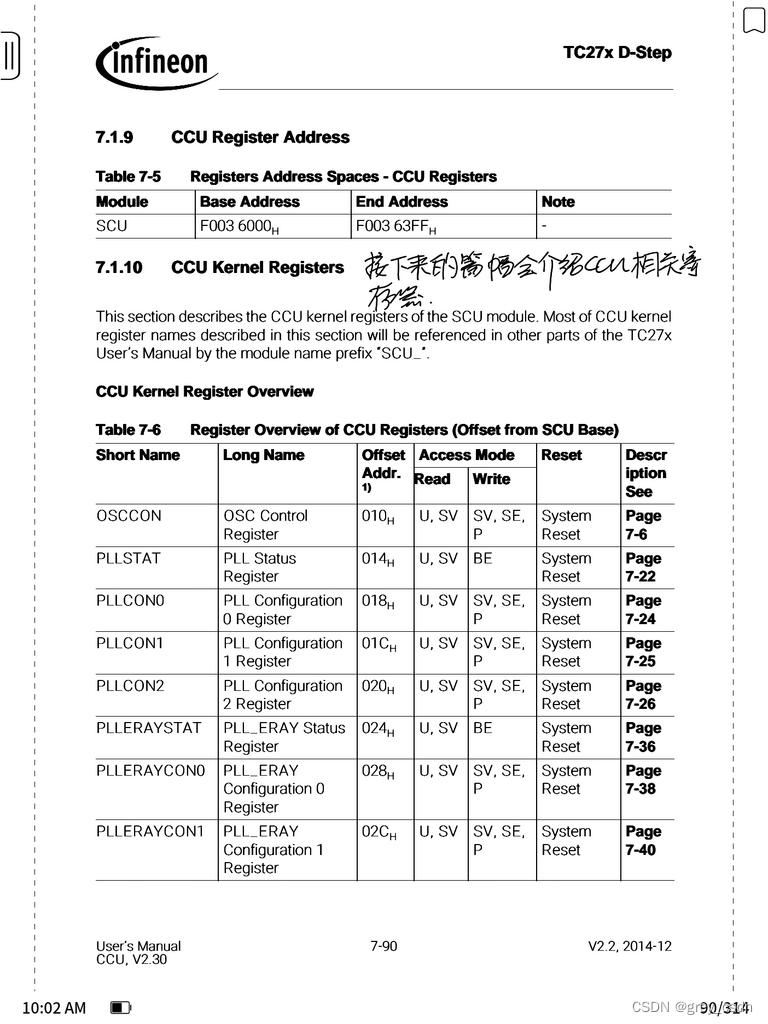

继续往下应该是CCU内核相关寄存器的介绍了,这一次的学习来不及看了。下一次针对性做一个学习小结。

2764

2764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?