JESD204接口调试总结——Xilinx JESD204C IP工程应用

JESD204C上板调试,我直接跳过了看它的example的过程,因为example blockdesign设计的内容比较多,看起来麻烦。因为我已经有了JESD204B调试的经验,那么JESD204C我依葫芦画瓢,直接把一些重点线连接起来,做一个有收有发的顶层模块后在通过收发回环来进行仿真

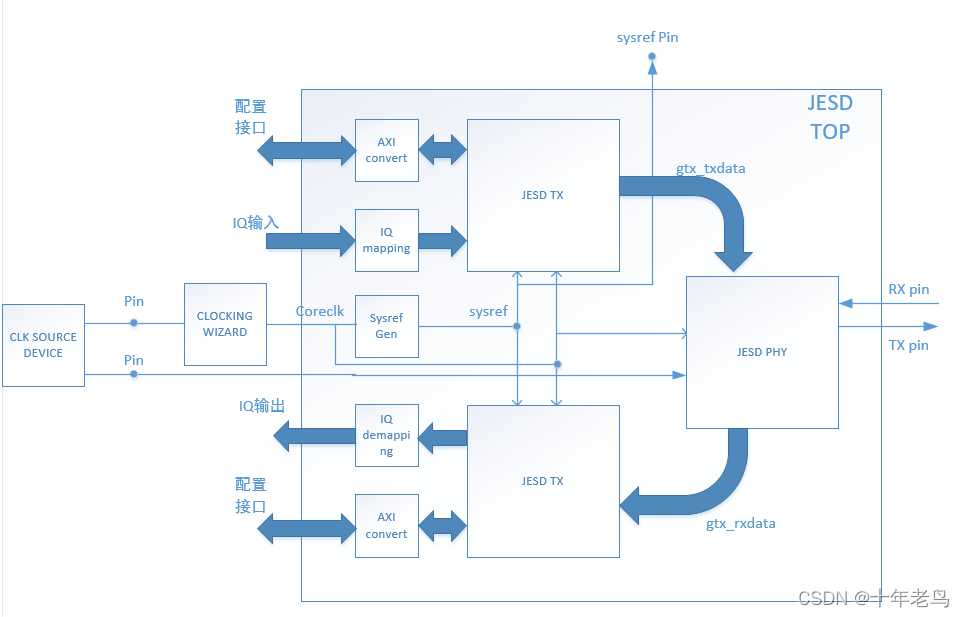

很明显,作为一个ADC和DAC接口,我们需要构建一个顶层模块

1、 IQ输入,作为DAC的数据源

2、 IQ输出,作为ADC采集的数据

3、 AXI总线,用于对IP核的配置

4、 几个复位线,对phy 和axi进行复位用

5、 时钟

6、 与FPGA外部JESD器件接口 【高速接口管脚/SYSREF/参考时钟/】

JESD204B:4T4R 4lane采样率 245.76Mbps 9.8304G的速率

JESD204C:4T4R 4lane采样率 245.76Mbps 8.11008G的速率

采用204C,serdes可以使用更低的速率来实现和204B一样数据量的传输。

JESD CORE 数据的位宽为32bit,正好一个lane覆盖一个 {I,Q}

</

</

本文介绍了在FPGA中使用Xilinx JESD204C IP进行接口调试的经验,包括如何构建顶层模块、设置IQ输入输出、AXI总线配置、复位线、时钟及高速接口。着重讨论了JESD204B与JESD204C的区别,例如204C能以更低的速率实现相同数据量的传输。还提到了AXI转换、IQ映射、SYSREF生成以及PHY核的配置,如回环测试、预加重参数调整,并提供了调试过程中的关键步骤和寄存器操作。

本文介绍了在FPGA中使用Xilinx JESD204C IP进行接口调试的经验,包括如何构建顶层模块、设置IQ输入输出、AXI总线配置、复位线、时钟及高速接口。着重讨论了JESD204B与JESD204C的区别,例如204C能以更低的速率实现相同数据量的传输。还提到了AXI转换、IQ映射、SYSREF生成以及PHY核的配置,如回环测试、预加重参数调整,并提供了调试过程中的关键步骤和寄存器操作。

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?