状态机(State Machine,有限状态机,Finite State Machine,FSM)概念:在有限个状态之间按一定规律转换的时序电路,主要于处理串行逻辑。

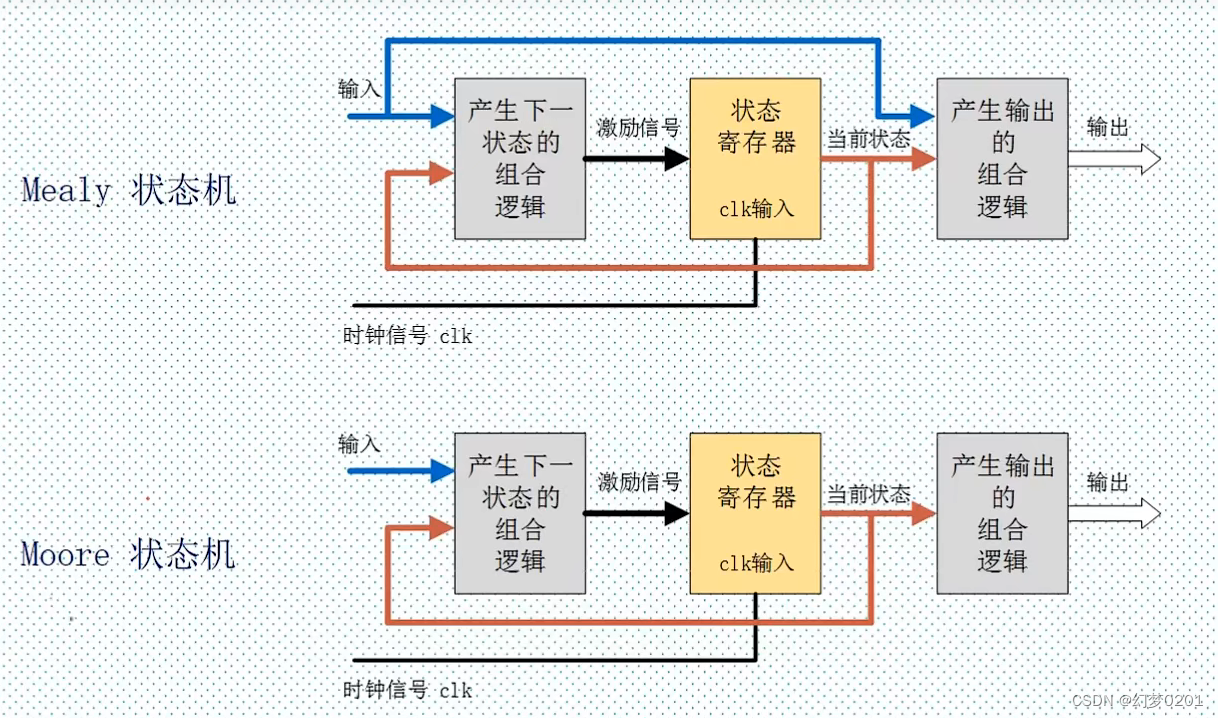

状态机模型:

状态寄存器是由一组触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟clk的跳变沿

状态是否改变、如何改变,取决于组合逻辑F的输出,F是当前状态和输入信号的函数。

状态机的输出是由组合逻辑G提供的。

Mealy状态机的输出与当前状态和输入信号有关,Moore状态机的输出仅与当前状态有关

状态机设计:

1、状态空间定义:为每种状态进行编码;

2、状态跳转(时序逻辑);

3、下个状态的判断(组合逻辑);

4、各个状态下的动作:

2146

2146

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?