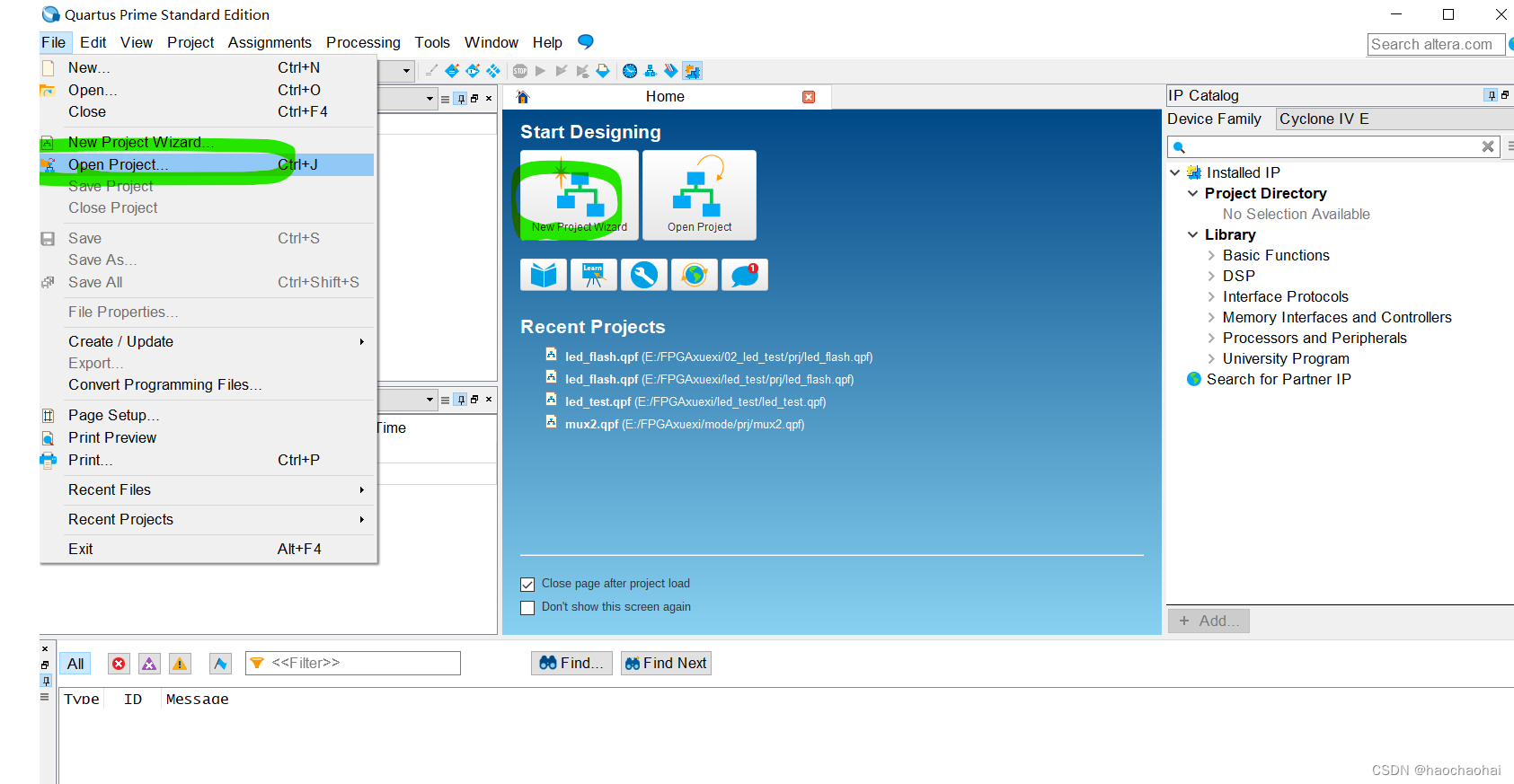

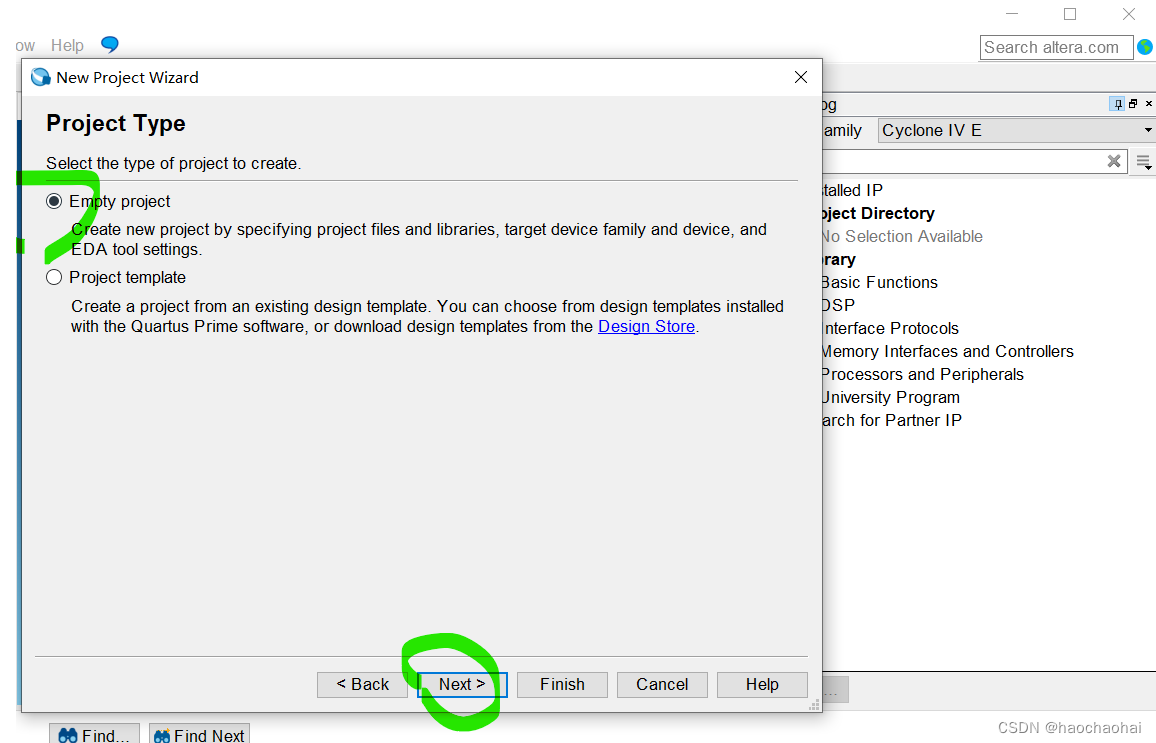

新建工程

选择工程目录

定义工程名称

选择FPGA芯片

选择自带modesim-altera,verilog语言,next

完成

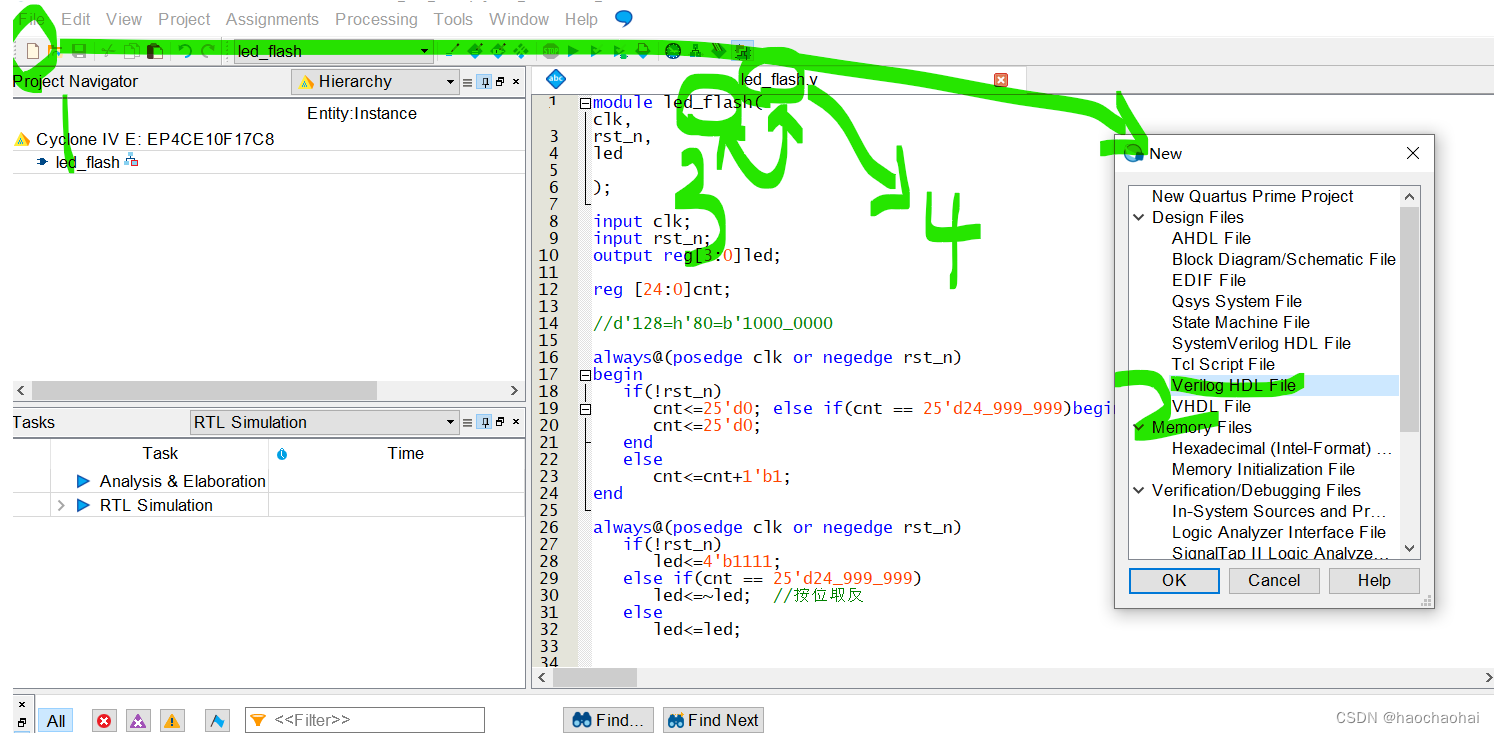

选择verilog文件进行代码编写,将文件名命名为module的模块名,此时顶层文件为该文件

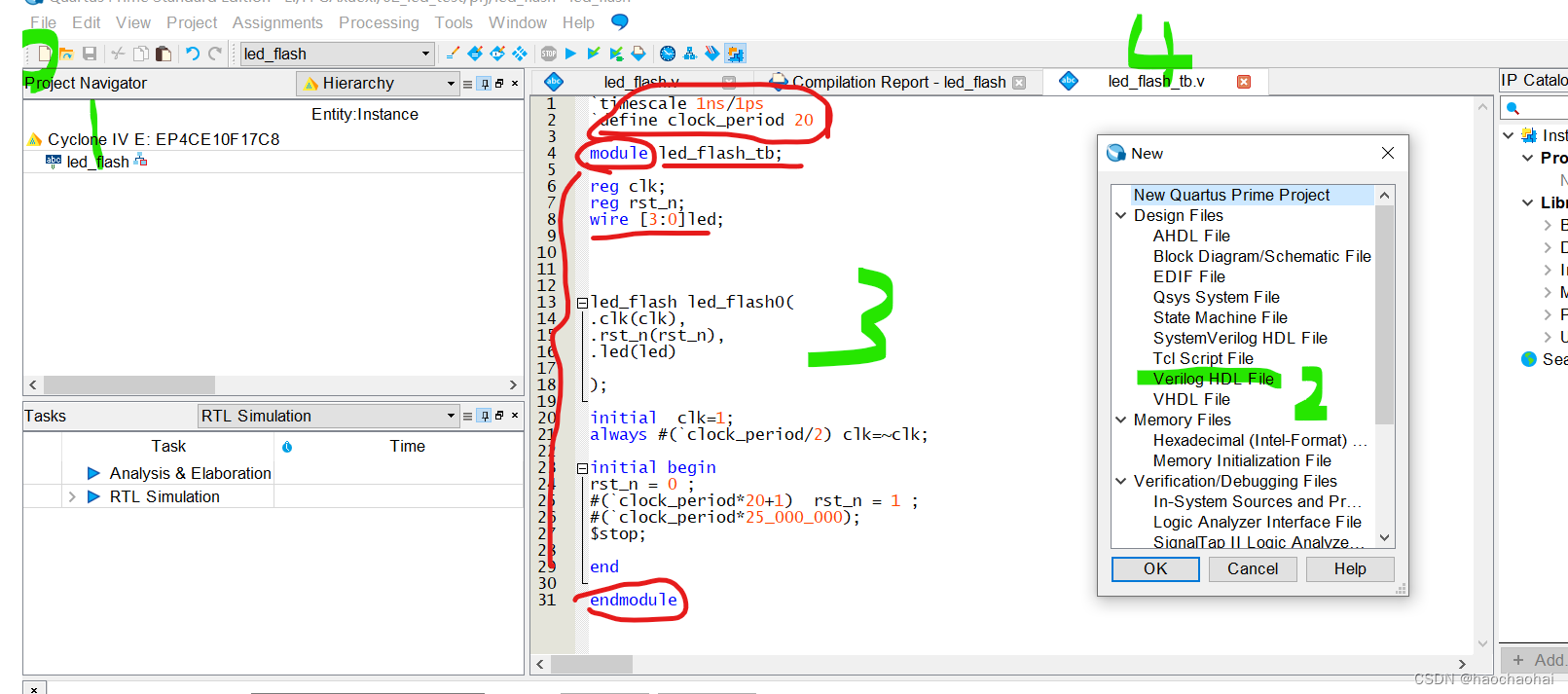

然后编写testbench文件进行modesim测试

testbench文件名字与模块一致,注意程序书写规范,生成时钟方法,延时的使用方法,停止的使用方法,例化方法,端口定义

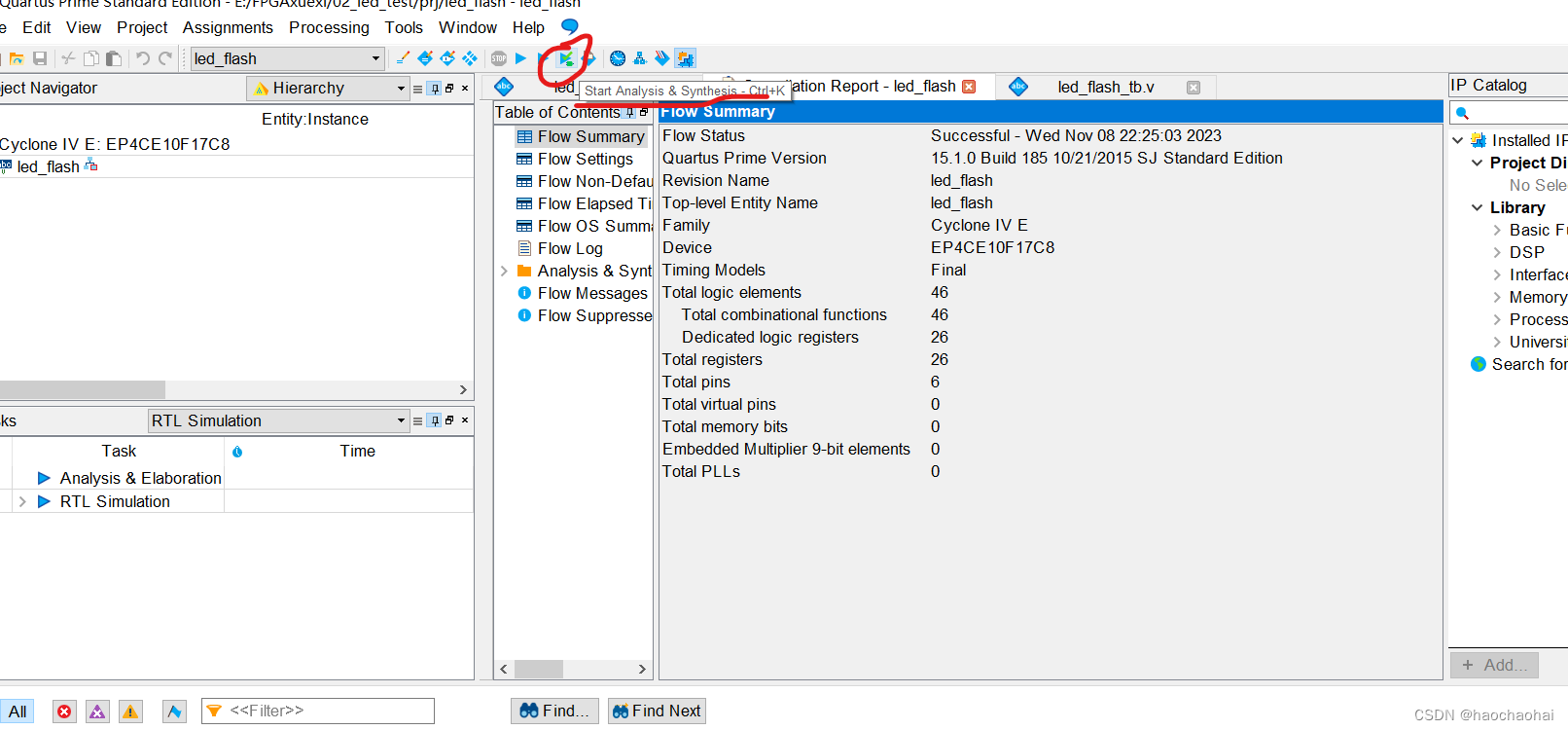

进行分析和综合,没问题

接下来将测试程序导入modesim中

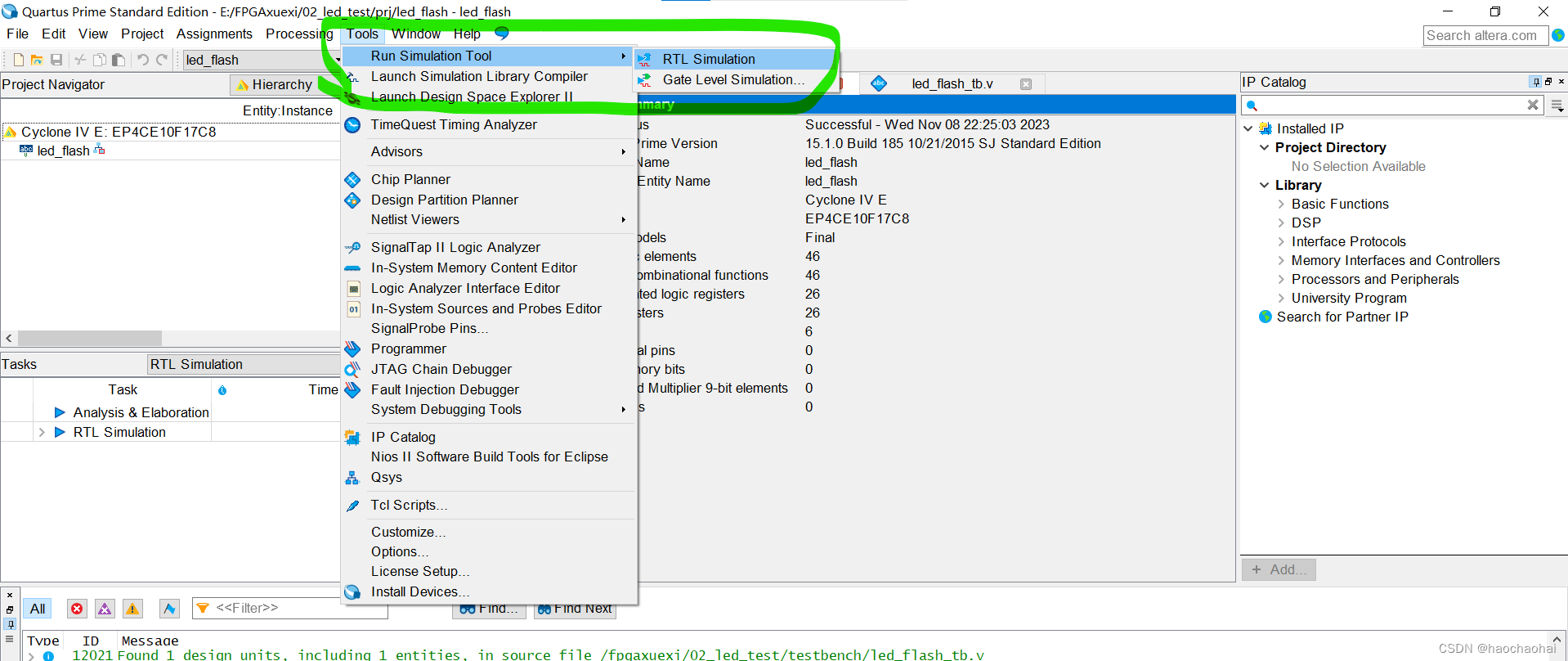

加入testbench文件

应用,ok

RTL仿真

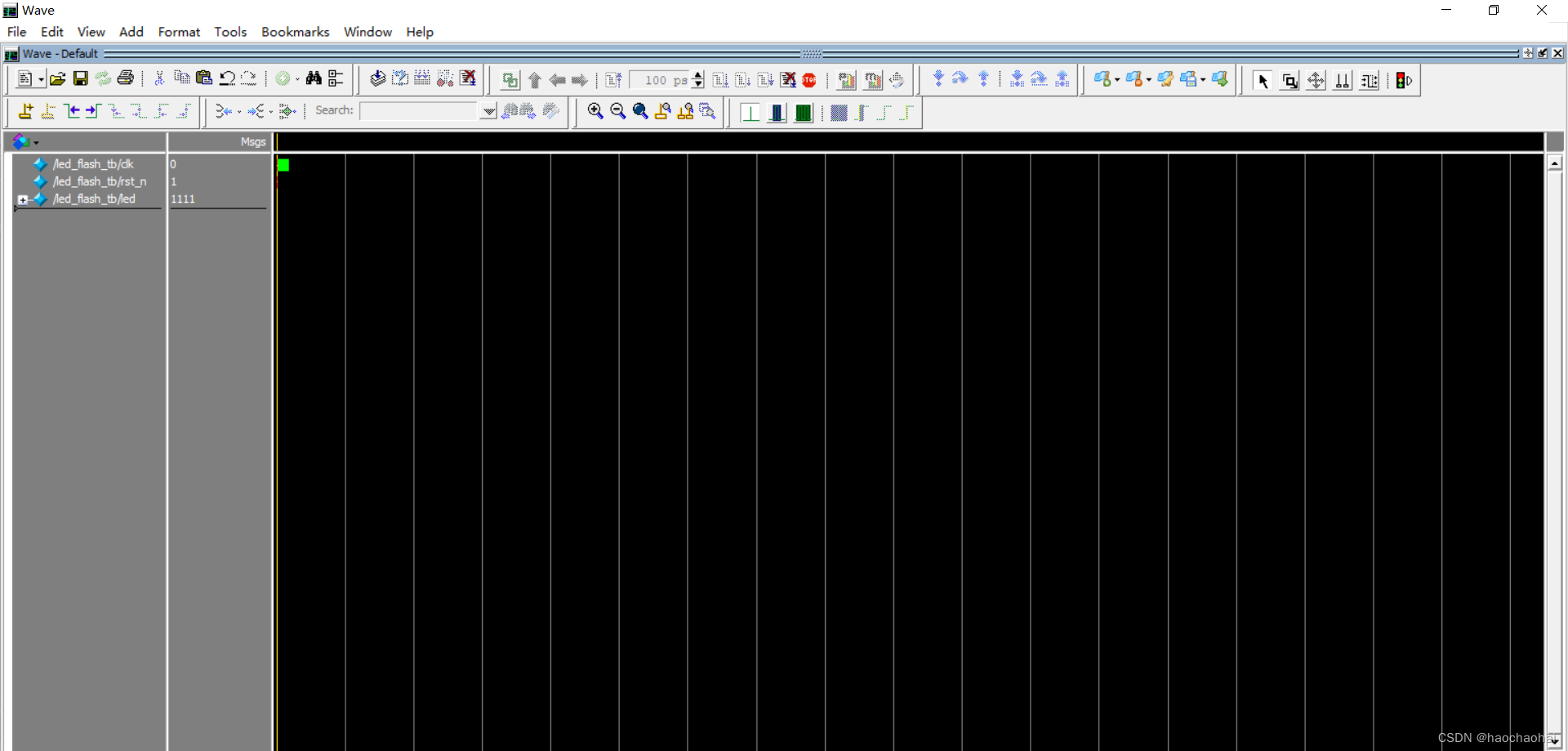

出现仿真波形

ctrl+鼠标左键选择显示范围

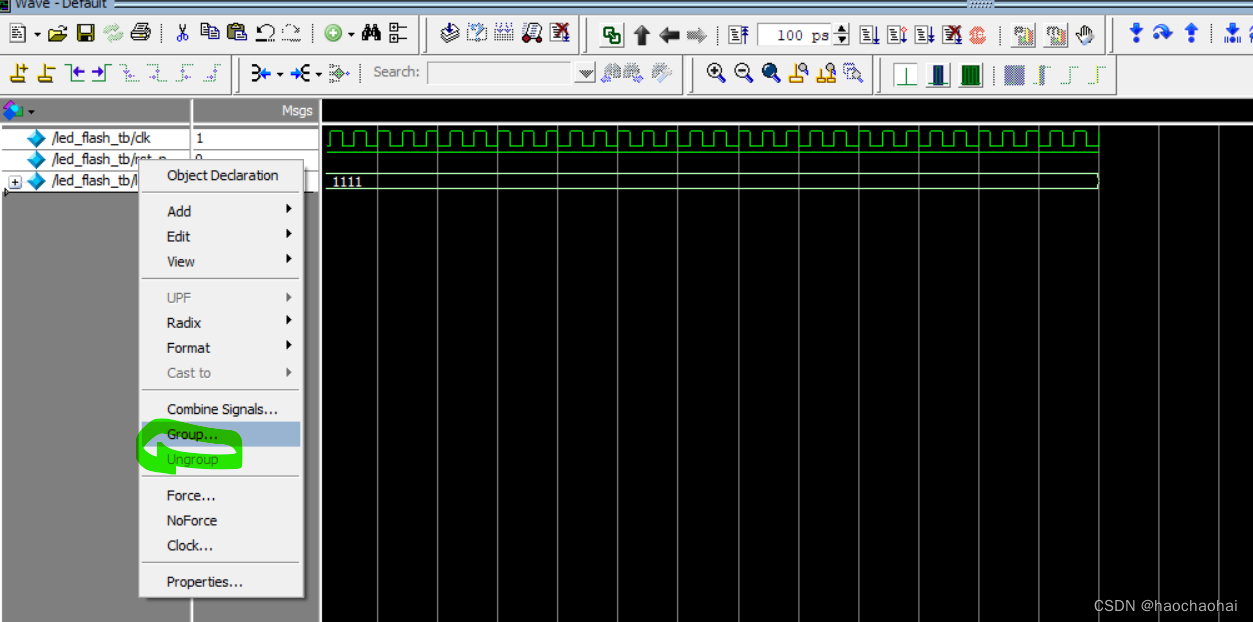

分组的方法

增加光标

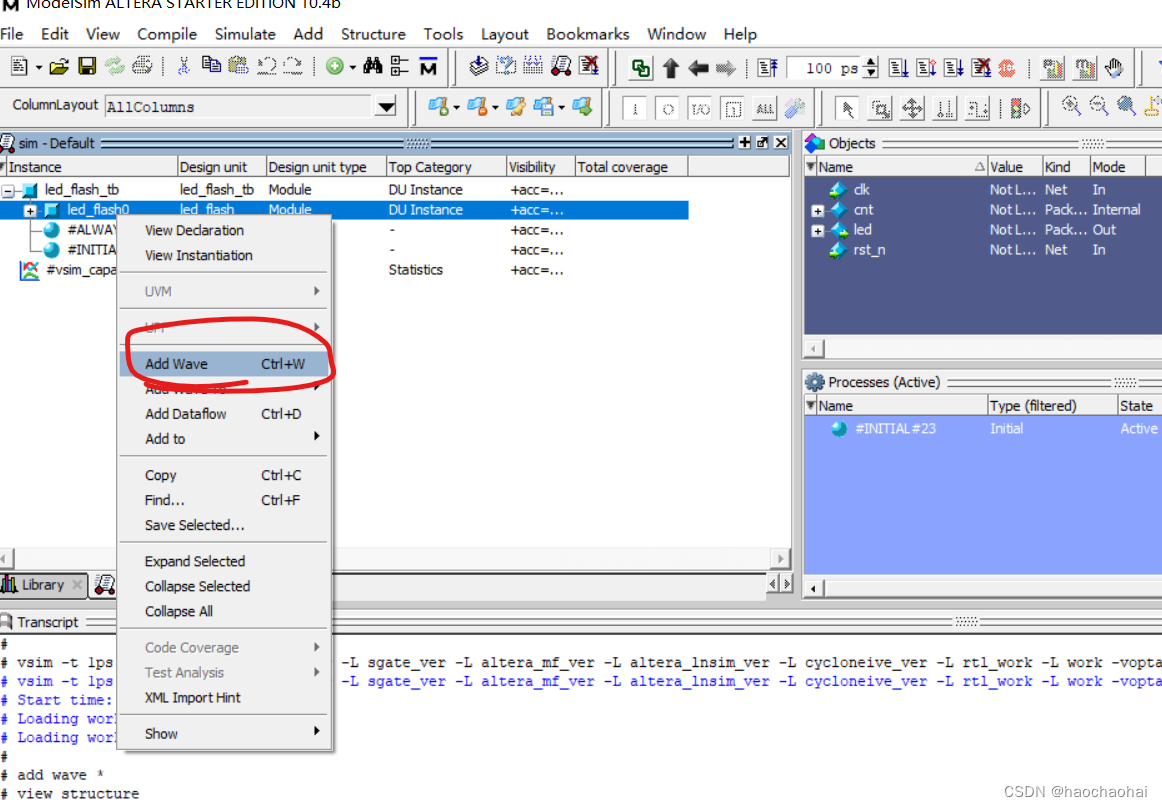

加入波形

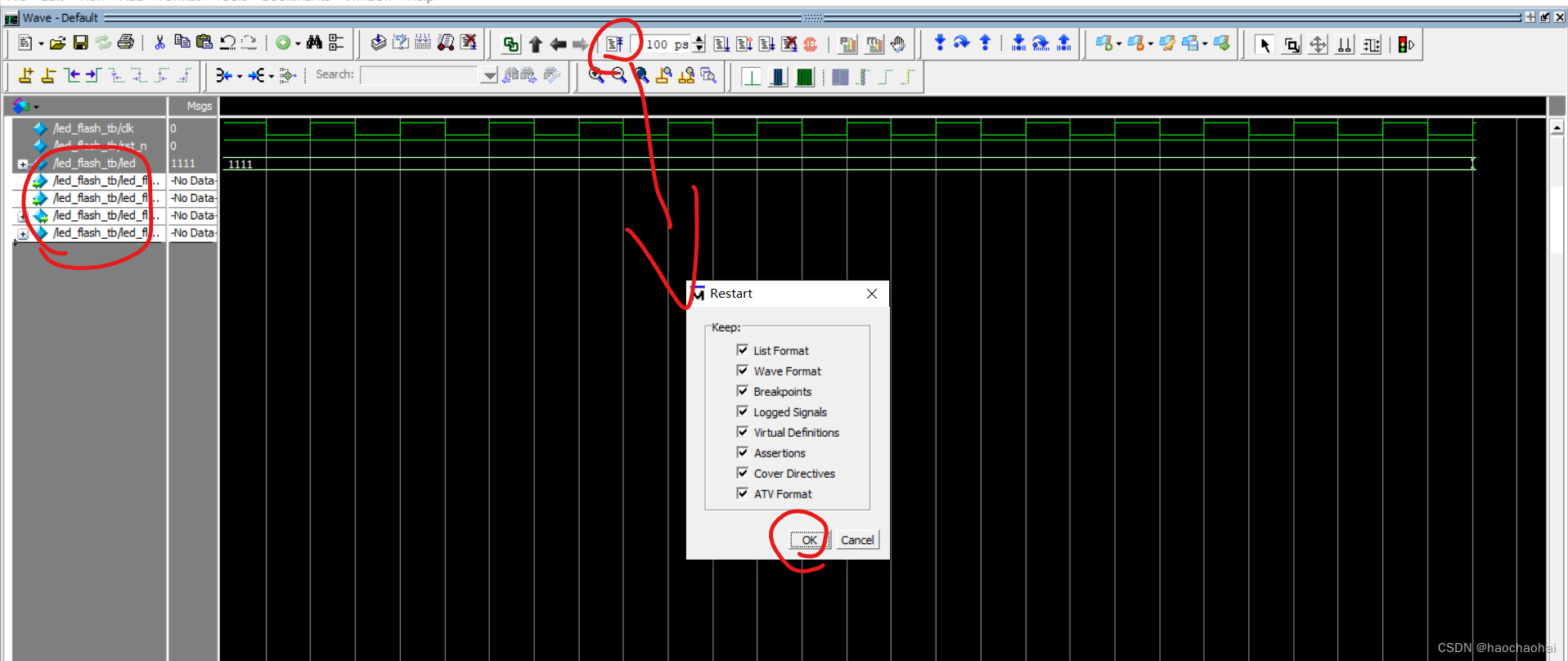

reststart

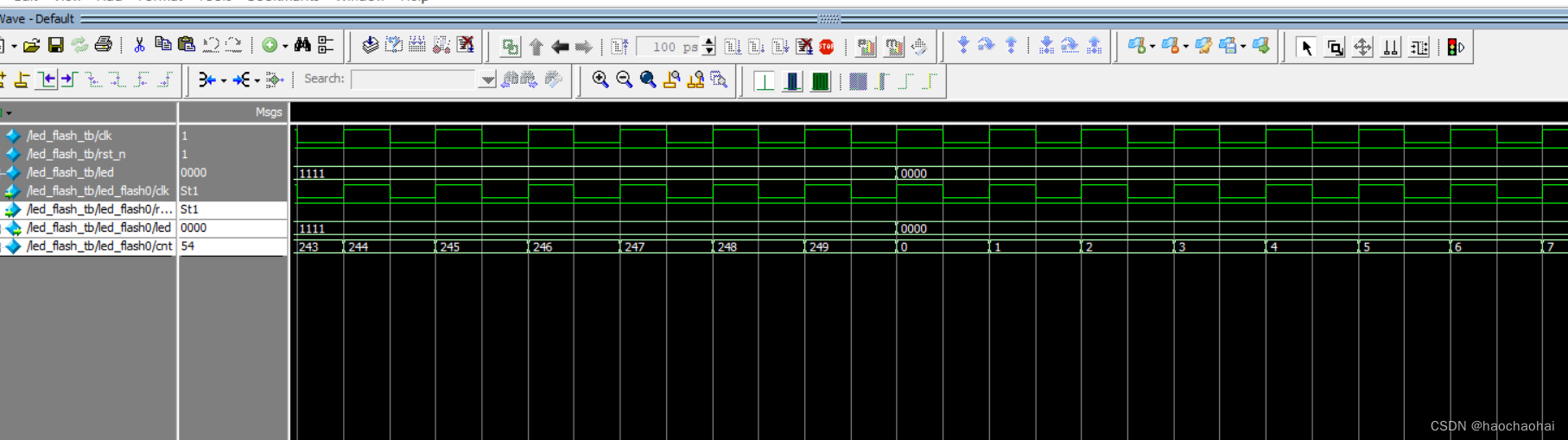

然后运行全部

修改数据格式

修改文件程序不需要再进行分析综合仿真,可以进行重新编译 注意:修改程序要保存,

然后仿真ok,这样不用分析综合可以节约大量时间!!!

6463

6463

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?