EtherCAT从站学习笔记——PDI通信接口

大多数EtherCAT从站设计从站微处理器芯片是普通单片机,数据传输是通过SPI串行接口进行的,传输效率比较低,这就导致EtherCAT通信协议卓越的性能无法得到充分的发挥。在MCU与LAN9252的通信中,本方案利用PS端的引脚设计了FSMC模块并行传输数据,极大地提高了数据传输速率。FSMC技术主要有如下特点:

1)有多种可扩展的存储器型号;

2)可以同时扩展多种外部存储器;

3)可以对外部存储器进行快速读写;

4)易于扩展多种外部存储器;

5)易于实现多种存储操作。

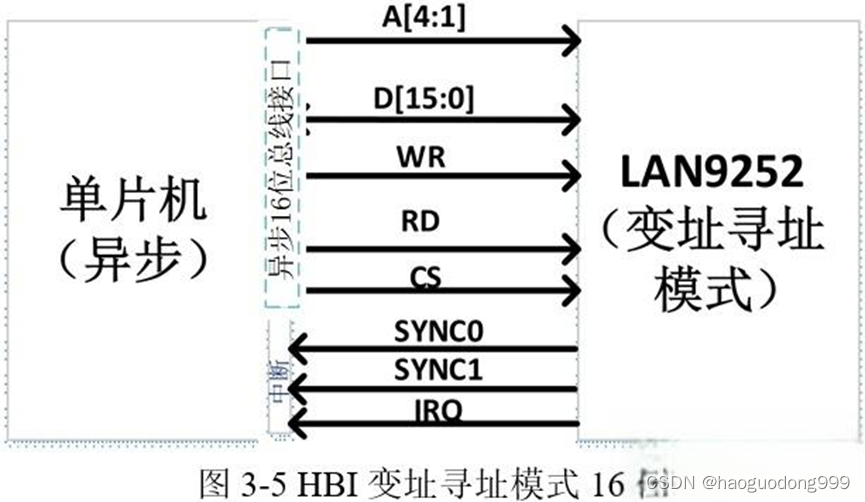

如图3-5所示,为HBI变址寻址模式下的MCU与LAN9252连接示意图。其中包括4位地址线、16位数据线、读写信号线、片选信号线及SYNC0、SYNC1、IRQ中断线。

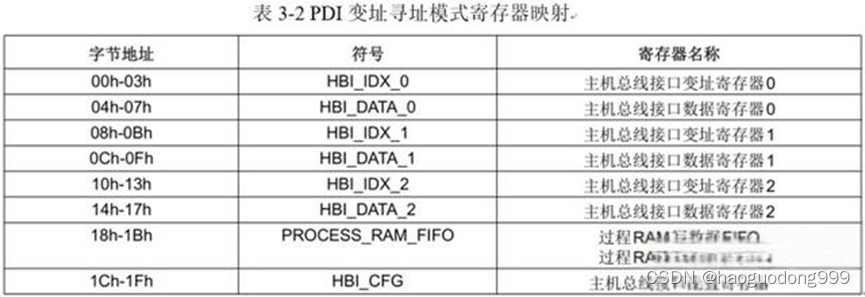

LAN9252提供3个变址/数据寄存器存储区,每个存储区单独进行字节/字-双字转换。内部寄存器的访问方式是:先写入3个变址寄存器之一,接着读取或写入相应的数据寄存器。3个变址/数据寄存器存储区支持最多3个独立的驱动器线程,而不会出现访问冲突。每个线程可写入其分配的变址寄存器,而不会出现被其他线程改写的问题。同一32位变址/数据寄存器中需要2个16位周期或4个8位周期,但这些访问可以交错进行。支持对过程数据FIFO进行直接(非变址)读写访问。直接FIFO访问提供单独的字节/字-双字转换,支持对变址/数据寄存器进行交错访问。

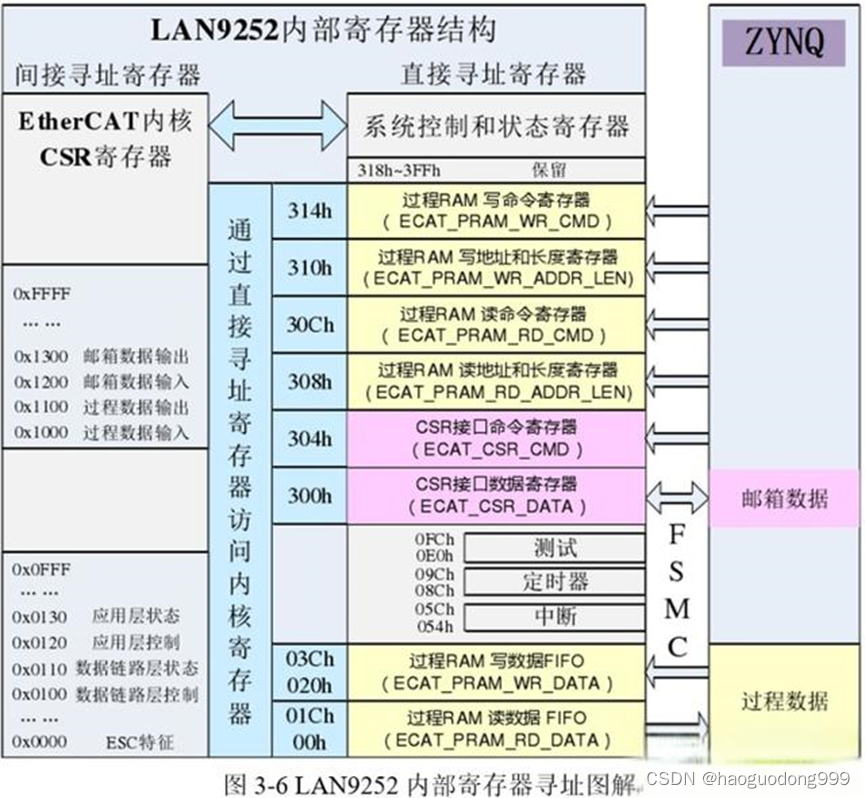

MCU并不能通过FSMC总线接口直接访问LAN9252内部的EtherCAT内核寄存器,而是需要通过LAN9252提供的系统控制和状态寄存器进行间接寻址,寻址方式如图3-6所示。

间接读写EtherCAT内核寄存器分为两种:EtherCAT内核寄存器CSR的读写,为单次读写;EtherCAT过程数据RAM读写,为连续读写。

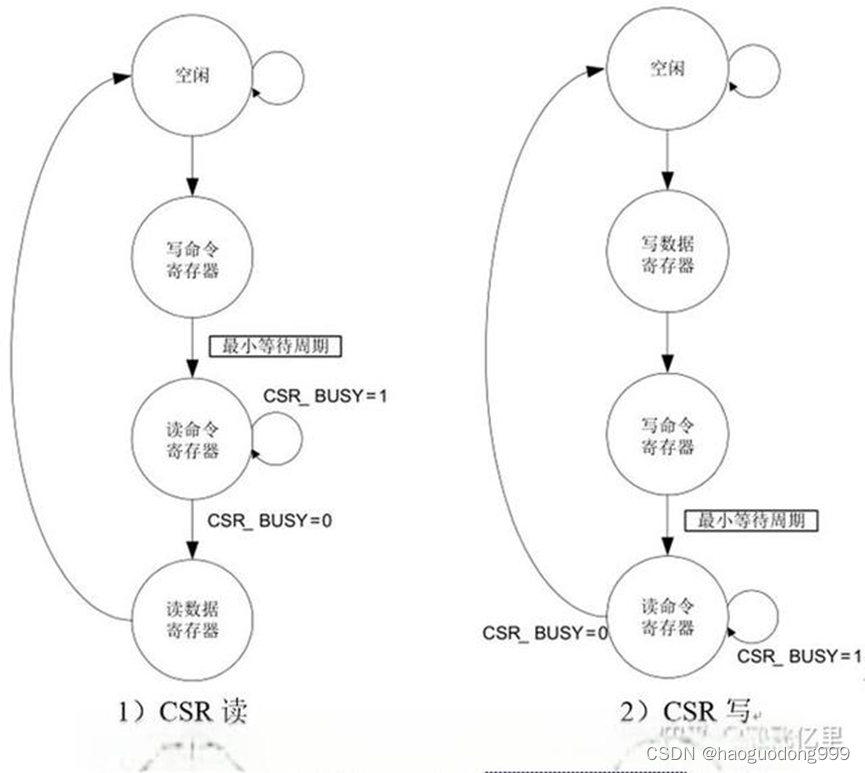

要读取单个EtherCAT内核寄存器,必须通过以下方式发起读周期:单次写入EtherCATCSR接口命令寄存器(ECAT_CSR_CMD),将CSR繁忙(CSR_BUSY)位置1、将CSR地址(CSR_ADDR)字段设置为所需寄存器地址、将读/写(R_nW)位置1以及将CSR大小(CSR_SIZE)字段设置为所需大小。当CSR繁忙(CSR_BUSY)位清零时,可读取有效数据,即可以从EtherCATCSR接口数据寄存器(ECAT_CSR_DATA)读取数据。有效数据始终与EtherCATCSR接口数据寄存器(ECAT_CSR_DATA)的最低位对齐。图3-71)给出了读取EtherCAT内核CSR时所需过程的图示

要写入单个EtherCAT内核寄存器,必须首先向EtherCATCSR接口数据寄存器(ECAT_CSR_DATA)写入所需数据。有效数据始终与EtherCATCSR接口数据寄存器(ECAT_CSR_DATA)的最低位对齐。必须通过以下方式发起写周期:单次写入EtherCATCSR接口命令寄存器(ECAT_CSR_CMD),将CSR繁忙(CSR_BUSY)位置1、将CSR地址(CSR_ADDR)字段设置为所需寄存器地址、将读/写(R_nW)位清零以及将CSR大小(CSR_SIZE)字段设置为所需大小。写周期的完成由CSR繁忙(CSR_BUSY)位清零来指示。图3-72)给出了写入EtherCAT内核CSR时所需过程的图示。

过程数据的传输方式与其他间接寻址的寄存器不同,过程数据从EtherCAT内核经16级深32位宽FIFO传输,FIFO的基址为00h,但它也可在其他7个连续的存储单元访问。主机可在这些别名端口存储单元中的任一个存储单元访问FIFO,因为它们的功能相同且包含相同的数据。通过实现这种别名端口寻址,主机可对连续地址进行突发访问。

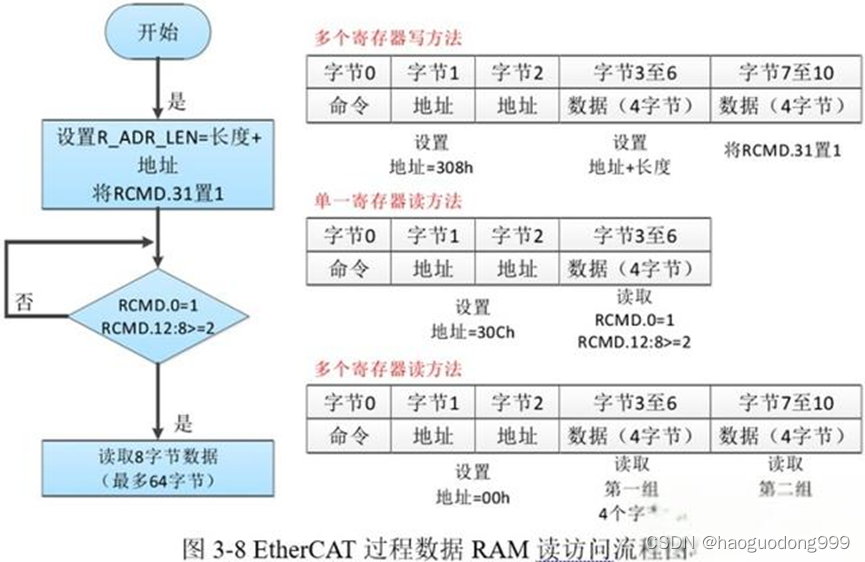

如果要连续读取EtherCAT过程数据RAM,需要通过以下方式发起读周期:首先向EtherCAT过程RAM读地址和长度寄存器(ECAT_PRAM_RD_ADDR_LEN)写入所需传输的起始字节地址和长度(单位为字节),接着写入EtherCAT过程RAM读命令寄存器(ECAT_PRAM_RD_CMD)以将PRAM读繁忙(PRAM_READ_BUSY)位置1。

有效数据通过EtherCAT过程RAM读数据FIFO(ECAT_PRAM_RD_DATA)从FIFO读取。PRAM数据可读次数(PRAM_READ_AVAIL_CNT)字段指示在无需再次校验状态的条件下可执行的读操作次数。最后一次读取EtherCAT过程数据RAM读数据FIFO(ECAT_PRAM_RD_DATA)后,PRAM读繁忙(PRAM_READ_BUSY)将自清零。当数据从FIFO传输到EtherCAT内核时,PRAM写长度(PRAM_WRITE_LEN)和PRAM写地址(PRAM_WRITE_ADDR)会进行更新以显示进程,流程图如图3-8。其中,RCMD:EtherCAT过程RAM读命令寄存器(地址=30Ch),R_ADR_LEN:EtherCAT过程RAM读地址和长度寄存器(地址308h)。

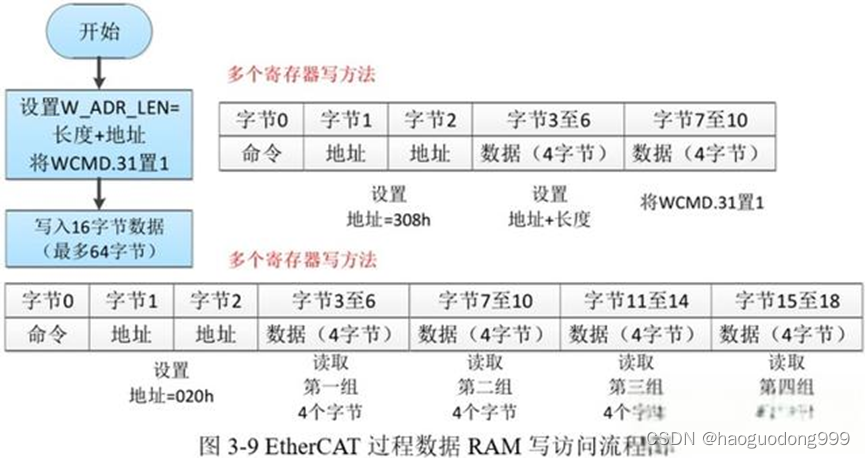

如果要写入EtherCAT过程数据RAM,需要通过以下方式发起写周期:首先向EtherCAT过程RAM写地址和长度寄存器(ECAT_PRAM_WR_ADDR_LEN)写入所需传输的起始字节地址和长度(单位为字节),接着写入EtherCAT过程RAM写命令寄存器(ECAT_PRAM_WR_CMD)以使PRAM写繁忙(AM_WRITE_BUSY)位置1。

数据经16级深32位宽FIFO传输到EtherCAT内核中。当EtherCAT过程RAM写命令寄存器(ECAT_PRAM_WR_CMD)中的PRAM可写空间(PRAM_WRITE_AVAIL)位指示空间可用时,主机可通过EtherCAT过程RAM写数据FIFO(ECAT_PRAM_WR_DATA)向FIFO写入数据。PRAM空间可写次数(PRAM_WRITE_AVAIL_CNT)字段指示在无需再次校验状态的条件下可执行的写操作次数。最后一次向EtherCAT内核写入数据后,PRAM写繁忙(AM_WRITE_BUSY)将自清零。当数据从FIFO传输到EtherCAT内核时,PRAM写长度(PRAM_WRITE_LEN)和PRAM写地址(PRAM_WRITE_ADDR)会进行更新以显示进程,流程图如图3-9。其中,WCMD:EtherCAT过程RAM写命令寄存器(地址=314h),W_ADR_LEN:EtherCAT过程RAM写地址和长度寄存器(地址=310h)。

必要时,可通过将EtherCAT过程RAM读命令寄存器(ECAT_PRAM_RD_CMD)中的PRAM读中止(PRAM_READ_ABORT)位置1来中止读命令。同理,也可通过将EtherCAT过程RAM写命令寄存器(ECAT_PRAM_WR_CMD)中的PRAM写中止(PRAM_WRITE_ABORT)位置1来中止写命令。

本文详细介绍了如何通过FSMC技术改进EtherCAT从站与LAN9252的通信,提升数据传输速率,以及如何通过PDI通信接口进行EtherCAT内核寄存器的间接寻址,包括读写过程和FIFO操作的详细步骤。

本文详细介绍了如何通过FSMC技术改进EtherCAT从站与LAN9252的通信,提升数据传输速率,以及如何通过PDI通信接口进行EtherCAT内核寄存器的间接寻址,包括读写过程和FIFO操作的详细步骤。

1232

1232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?