第一讲 前言

只要是做SOC芯片的项目都需要SOC验证,SOC验证也是芯片验证的重中之重。

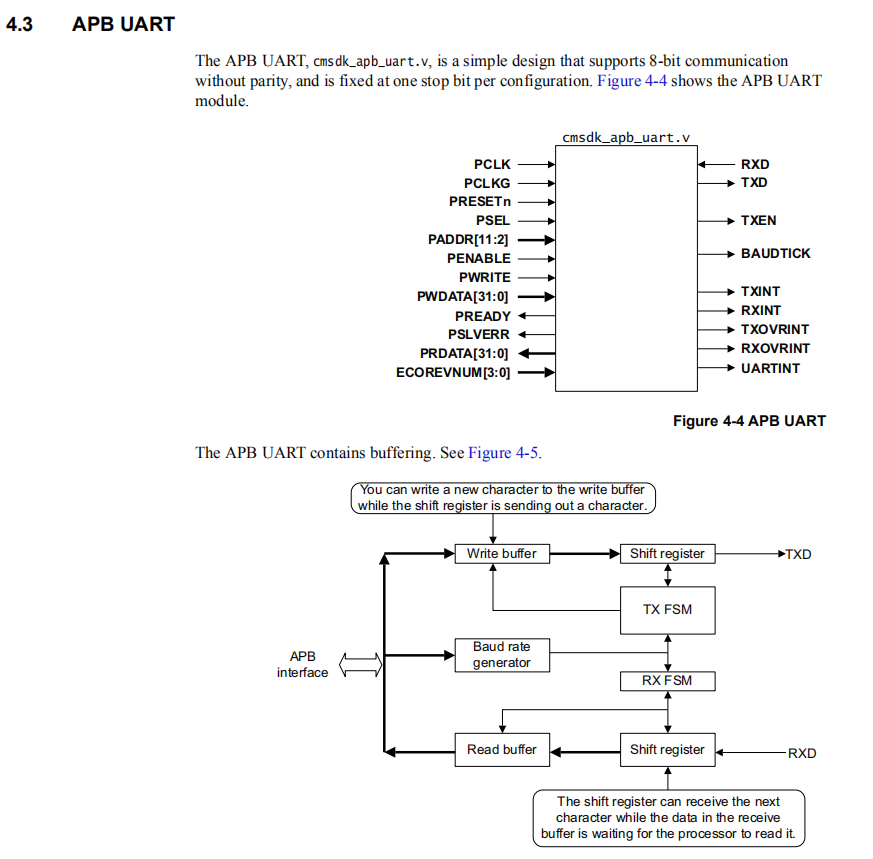

在之前做过ahb2apb、ahb2uart的验证之后,这篇文章提到相关内容都很少深入,于是乎,还是后面打算去啃ARM架构,默写代码去了!

课程先修知识:

Linux基本操作

Verilog基础

电路设计基础

UVM验证方法学

测试点分解

第二讲 验证flow

验证的Roadmap

验证的目标

UVM验证方法学

ASIC验证分解

验证策略和任务的分解

AMBA可重用、灵活性、兼容性、广泛支持

一.验证的Roadmap

1.ASIC芯片项目流程

市场需求>产品定义>硬件、软件>芯片测试>产品发布

硬件:芯片定义>芯片开发>芯片IO

软件:软件定义>软件开发>软硬件联调

2.验证的阶段和内容

立项------>Tape Out

验证计划>模块验证>子系统验证>系统验证>post仿真

总体设计>模块设计>系统集成>设计迭代>前端实现>后端设计

3.验证阶段的输入输出

< I > 芯片总体设计>验证计划

内容划分:(模块、子系统、系统)

时间安排:(Tape Out时间和设计时间综合考虑)

人力需求

验证平台规划:模块验证平台、系统验证平台等

< II >模块设计spec、协议——>模块验证计划、验证report

- 验证计划主要关注feature list和testcase

- 验证feature迭代

- Corner case添加

- Code coverage要求(视情况),function coverage (必须100%)

行覆盖率、状态机覆盖率、行覆盖率(每个公司的要求不一致)

代码覆盖率100%不能保证功能覆盖率

< III >子系统设计spec、协议——>子系统验证计划、子系统验证平台、验证report

- 验证计划主要关注feature list和teatcase

- 验证计划迭代

- Corner case添加

- 接口Toggle coverage (不一定100%)

< IV >系统设计spec、应用场景——>系统验证计划、系统验证平台、验证report

- 验证计划主要关注feature list和teatcase

- 验证feature需要与设计、架构、软件进行头脑风暴

- 关注性能

- Direct case,C code

< V >SDF文件——>后仿验证计划、验证report

- 验证计划主要关注feature list和teatcase

- 验证feature需要与设计、架构、软件进行头脑风暴

- 关注性能

- Direct case,C code

二.验证的目标

1.为什么需要验证

- 验证对IC的重要性,对比软件

- 验证的目的是什么?

- 要验证什么?该怎么验?

软件也会验证,软件有问题打个补丁就可以继续上线;而IC出错就变砖头;

验证的目标就是找bug,保证tape out的芯片没致命问题;

要验证设计的代码,有没有实现这个功能,考虑的问题就多一些

2.怎么达成目标?

- 激励与响应

- 检查点

- 依据

- 100%的含义[ -------]

3.达成目标的手段

- 验证工具的掌握:

验证语言 、验证方法学、仿真工具、脚本语言 - 算法/协议的理解:

优秀的验证工程师对协议的理解要比设计工程师还透彻

[最好知道为什么错了,该怎么修改,希望自己能达到到这种水平] - 验证的理念:

要验证什么 怎么检查高效 问题的原因是什么

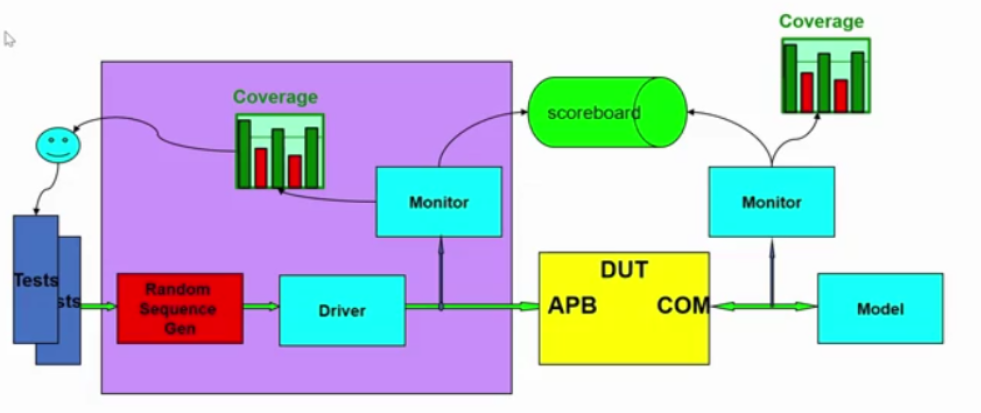

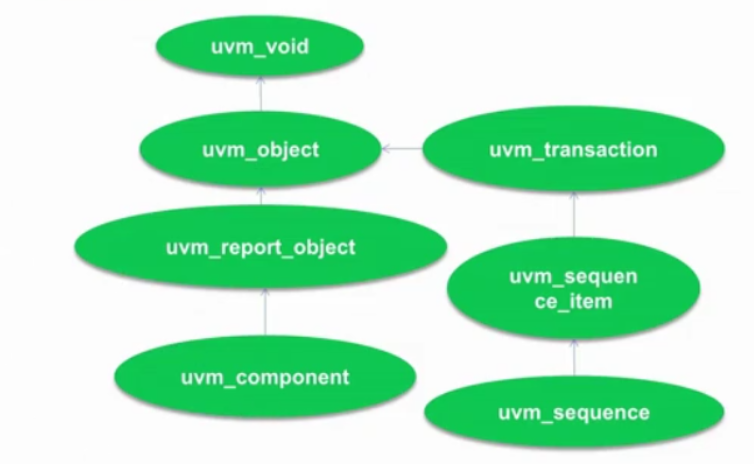

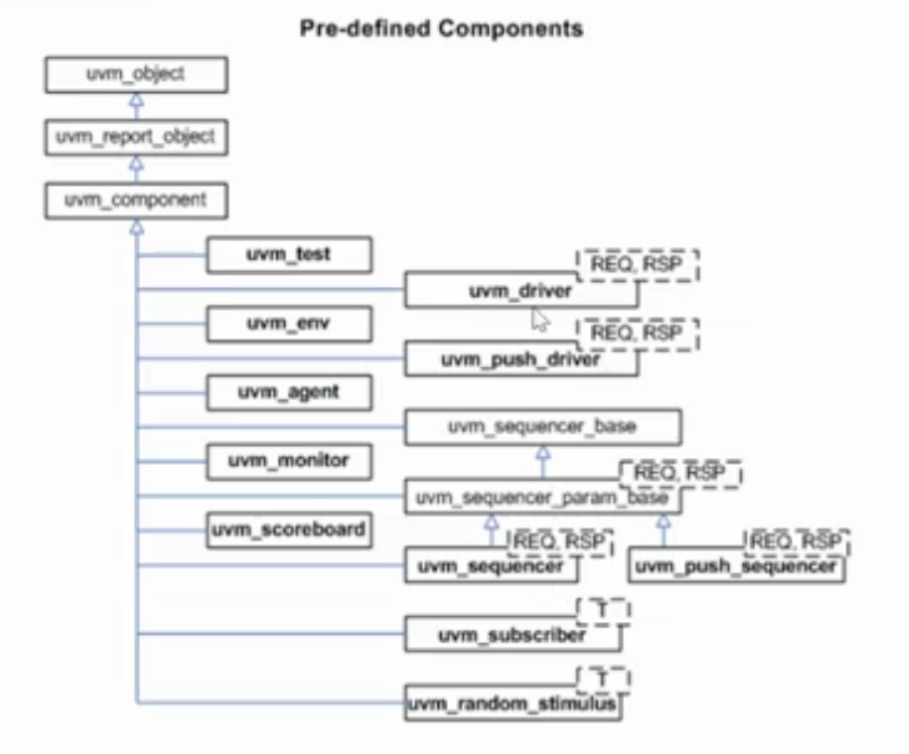

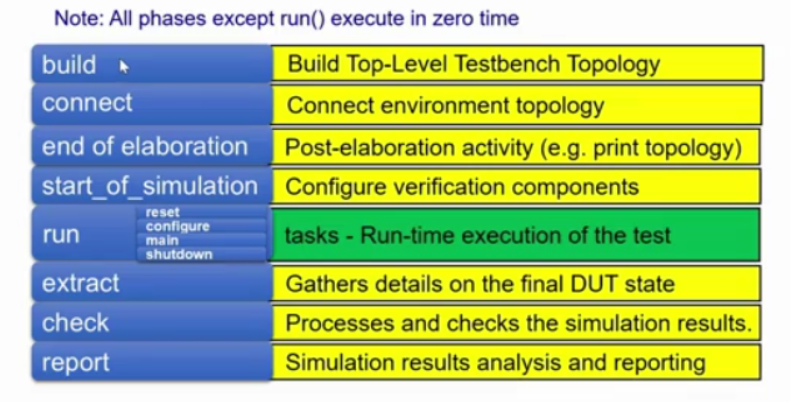

三.UVM验证方法学

CDV-基于覆盖率驱动 验证

uvm_component就是基础航线、铁路

uvm_sequence就是飞机、火车

只有run phase是task,其他都是function

四.ASIC验证分解

1.按大类分解

- 数字前端验证:模块验证、子系统验证、系统验证

- 数字后端验证:后端验证(post)

- FPGA验证:软硬件协同[定位问题比较困难]

- 加速器验证:验证、软件[三家EDA厂商]

- Validation[芯片回来之后的测试,比如老化、插拔次数]

- 为什么要这么划分?[放到系统级验证,太耗时]

2.模块验证

- 模块验证侧重点在模块本身功能的验证

- 以模块的spec和协议为基础提取验证feature

- 验证计划的重点是feature和验证架构,然后列出testcase

- 验证计划根据验证的开展进行增补

- 模块能够覆盖的绝对不到下一级去覆盖

- Function coverage 100%

- Code coverage 95%+(各公司有标准)

- Check list[看以前在哪里吃过亏]

- 对于IIP,检查参数设置

- 寄存器访问、复位值

- 寄存器field功能

- 协议检查,时序要求

- 中断产生、查询、清楚

- 所有输入输出信号

- 工作模式覆盖

- 状态机跳转

- FIFO的读写操作,空满状态

- 计数器的边界load

- Ram的读写功能,边界点

3.子系统验证

- 子系统验证侧重点在系统的互联性

- 关注系统的工作模式

- 关注系统的复杂场景应用

- 完成度:芯片bug趋于收敛

- Review toggle coverage,exclude之后100%

- Check list检查

3.子系统验证内容

- 中断的产生和连接

- DMA功能,所有通道的req,传输、中断

- IP的模块功能,特别是与其他模块相关的,与接口相关的

- IOMAX

- 睡眠唤醒

- Memory读写

- GPIO功能

- Clk/Reset

4.系统验证

- c代码软硬件协同仿真

- 中断处理

- 关键系统路径覆盖

- 芯片工作模块和测试模块

- 数据通路和性能

- LowPower功能实现

4.系统验证内容

- 基本IP功能

- 中断处理

- 多IP同时工作

- 程序启动

- 工作模式,如安全工作

- jtag功能

- 寄存器测试

- 应用场景

5.后仿验证

- 网表+sdf,带时序的仿真

wc: worst case slow,低电压,高温度,慢工艺->一般情况下 delay最大, setup差

wcl: worst case low-temperature,低电压,低温度,慢工艺->温度反转效应时 delay最大, setup差

lt:即low- temperature,也叫bc( best case fast),高电压,低温度,快工艺->一般情况下 delay最小,hold差

ml:max- leakage,高电压,高温度,快工艺->温度反转效应下 delay最小,hold差

tc: typical,普通电压,普通温度,标准工艺->各种 typical - 从系统case中选取case,专注异步处理和PAD接口相关

- 仿真速度较慢,case需要优化

[后仿时间很长,做优化]

五.验证策略和任务的分解

- 验证平台

子系统验证平台 系统验证平台 后仿验证平台 - 处理脚本

makefile regression coverage - 子系统验证

内容作为作业,学员补充 - 系统验证

内容作为作业,学员补充 - Netlist:验证和后仿验证

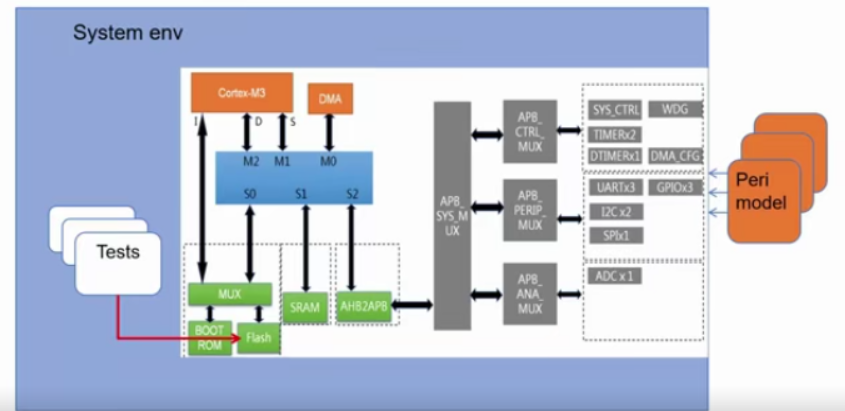

第三讲 子系统关注点的验证

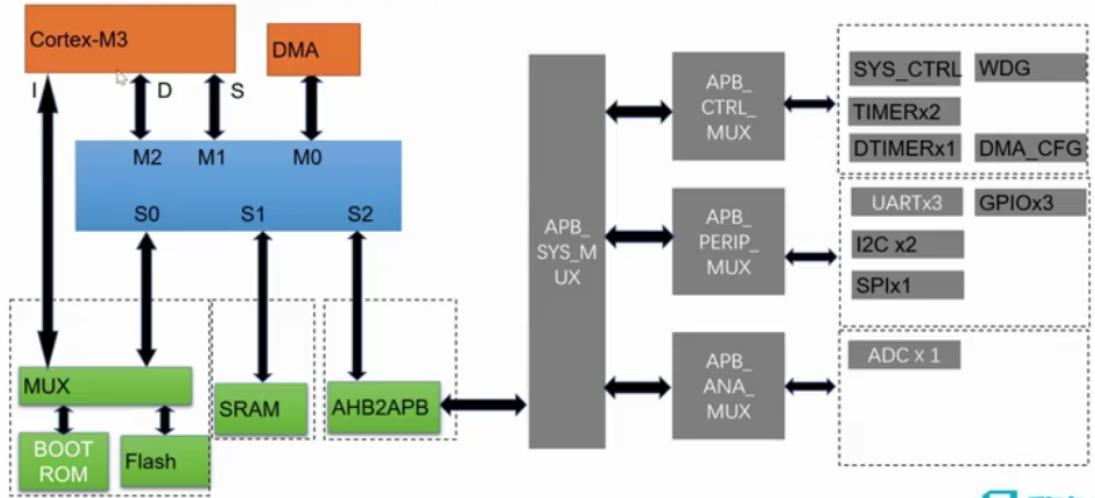

采用的spec就是下面这个!

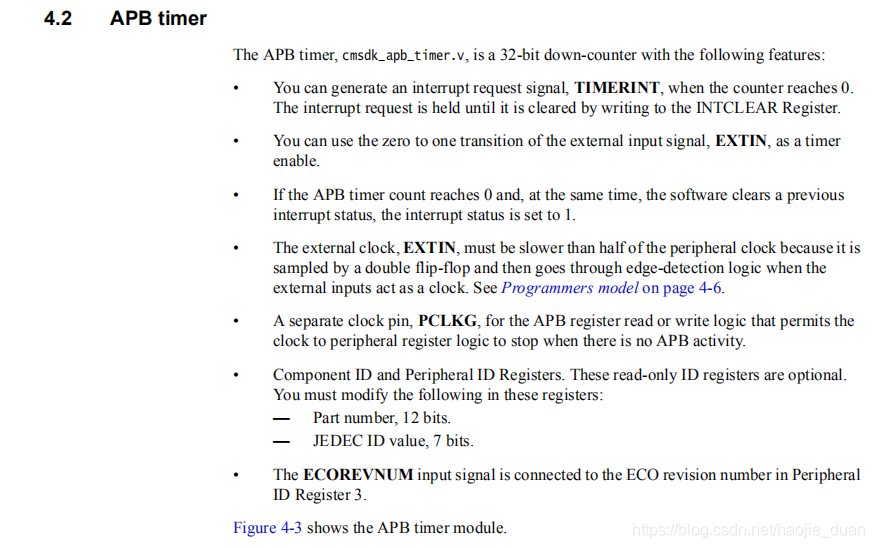

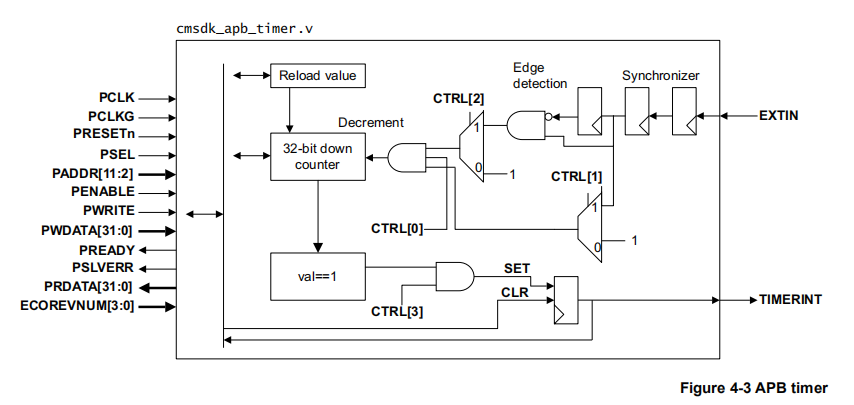

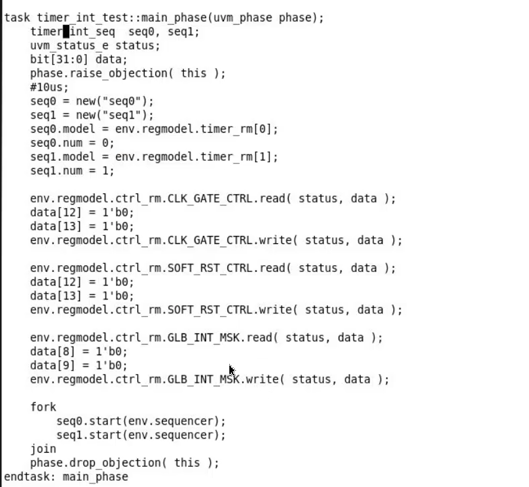

一 、APB timer验证讲解

写seq和对应的test

mcu_ctrl_register也有spec

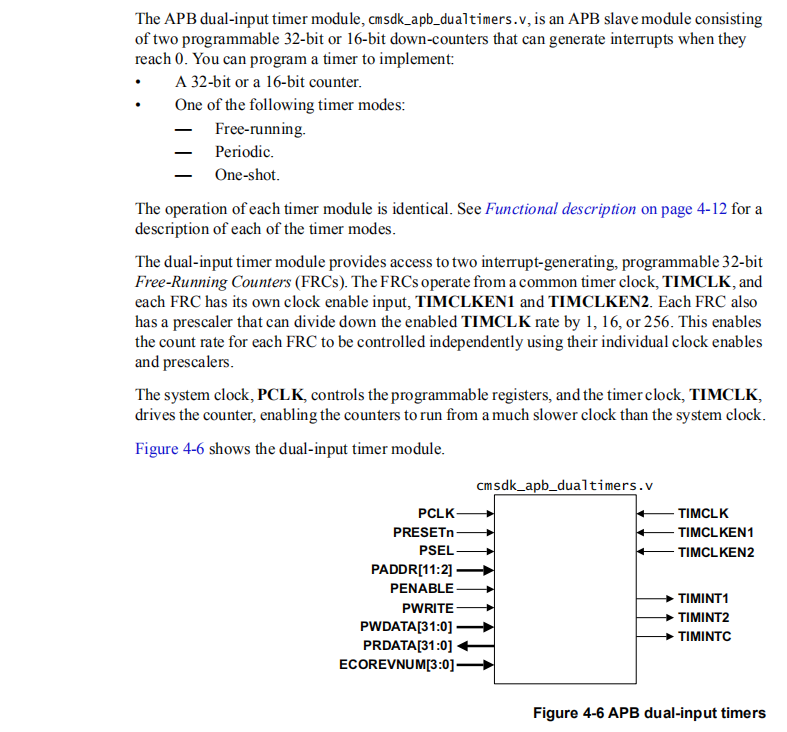

二 、APB dtimer验证

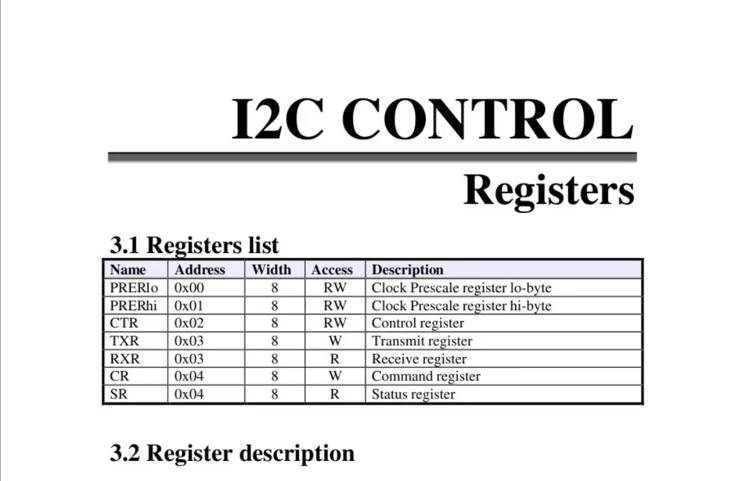

三、I2C验证

四、uart验证

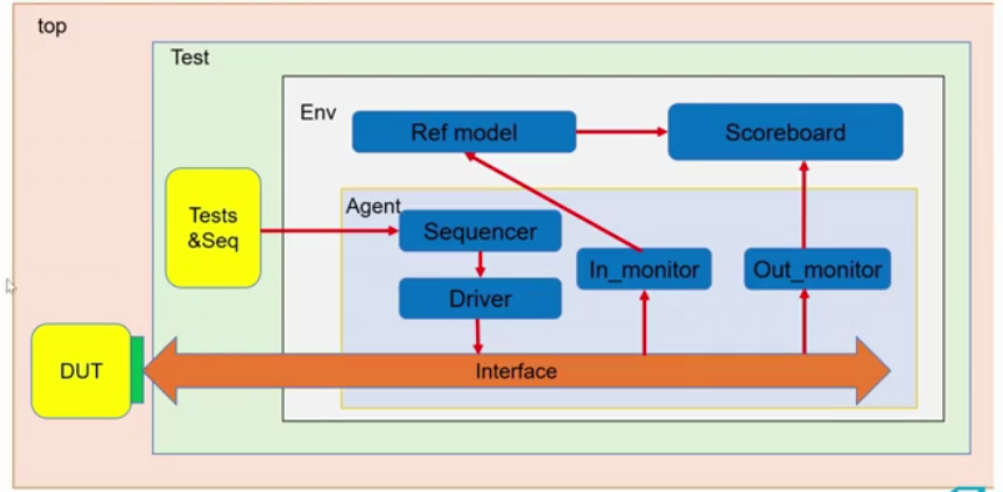

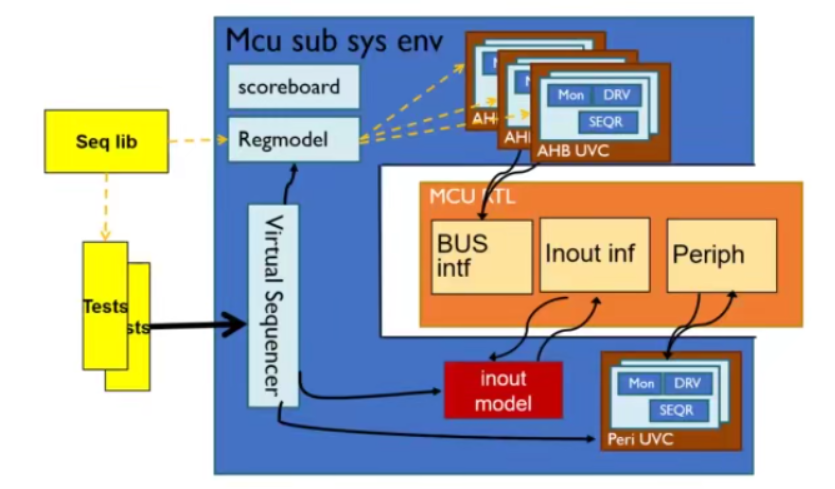

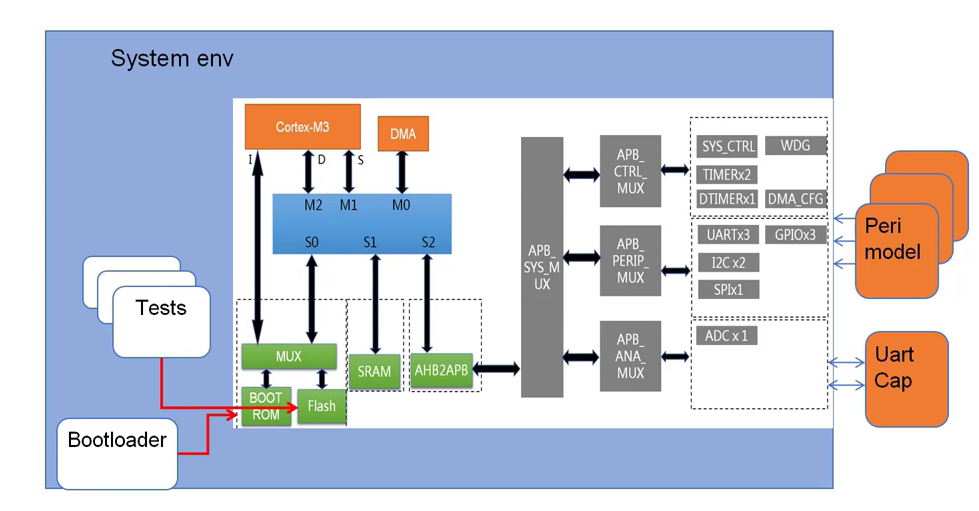

第四讲 子系统验证环境

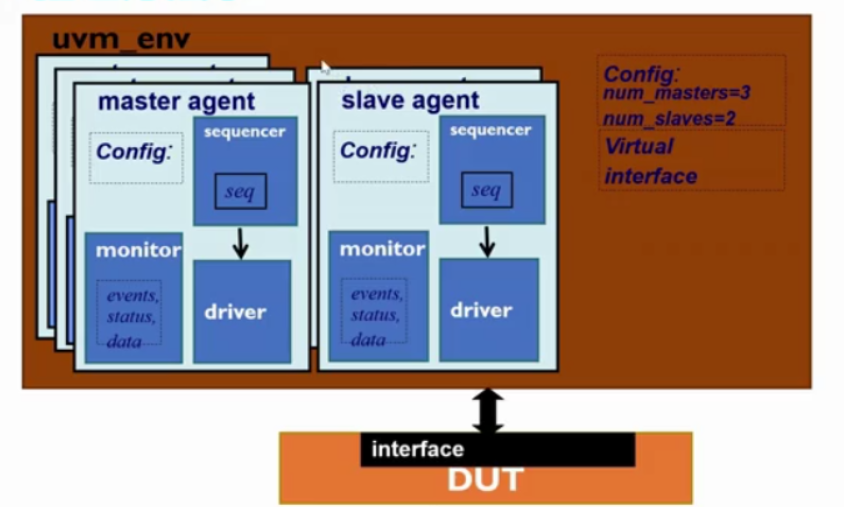

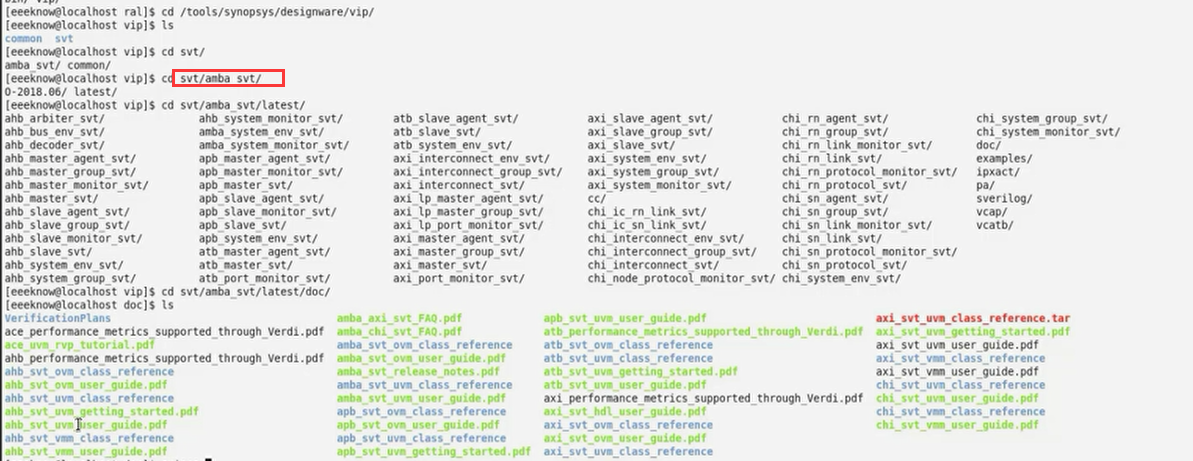

- AHB VIP介绍

- Regmodelf的生成

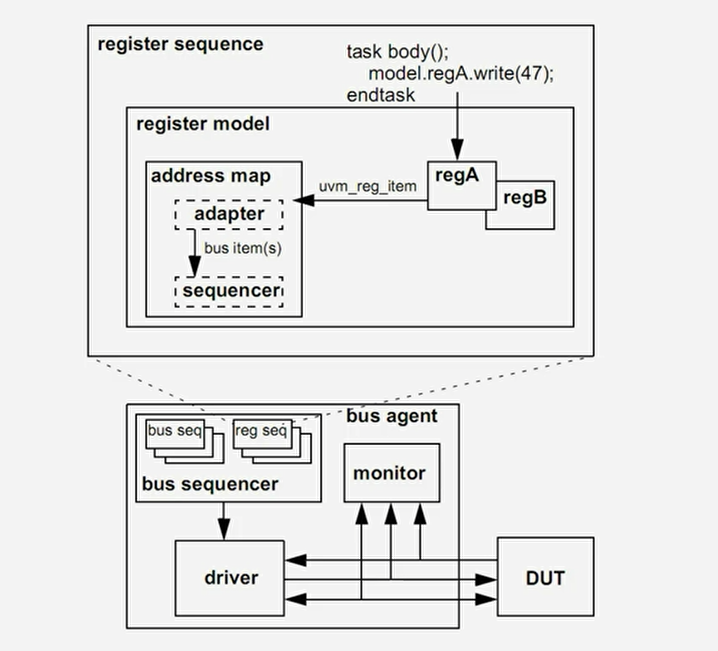

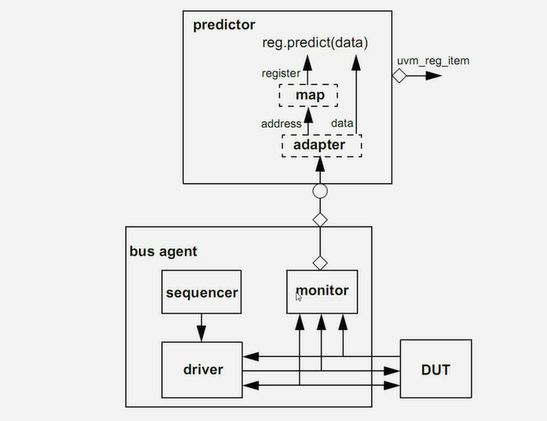

- Adapter介绍

- Virtual sequencer

- Environment

- Tb top

- Base test

一. AHB VIP介绍

- 1.为什么使用VIP

- 2.AHB VIP使用:三大公司的免费

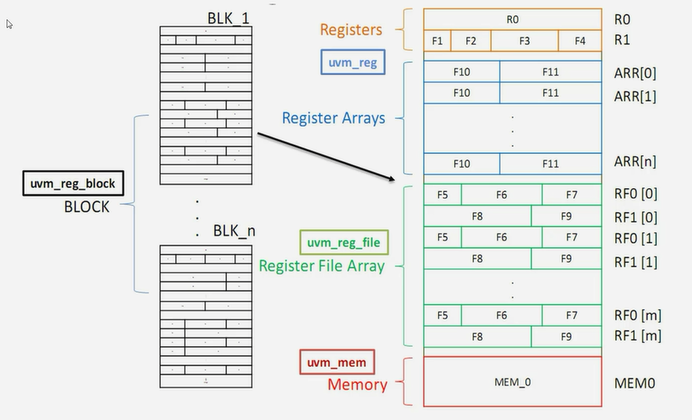

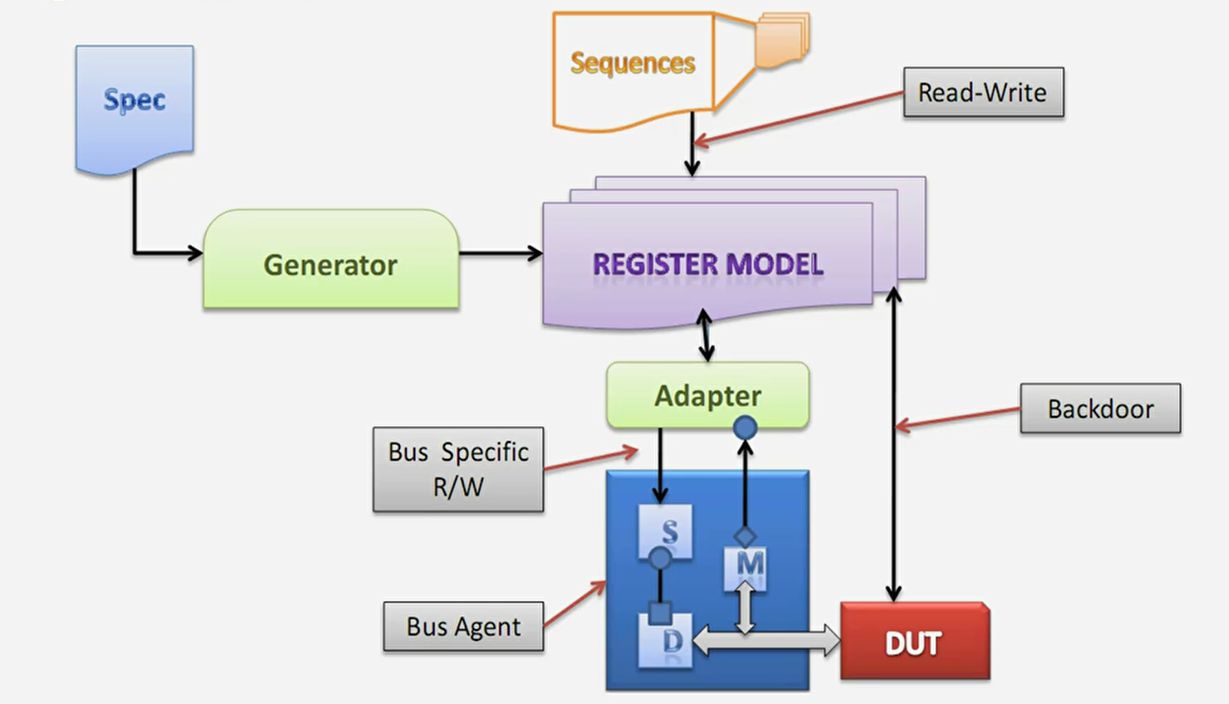

二. Regmodelf的生成

dut的抽象模型

ralgen可以生成寄存器

三. Adapter介绍

生成regmodel,就要和dut连接起来

镜像值、期望值

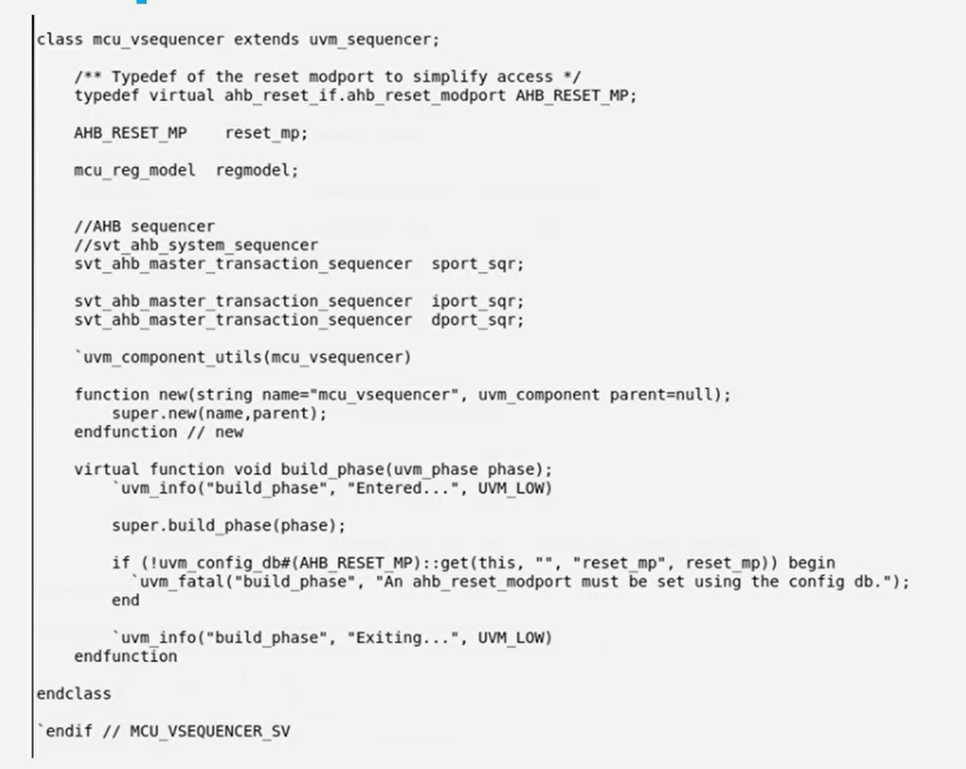

四. Virtual sequencer

sequence都运行在sequencer上

五. Environment

- Define component

- Create component

- Component connect

六. Tb top

- Import package

- Interface instantiation

- DUT instantiation

- Config_db

- Clk and reset

- Waveform

七. Base test

- Create environment

- Config environment

- Reset phase

- Main phase

第五讲 子系统验证仿真

Makefile、debug、功能点梳理

第六讲 子系统验证回归

Memory测试

DMA模块、验证

覆盖率统计和分析

第七讲 系统级验证

一、系统级验证环境

第八讲 Netlist和post仿真

后记

本文已完结,最近几年应该不会补充了!

本文围绕SOC芯片验证展开,先介绍验证flow,包括ASIC芯片项目流程、各验证阶段的输入输出、目标及达成手段,还提及UVM验证方法学和ASIC验证分解。接着阐述子系统关注点验证、验证环境搭建、仿真、回归等内容,最后涉及系统级验证和Netlist及post仿真。

本文围绕SOC芯片验证展开,先介绍验证flow,包括ASIC芯片项目流程、各验证阶段的输入输出、目标及达成手段,还提及UVM验证方法学和ASIC验证分解。接着阐述子系统关注点验证、验证环境搭建、仿真、回归等内容,最后涉及系统级验证和Netlist及post仿真。

2983

2983

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?