在数字信号处理中,采集到的数都是定点数,有些算法对数据精度比较敏感,比如QAM高阶调制解调,在符号同步过程中,通过符号定时同步对接收到的信号进行盲解调。

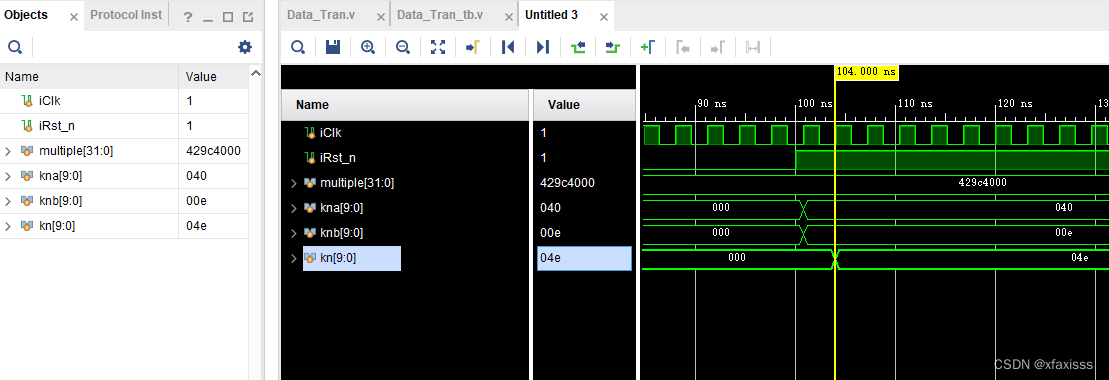

在同步过程中需要求取插值基点kn及小数uerr的数值,kn为整数,uerr的值为浮点数,该数据通过η与w的比值求取(kn+uerr=η/w),其中η设置为1,w=symbolrate*nsamp/fs,如果η和w的取值采用定点数,w取值可能与实际值偏差较大,解调星座图指标较差,如果采用浮点数,则FPGA处理需要求取其整数部分并使用定点数以满足时序逻辑确定采样基点mk,小数部分任然需要保留浮点数,这时需要求取kn及uerr的值。整数kn转换代码仿真:

module Data_Tran_tb;

reg iClk;

reg iRst_n;

reg [31:0] multiple = 32'b0_1000_0101_001_1100_0100_0000_0000_0000; //78.125

reg [9:0] kna,knb;

reg [9:0] kn;

always@(posedge iClk or negedge iRst_n)

begin

if(!iRst_n)begin

kn <= 0;

kna <= 0;

knb <= 0;

end else

begin

kna <= 10'd1<<(multiple[30:23]-8'd127);

knb <= multiple[22:0]>>(8'd150-multiple[30:23]);

kn <= kna + knb;

end

end

initial begin

// Initialize Inputs

iClk = 0;

iRst_n = 0;

#100;

iRst_n = 1'b1;

end

always #1.6 iClk =~iClk;

endmodule

仿真运算结果:

采用浮点数与定点数运算解调效果:

229

229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?