情景描述:

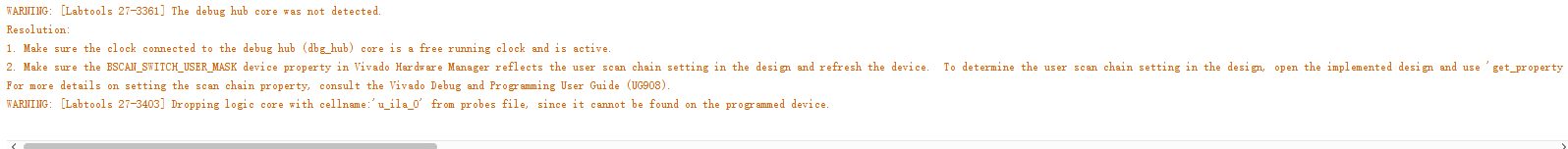

使用Vivado 2017.4书写Verilog代码,并且创建debug core进行信号抓取。添加完debug core并成功Run Implementaion,在IMPLEMENTATION的结构图中可以看到相应的ila_core和hub都已经建立。在生成bit文件的时候出现warning告知debug core被丢掉了,因为没有在设备上找到相应的内容,警告截图如下:

虽然bit文件可以正常生成和烧写,但是不能进行抓信号功能。

解决方法:

-

首先你需要确认你的操作流程正确,添加debug core的正确流程是:

Run Synthesis (综合) -> Mark debug(给想抓的信号打上debug标志)->Set Up Debug并添加你想要仿真的信号->Run Synthesis(再次综合)->Run Implementation(布线)->Generate Bitstream(生成bit流)注意set up debug之后要再次Run Synthesis,因为添加debug之后,你的约束文件会被修改,所以需要再次综合。

-

Refresh Device, 在程序烧写到device上之后,需要refresh device 才能加载到抓信号界面,因为烧写程序和抓信号都是通过Jtag线来做的

-

确认debug core连接时钟正确,需要检查所有的debug core是否连到了一个可用的时钟

-

确认debug core时钟频率比Jtag线的频率高,这是我出现上述问题的原因。

上板子抓信号的原理是: 信号会被缓存到板子上的debug core中,然后再通过Jtag线传到电脑,所以只有当Jtag线的频率低于debug core缓存信号的频率时,才能成功抓取信号。

确保debug core时钟频率比Jtag线的频率高的方法很容易想到有两种:

1、提高debug core的时钟频率,方法为在约束文件中主动书写debug core的时钟频率,方法可以参考博客:

https://www.cnblogs.com/kevinchase/p/7494865.html

2、降低Jtag线的频率,这种方法我猜想可能会导致烧写程序的速度变慢(个人感觉带宽不变,频率下降应该会导致烧写时间增长)。

方法是:

- 首先关闭和板子的连接,要确保是如下状态:

- 选择Open New Target

- 选择Jtag 的时钟频率,比debug core的频率低即可:

- 再重新连上FPGA->Program Device -> Refresh Device

通过以上流程,本人已顺利解决debug core 被删掉的问题。

补充:2020.1.8 我再次遇到了这个问题并且用上述方法没有解决

此次问题原因为:

时钟不是free running clock,对于free running clock的定义,我搜索到的结果为,上电就可以运行的时钟,而不能是需要一定条件才能运行的时钟。

解决方法:

我添加debug core的模块为PCIe模块,我猜测它的时钟可能和上位机有关,所以我将FPGA板插到主机的PCIe槽中再烧写程序就解决了。

另外,按照我搜索的结果,Jtag线和烧录器也可能导致上述问题,所以应当首先排除物理上的问题

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?