参考1:Cyclone IV Device Handbook

参考2:

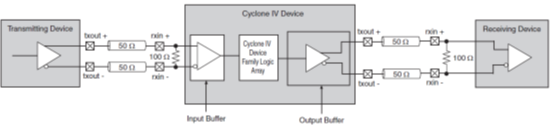

LVDS信号的电压摆幅只有350MV, 为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。LVDS的工作原理是其中发送端是一个为3.5mA的电流源,产生的3.5mA的电流通过差分线中的一路传到接收端。由于接收端对直流表现为高阻,电流通过接收端的100R的匹配电阻产生350mV的电压,同时电流经过差分线的另一条流回发送端。当发送端状态变化时它通过改变流经100R电阻的电流的方向产生有效的'0'和'1'状态态。

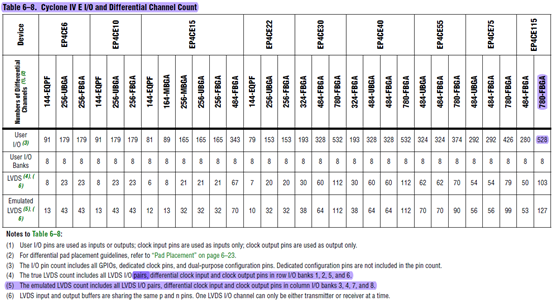

C4 E器件的左右边4个bank支持true LVDS transmitters,上面4个bank支持emulated LVDS transmitters。

C4 E器件使用true lvds transmitters接收和发送数据时,连接示意图如下,在接收时,端接100R电阻,发送数据时,不需要端接100R电阻。

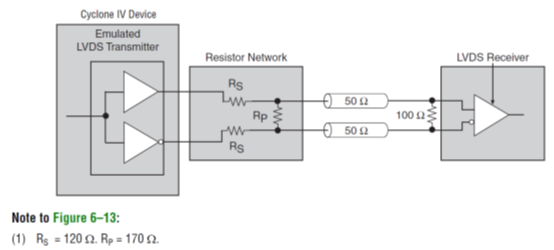

C4 E器件使用emulated lvds transmitters发送数据时,连接示意图如下。

由上可知,real lvds口用作lvds接口时比emulated lvds口要方便许多,所以在设计中如果使用C4 E器件,尽量使用1.2.5.6 bank来作lvds口。如果需要端接电阻,端接的电阻应该尽量靠近输出的IO口。还有一点需要的注意的是,不管是需要端接电阻还是不需要端接电阻的IO,在使用LVDS口输入时,需要端接100R电阻。

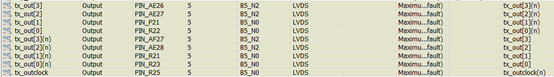

在画原理图时,lvds信号应该连到DIFFIO_**P和DIFFIO_**N上。

在layout时,要把一组LVDS信号线当做一根线来处理,它们与其他信号线的距离最好能大于20个mil。每一组LVDS内的两根信号线的长度需要做等长处理,同时采用"紧耦合"的走线方式。当"紧耦合"和"等长"发生矛盾,两者不可以兼得时,应该优先考虑等长。LVDS走 线尽量走直线,需要拐弯的部分,拐弯走成"圆弧"状。

Quartus中分配管脚时,需要选择I/O Standard为LVDS,然后会自动参数另一个*(n)的配对差分管脚

另外,根据altera提供的Guidelines,见Cyclone IV Device Handbook,设计时需注意以下问题:

-

控制阻抗,对线宽、线距做比较

-

走线时,差分线的线距尽量一致,以使共模抑制比(CMRR)最大

-

使用lvds_rx口时,端接电阻尽量靠近管脚

-

尽量使用表贴器件

-

避免90度走线

-

尽量不要打过孔,如果非得打过孔,差分线上过孔数量应一致

设计中还需注意以下3点:

-

选作LVDS的Bank的VCCIO电压是2.5V,在硬件设计时需要注意,如果电压分配不正确,也无法完成LVDS的分配。一旦该Bank的 VCCIO电压被设计成2.5V,那么该Bank的其他非LVDS信号(包括配置信号)的高电平也是2.5V了

-

当LVDS和普通信号一起作为输出信号时,普通信号的IO至少距离LVDS信号5个PIN。比如P101和P103作为LVDS输出,则 P96~P100,P102,P104~P108不可以同时被分配成普通输出信号,但可以被配置成LVDS输出信号。这些在硬件设计之初也需要有考虑。

-

LVDS信号非常讲究阻抗的匹配,LVDS的信号应该尽量少打过孔,在跨板传输时需要选择合适的接插件和信号线,如果接插件或者信号选择不正确,会大大影响传输的速率。

5879

5879

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?