fifo仿真的目的:

1、验证fifo的resetpin功能,看wr_rst_busy与rd_rst_busy情况。

2、验证1byte写入和8byte输出情况下,8byte输出的大小端模式;

3、full信号和empty的输出;

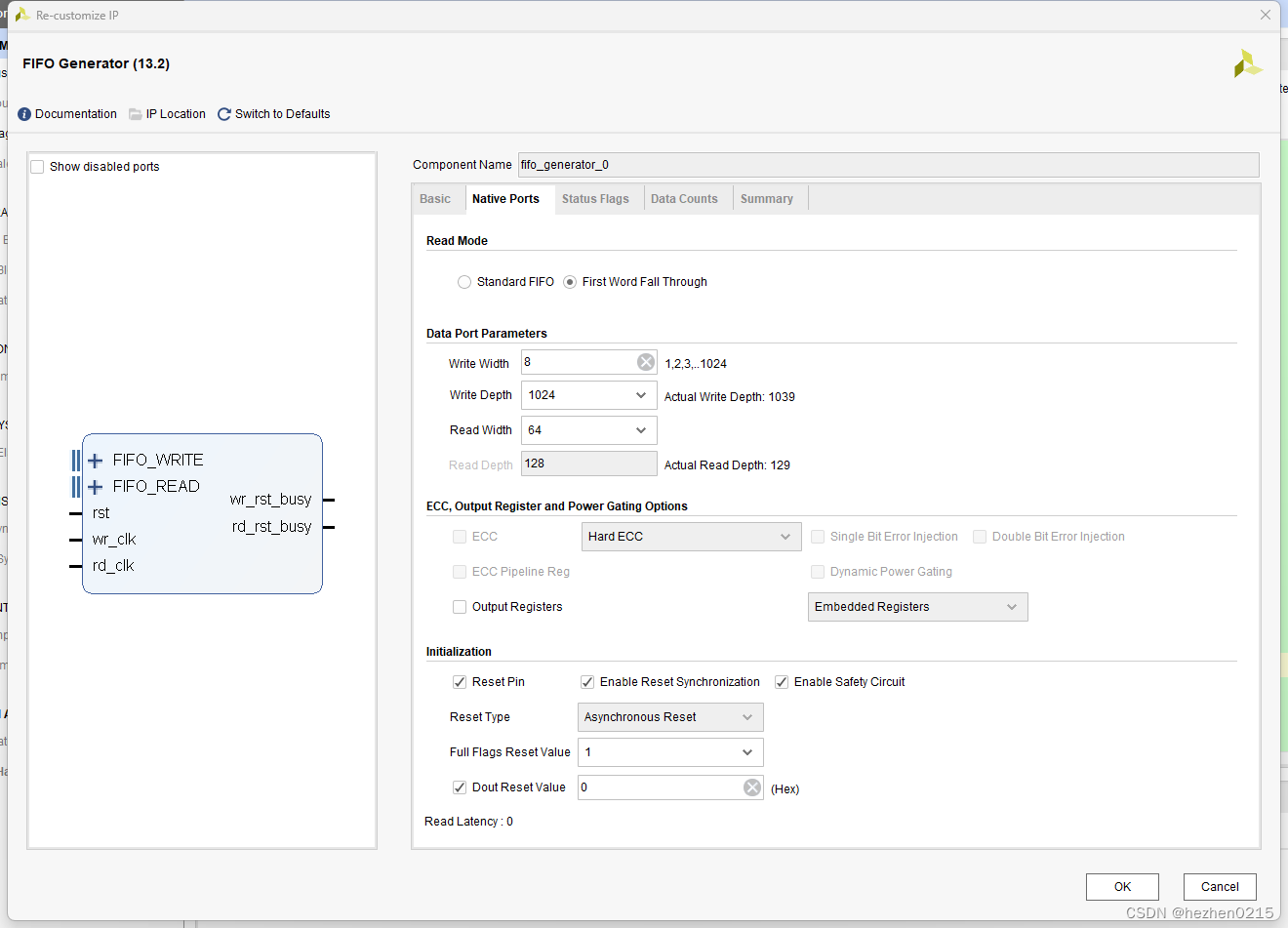

fifo IP的配置如下:

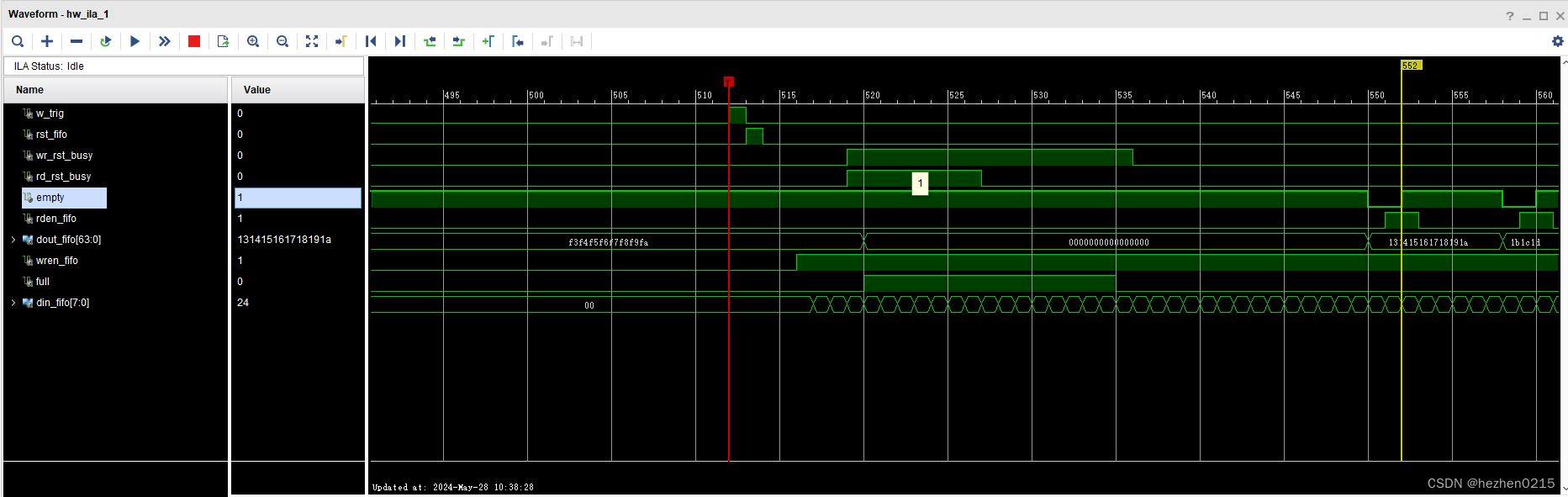

仿真结果如下:

fifo仿真总结:

1、当给出reset信号后,要经过5个clk周期后wr_rst_busy与rd_rst_busy同时拉高,wr_rst_busy信号维持了17个clk周期高电平,rd_rst_busy维持了8个clk周期高电平;

2、1byte写入和8byte输出情况下,先写入的值会在8byte输出的高位,即为大端模式;

3、empty会在最后一个读en的下一个周期拉高;full同样是写入最后一个数据的后一个周期拉高。

ram仿真的目的:

1、1byte写入8byte输出模式下,输出的大小端;

2、rst的作用;

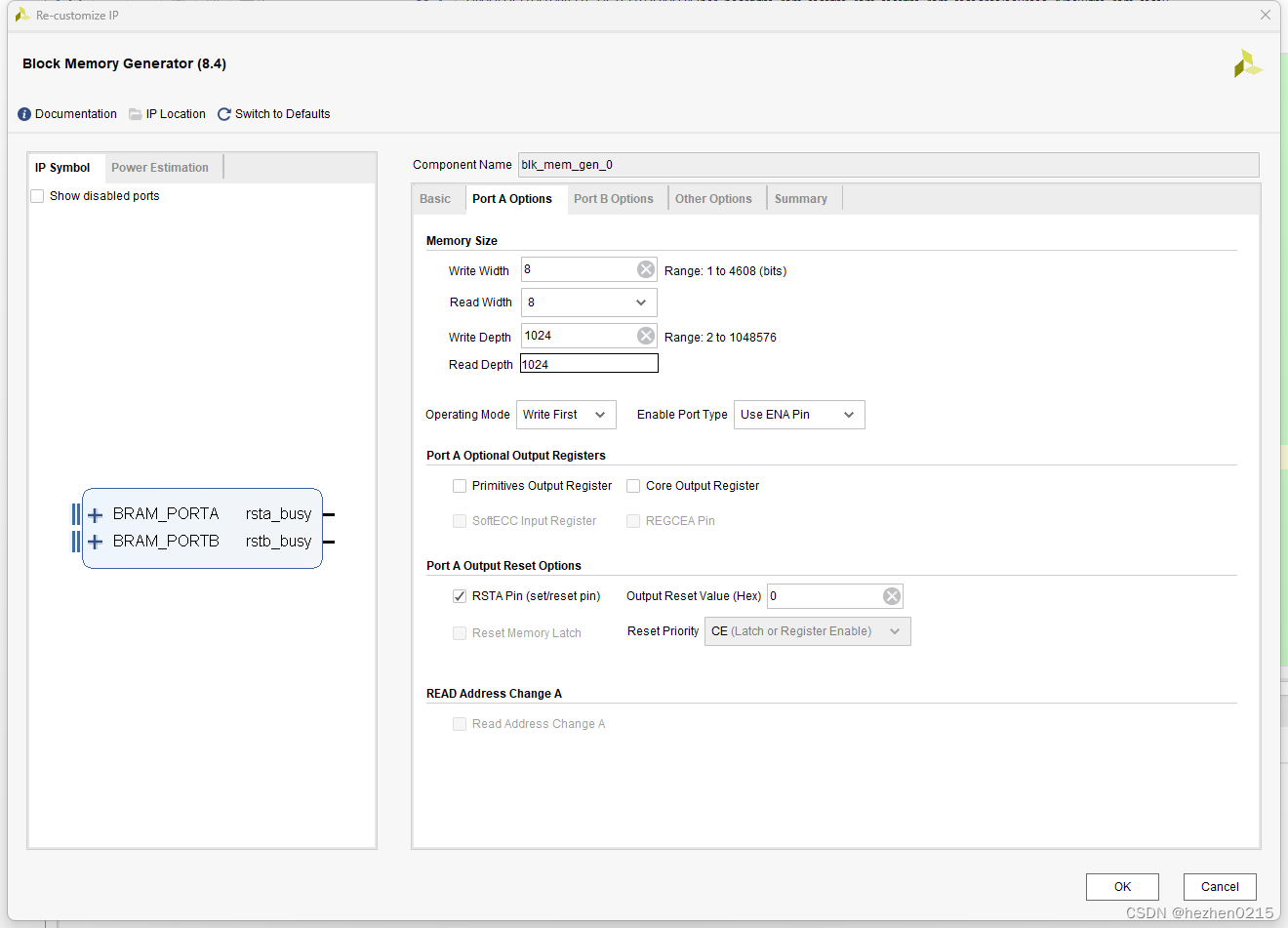

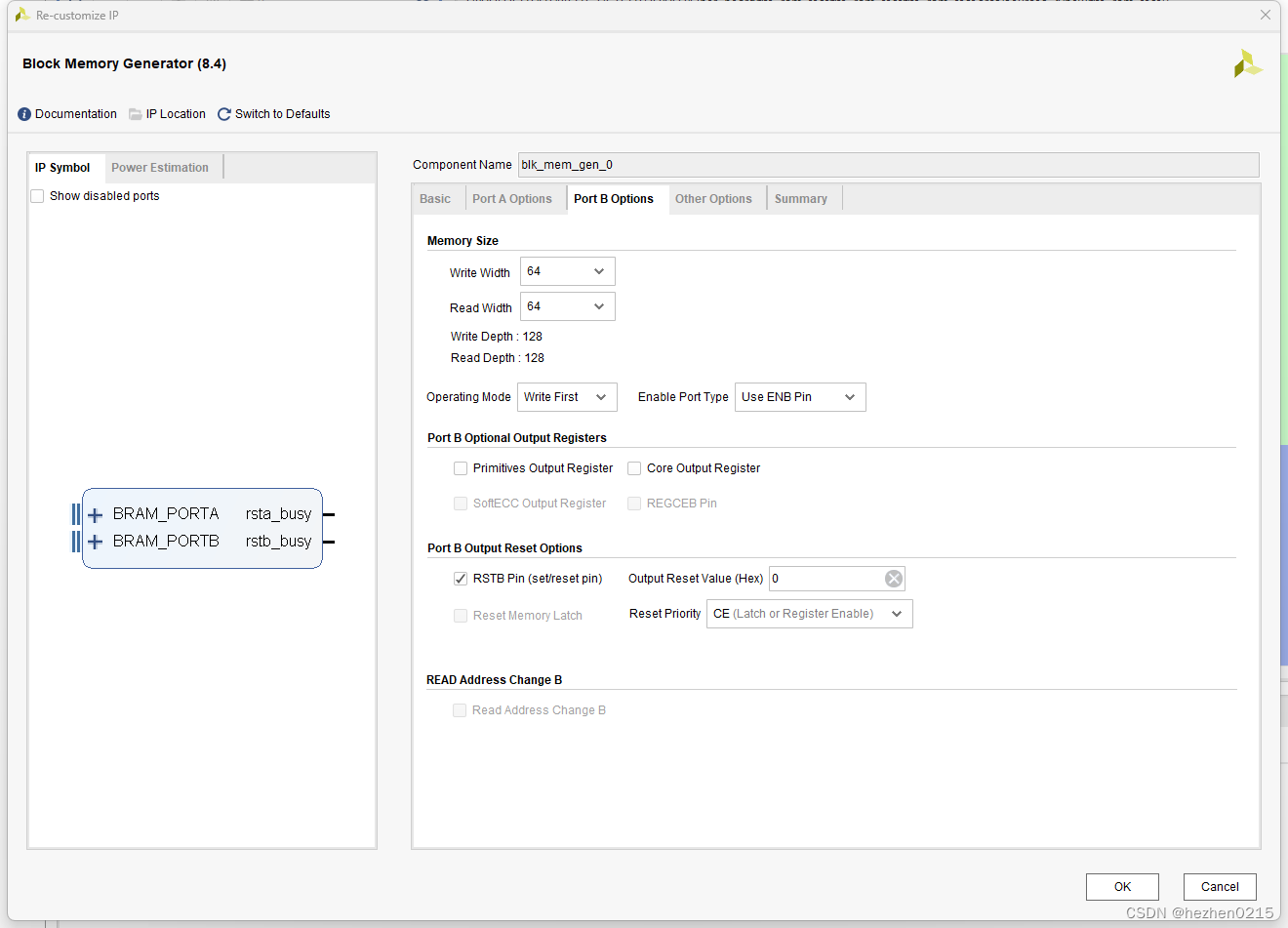

双口ram的配置如下图:

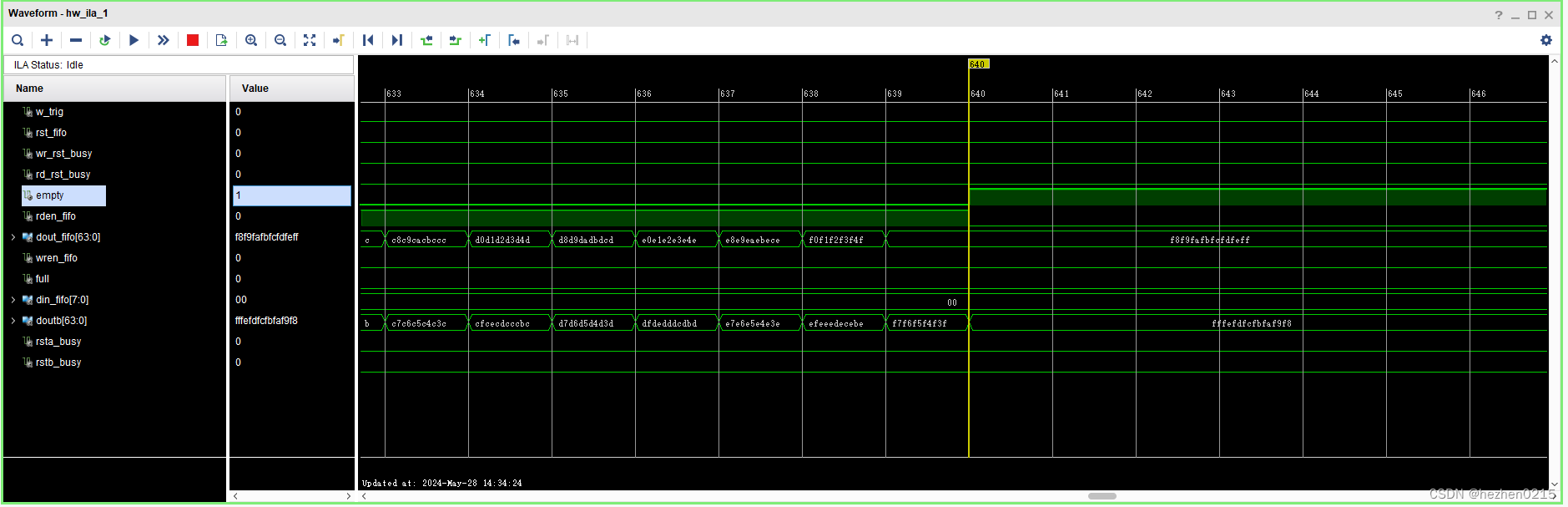

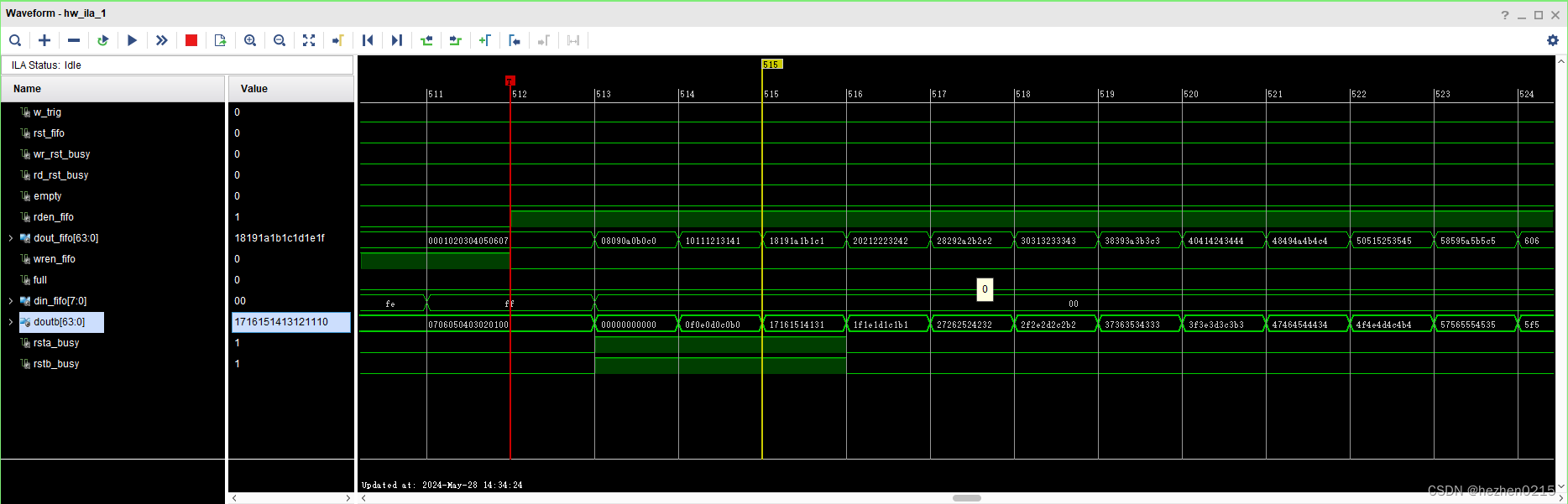

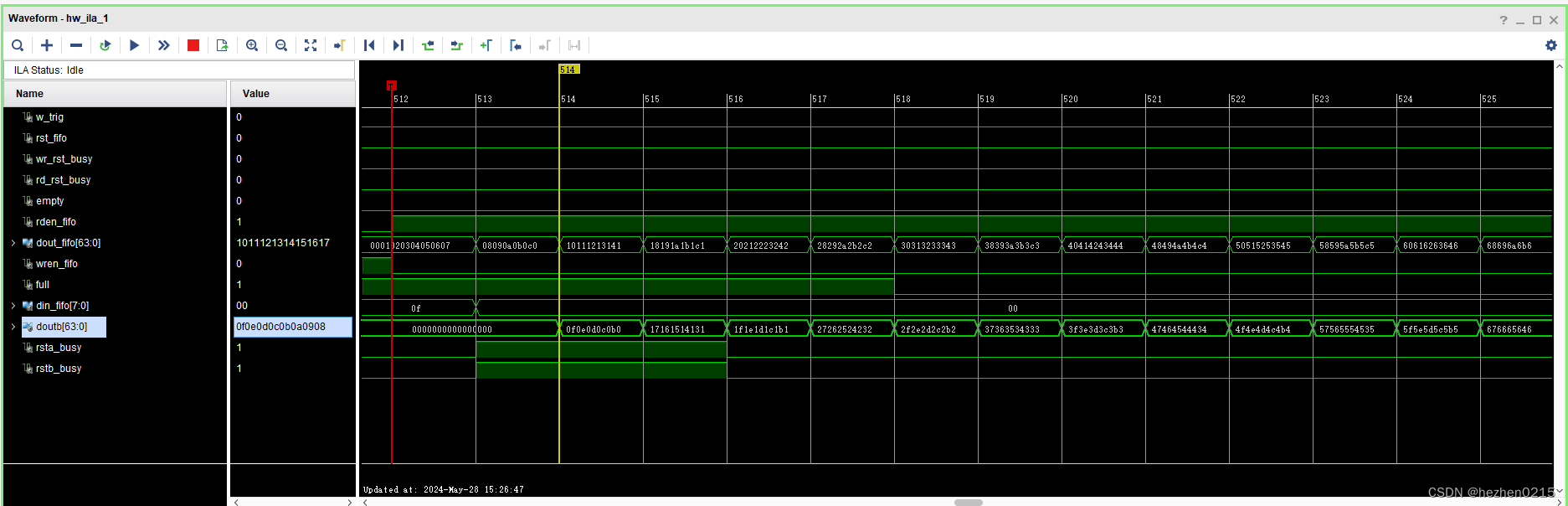

双口ram的仿真结果如下:

双口ram的仿真总结:

1、1byte写入8byte输出模式下,先写入的在输出的低byte,也就是小端模式;

2、rst后,busy会拉高并且维持3个clk周期,此期间读出数据位0.也就是rst只能复位响应端的读出,不能清空ram的所有数据,不具备claer功能。

805

805

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?