AIX-stream FIFO 实现CPU与FPGA数据流交互

基于地址形式的交互与基于流形式的交互

上周许老师说,内容我看不太懂,但是你要认真写,不然别人看不明白还不如不写。看了下,前面的确实很笼统,接下来按照许老师说的,认真写。

进入正题,流式传输和基于地址的传输有什么区别?

直观的看,基于地址的数据传输就像是CPU访问内存,每次访问数据都需要一个地址。基于流的数据传输方式类似于FIFO,队列的访问,每次读取会把数据“读走”,下次再读取的时候已经是下一个数据,写入也是类似。再FPGA中,流式数据传输是以时钟为驱动,加一些控制信号。stream常见的实例就是AD/DA转换,AD/DA转换器在采样时钟的驱动下,不停的产生数据流,外界根据一个ready信号来决定是否读取数据。address形式常见的例子例如MCU读取AT24C04,每次发生数据的读写都会提前设置地址。

可以看出来,基于stream的数据传输更适合批量数据的传输,基于Address的数据传输适合位置型的数据。

AXI-stream FIFO数据读写测试

AXI-stream总线读写协议

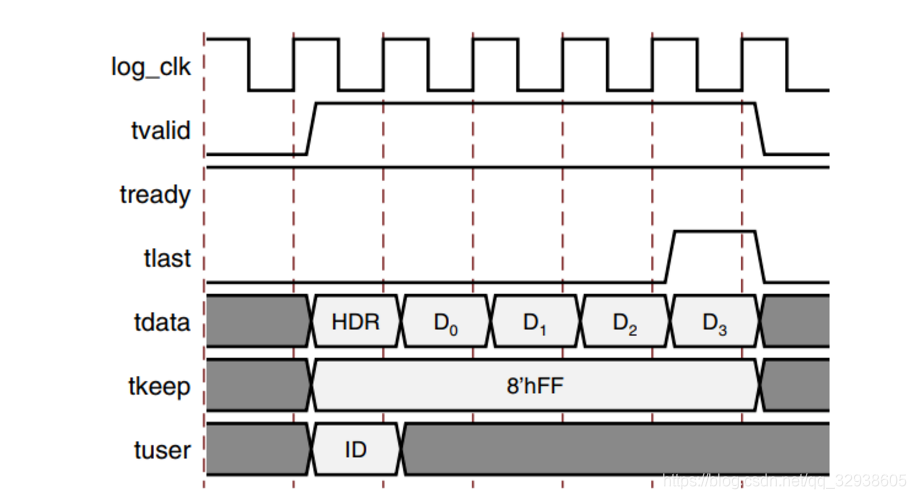

对上面的时序图进行点说明,在AXI-STREAM总线中,有两个握手信号很关键,明白了握手信号,根据这两个信号就可以进行数据的传输。

对上面的时序图进行点说明,在AXI-STREAM总线中,有两个握手信号很关键,明白了握手信号,根据这两个信号就可以进行数据的传输。

在说信号之前,先说一下AXI-stream是分为主设备和从设备的,主设备会发出clk信号和data,从设备在条件允许的情况下,进行数据的读取。

1、tvalid信号:此信号说明主机的数据已经准备好了,数据允许被从机读取。

2、tready信号:此信号是从机目前可以读取的信号,当该信号置位时说明从机准备好了读取主机的信号;

上图是我做的测试信号, 可以看出tready&tvalid1的时刻,数据开始被传输 。

上图是我做的测试信号, 可以看出tready&tvalid1的时刻,数据开始被传输 。

这种握手机制,相互确定了对方是否准备好进行数据传输,一旦双方都确认,数据传输就会开始,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1448

1448

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?