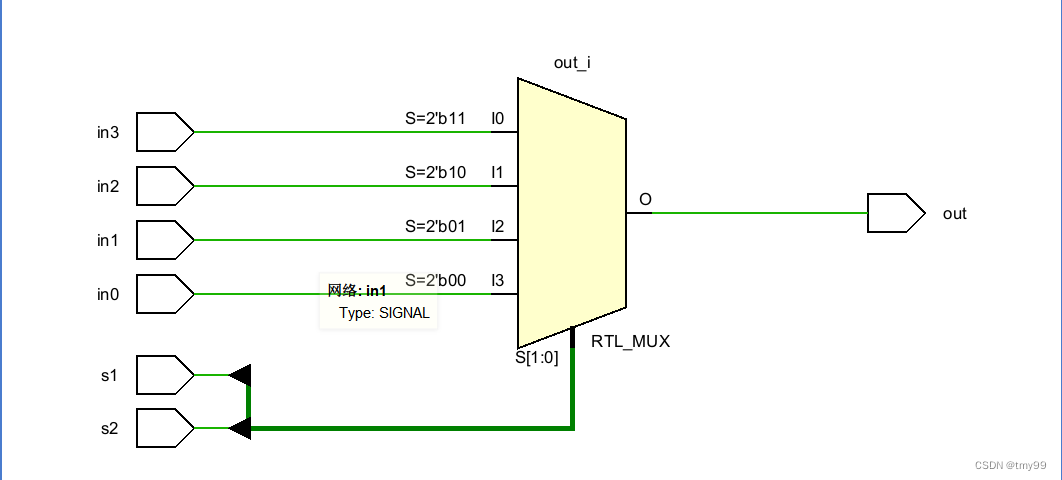

1.多路选择器

source:

module mult_select4_1(

input in0,in1,in2,in3,

intput s2,s1,

output reg out

);

always @ *

begin

case ({s2,s1})

2'b11:out = in3;

2'b10:out = in2;

2'b01:out = in1;

2'b00:out = in0;

endcase

end

endmodule仿真:

module tb(

);

wire [3:0] in;

wire [1:0] select;

wire OUT;

mult_select4_1 fun1(

.in0(in[0]),

.in1(in[1]),

.in2(in[2]),

.in3(in[3]),

.s2(select[1]),

.s1(select[0]),

.out(OUT));

initial begin

in = 4'b0101;

select = 2'b10;

OUT = 0;

end

endmodule

2.n比特大小比较器

module nbite_compare

#(parameter N = 8)//默认8位

(

input [N-1,0] in0,

input [N-1,0] in1,

output reg min,eq,max

);

always @ *

begin

min = 0;

eq = 0;

max = 0;

if (in0 < in1) min = 1;

if (in0 = in1) eq = 1;

if (in0 > in1) max = 1;

end

endmodule3.3-8译码器

module threetoeight_interpreter(

input [2:0] in,

output reg [7:0] out

);

always @*

begin

case (in)

3'b000:out = 8'b00000001;

3'b001:out = 8'b00000010;

3'b010:out = 8'b00000100;

3'b011:out = 8'b00001000;

3'b100:out = 8'b00010000;

3'b101:out = 8'b00100000;

3'b110:out = 8'b01000000;

3'b111:out = 8'b10000000;

endcase

end

endmodule4.8-3编码器

module eighttothree_code(

input [7:0] in,

output reg [2:0] out,

output reg vaild

);

always @*

begin

vaild = 1;

out = 3'b000;

case (in)

8'b00000001:out = 3'b000;

8'b00000010:out = 3'b001;

8'b00000100:out = 3'b010;

8'b00001000:out = 3'b011;

8'b00010000:out = 3'b100;

8'b00100000:out = 3'b101;

8'b01000000:out = 3'b110;

8'b10000000:out = 3'b111;

default : vaild = 0;

endcase

end

endmodule5.优先级8-3编码器

module pri_eighttothree_code(

input [7:0] in,

output reg [2:0] out,

output reg vaild

);

always @*

begin

vaild = 1;

out = 3'b000;

casez (in)

8'b1???????:out = 3'b111;

8'b01??????:out = 3'b110;

8'b001?????:out = 3'b101;

8'b0001????:out = 3'b100;

8'b00001???:out = 3'b011;

8'b000001??:out = 3'b010;

8'b0000001?:out = 3'b001;

8'b00000001:out = 3'b000;

default: vaild = 0;

endcase

end

endmodule

4688

4688

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?