多路选择器是一种数字电路组件,用于从多个输入中选择一个输出,其主要功能是根据控制信号选择某个特定的输入信号,并将其传递到输出端。这种特性使得多路选择器在多个领域都有广泛的应用。例如,它可以被用于选择存储器中的不同地址以读取或写入数据。此外,在处理器的指令执行过程中,多路选择器也能够帮助指令选择不同的操作数或执行路径,从而提高处理器的运行效率。在数据交换系统中,多路选择器可以帮助选择不同的信道进行数据传输。通过多路选择器的选择,可以实现不同用户之间的数据分发和转接,提高数据交换的效率和准确性。

多路选择器是一种组合逻辑电路,它根据选择信号从多个输入信号中选择一个输出。在4选1多路选择器中,通常有2个选择输入(足以选择4个不同的输入线),以及4个数据输入和1个数据输出。根据选择输入的不同组合,输出将是四个数据输入中的一个。

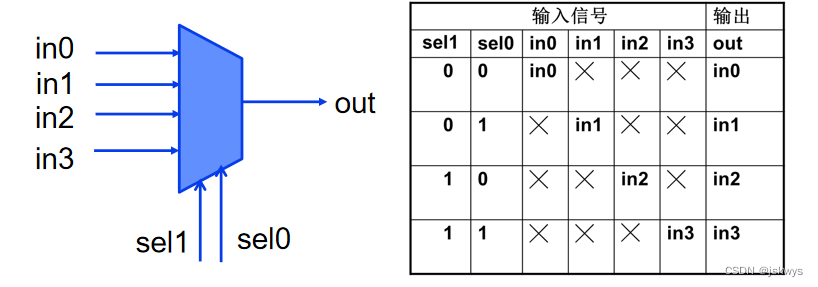

图1 4选1数据选择器符号及功能表

图1为4选1数据选择器符号及功能表。其中sel0和sel1为选择信号,in0~in3为4路输入信号。out为输出信号。当选择输入信号为00时,out输出in0,当选择输入信号为01时,out输出in1,当选择输入信号为10时,out输出in2,当选择输入信号为11时,out输出in3,从而实现四选一数据的输出。理解功能表可以进行RTL级4选1多路选择器的Verilog设计。

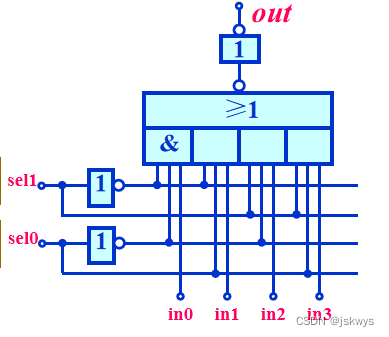

图2为4选1数据选择器逻辑电路图。逻辑电路图由与门、或非门、非门组成。理解电路原理可以进行门级4选1多路选择器的Verilog设计。

图2 4选1数据选择电路图

门级代码:

module mux4_1(out,in0,in1,in2,in3,sel);

input in0,in1,in2,in3;output out;

input wire[1:0]sel;

wire s0_n,sl_n,w,x,y,z;

not(s0_n,sel[0]),(s1_n,sel[1]);

and(w,in0,s0_n,s1_n);

and(x,in1,sel[0],s1_n);

and(y,in2,s0_n,sel[1]);

and(z,in3,sel[0],sel[1]);

or(out,w,x,y,z);

endmodule门级测试文件:

module tb_mux4_1;

reg[3:0]d;

reg[1:0]s;

wire out;

mux4_1 mymux (out,d[0],d[1],d[2],d[3],s);

initial begin

d=4'b1010;

s=2'b00;

#5 s=2'b01;

#5 s=2'b10;

#5 s=2'b11;

#5 $finish;

end

endmodulertl级代码:

module mux4_2(out,in0,in1,in2,in3,sel);

output out;

input in0,in1,in2,in3;

input[1:0] sel; reg out;

always @(in0 or in1 or in2 or in3 or sel)

case(sel)

2'b00: out=in0;

2'b01: out=in1;

2'b10: out=in2;

2'b11: out=in3;

default: out=2'bx;

endcase

endmodulertl级测试文件:

module tb_mux4_2;

reg[3:0]d;

reg[1:0]s;

wire out;

mux4_2 mymux (out,d[0],d[1],d[2],d[3],s);

initial begin

d=4'b1010;

s=2'b00;

#5 s=2'b01;

#5 s=2'b10;

#5 s=2'b11;

#5 $finish;

end

endmodule

878

878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?