最近要移植FreeRTOS操作系统,这也是个学习的过程,在此以笔记的形式记录下来。本篇文章主要是谈Cortex-M4内核中断的一些概念以及其在FreeRTOS中的使用方法,部分内容摘自《Cortex-M3权威指南(宋岩译)》,在此向作者表示感谢。

1 优先级值和逻辑优先级

首先要解释一下优先级值和逻辑优先级:在Cortex-M内核中,假如有8级优先级,我们说优先级值是0~7,但数值最大的优先级7却代表着最低的逻辑优先级。

接下来需要清楚的是,在Cortex-M4内核中,一个中断的优先级数值越低,逻辑优先级却越高。比如,中断优先级为2的中断可以抢占中断优先级为5的中断,但反过来就不行。换句话说,中断优先级2比中断优先级5的优先级更高。这是Cortex-内核最容易让人犯错之处,因为大多数的非Cortex-M内核微控制器的中断优先级表述是与之相反的。

FreeRTOS中所说的优先级均指逻辑优先级。

2 异常类型与优先级

异常类型

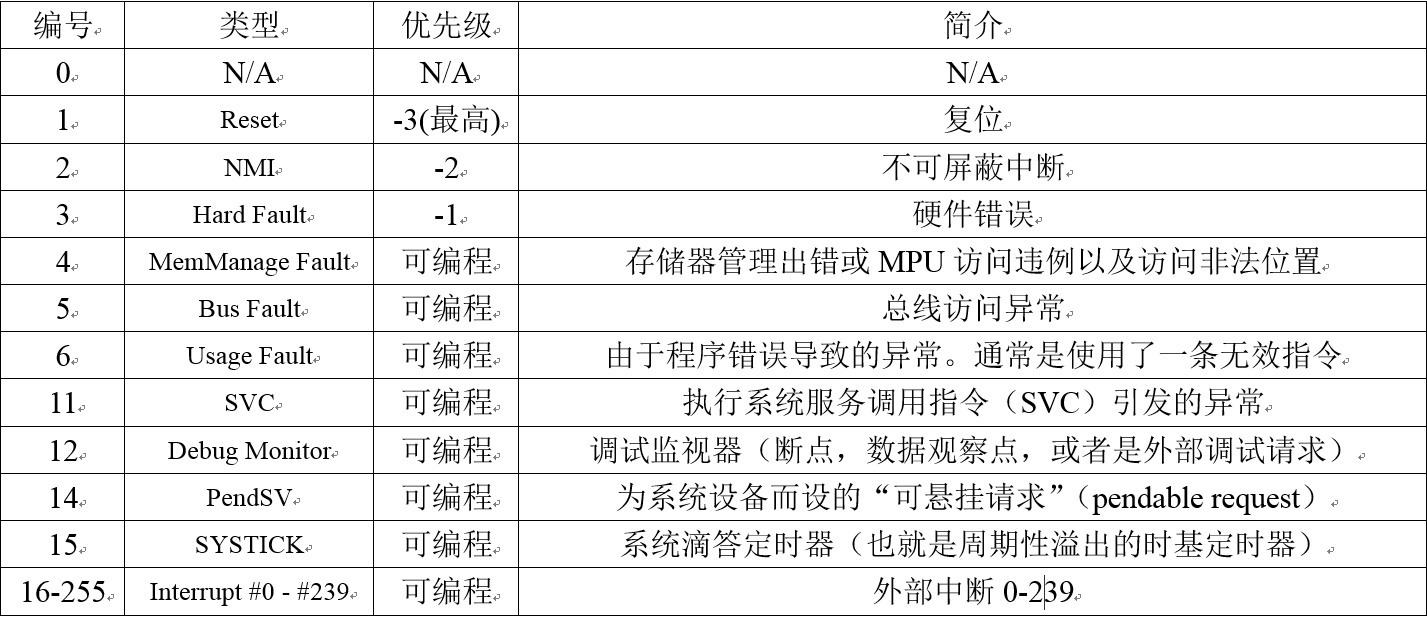

Cortex-M4内核支持众多的系统异常和外部中断。其中,编号1-15对应系统异常(没有编号为0的异常),大于等于16的则全是外部中断。除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。Cortex-M4内核异常如下。

优先级

在CM4中,优先级对于异常来说很关键的,它会决定一个异常是否能被掩蔽,以及在未掩蔽的情况下何时可以响应。优先级的数值越小,则优先级越高。CM4支持中断嵌套,使得高优先级异常会抢占(preempt)低优先级异常。有3个系统异常:复位,NMI 以及Hard Fault,它们有固定的优先级,并且它们的优先级号是负数,从而高于所有其它异常。所有其它异常的优先级则都是可编程的(但不能被编程为负数)。

中断优先级的设定是通过Interrupt Priority-Level Registers (0xE000E400-0xE000E4EF),即NVIC->IP[IRQn]寄存器,该寄存器共有240个。这些寄存器都是8位,原则上,其可支持3个固定的高优先级和多达256级的可编程优先级。但是,绝大多数CM4芯片都会精简设计,以致实际上支持的优先级数会更少,如8级、16 级、32 级等。它们在设计时会裁掉表达优先级的几个低端有效位,以减少优先级的级数,但不管使用多少位来表达优先级,都是以MSB对齐。举例来说,如果只使用了3个位来表达优先级,则NV

本文详细介绍了Cortex-M4内核中断的优先级概念,包括逻辑优先级和抢占优先级。解释了FreeRTOS中中断与优先级的关系,强调在中断服务例程中调用RTOS API的限制,以及如何设置configMAX_SYSCALL_INTERRUPT_PRIORITY和configKERNEL_INTERRUPT_PRIORITY宏以确保正确中断管理。同时,讨论了中断优先级寄存器的配置及其在FreeRTOS临界区中的作用。

本文详细介绍了Cortex-M4内核中断的优先级概念,包括逻辑优先级和抢占优先级。解释了FreeRTOS中中断与优先级的关系,强调在中断服务例程中调用RTOS API的限制,以及如何设置configMAX_SYSCALL_INTERRUPT_PRIORITY和configKERNEL_INTERRUPT_PRIORITY宏以确保正确中断管理。同时,讨论了中断优先级寄存器的配置及其在FreeRTOS临界区中的作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

425

425

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?