目录

1.算法仿真效果

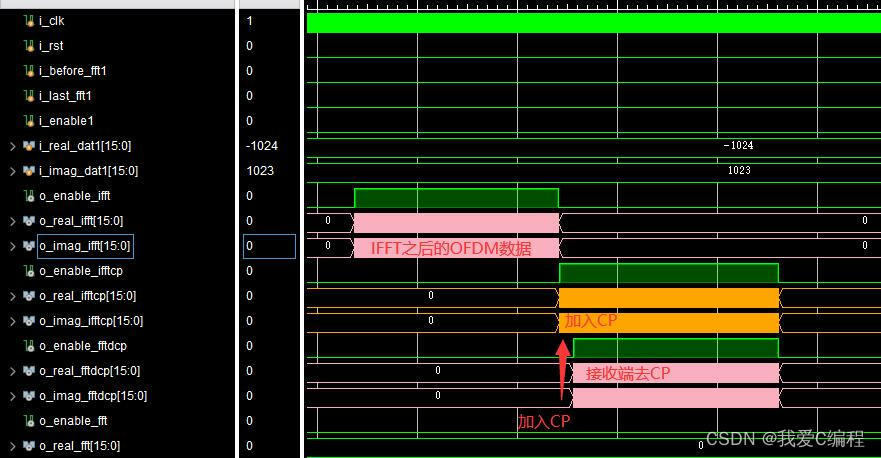

vivado2019.2仿真结果如下:

CP加入,删除效果:

系统RTL结构图:

2.算法涉及理论知识概要

正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)是一种高效的无线通信技术,已经被广泛应用于无线通信领域。OFDM技术的主要优势在于其可以有效地抵抗多径效应和频率选择性衰落,从而提高了无线通信系统的性能和可靠性。然而,OFDM系统的实现复杂度较高,需要高效的数字信号处理技术。现场可编程门阵列(Field Programmable Gate Array,FPGA)作为一种可编程逻辑器件,具有高度的灵活性和并行处理能力,非常适合实现复杂的数字信号处理算法。

2.1 OFDM原理

OFDM是一种多载波调制技术,其基本原理是将高速数据流分成若干个低速数据流,然后分别调制到一组正交的子载波上进行传输。在接收端,通过对各个子载波进行解调,可以恢复出原始的高速数据流。具体地,假设OFDM系统的子载波数量为N,符号周期为Ts,则第k个子载波的频率为fk=k/Ts。在一个符号周期内,OFDM符号可以表示为:

s(t)=∑[n=0,N-1]X[n]exp(j2πnft)(1)

其中,X[n]是第n个子载波上的调制符号,可以是QPSK、QAM等调制方式的符号。exp(j2πnft)是第n个子载波的相位旋转因子。

在接收端,通过对接收到的OFDM符号进行解调,可以恢复出各个子载波上的调制符号。具体地,第k个子载波上的解调符号可以表示为:

Y[k]=∫[t=0,Ts]r(t)exp(-j2πkft)dt(2)

其中,r(t)是接收到的OFDM符号。通过对所有子载波上的解调符号进行并串转换和解码,可以恢复出原始的高速数据流。

2.2 基于FPGA的OFDM系统设计和实现

基于FPGA的OFDM系统主要由以下几个部分组成:IFFT/FFT模块、成型滤波模块、加CP去CP模块以及控制模块。其中,IFFT/FFT模块用于实现OFDM符号的调制和解调;成型滤波模块用于对OFDM符号进行成型滤波处理;加CP去CP模块用于添加和去除循环前缀(CP),以消除多径效应引起的符号间干扰(ISI);控制模块用于控制整个系统的工作流程和数据传输。具体架构图略。

2.2.1IFFT/FFT模块设计和实现

IFFT/FFT模块是OFDM系统的核心部分之一,用于实现OFDM符号的调制和解调。IFFT(Inverse Fast Fourier Transform)用于将频域上的调制符号转换到时域上形成OFDM符号;FFT(Fast Fourier Transform)用于将接收到的时域OFDM符号转换到频域上进行解调。具体算法公式和实现方式略。

2.2.2成型滤波模块设计和实现

成型滤波模块用于对OFDM符号进行成型滤波处理以减小带外辐射并提高频谱利用率。常用的成型滤波器包括升余弦滚降滤波器、根升余弦滚降滤波器等。具体公式和实现方式略。

2.2.3加CP去CP模块设计和实现

加CP去CP模块用于添加和去除循环前缀(CP),以消除多径效应引起的符号间干扰(ISI)。在发送端添加适当长度的CP可以保证在一个符号周期内所有子载波都经历相同的信道响应从而避免ISI;在接收端去除CP可以恢复出原始的高速数据流。加入保护间隔之后基于IDFT(IFFT)的OFDM系统框图如下所示:

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/27 01:35:32

// Design Name:

// Module Name: TEST_OFDM_tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST_OFDM_tops;

reg i_clk;

reg i_rst;

reg i_before_fft1;

reg i_last_fft1;

reg i_enable1;

reg signed[15:0]i_real_dat1;

reg signed[15:0]i_imag_dat1;

wire o_enable_ifft;

wire signed[15:0]o_real_ifft;

wire signed[15:0]o_imag_ifft;

wire o_enable_ifftcp;

wire signed[15:0]o_real_ifftcp;

wire signed[15:0]o_imag_ifftcp;

wire o_enable_fftdcp;

wire signed[15:0]o_real_fftdcp;

wire signed[15:0]o_imag_fftdcp;

wire o_enable_fft;

wire signed[15:0]o_real_fft;

wire signed[15:0]o_imag_fft;

OFDM_tops OFDM_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_before_fft1 (i_before_fft1),

.i_last_fft1 (i_last_fft1),

.i_enable1 (i_enable1),

.i_real_dat1 (i_real_dat1),

.i_imag_dat1 (i_imag_dat1),

.o_start_ifft (),

.o_ends_ifft (),

.o_enable_ifft (o_enable_ifft),

.o_real_ifft (o_real_ifft),

.o_imag_ifft (o_imag_ifft),

.o_start_ifftcp (),

.o_ends_ifftcp (),

.o_enable_ifftcp (o_enable_ifftcp),

.o_real_ifftcp (o_real_ifftcp),

.o_imag_ifftcp (o_imag_ifftcp),

.o_start_fftdcp (),

.o_ends_fftdcp (),

.o_enable_fftdcp (o_enable_fftdcp),

.o_real_fftdcp (o_real_fftdcp),

.o_imag_fftdcp (o_imag_fftdcp),

.o_start_fft (),

.o_ends_fft (),

.o_enable_fft (o_enable_fft),

.o_real_fft (o_real_fft),

.o_imag_fft (o_imag_fft)

);

reg [15:0]cnts;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts <= 16'd0;

i_real_dat1 <= 16'b1111110000000000;

i_imag_dat1 <= 16'b0000001111111111;

end

else begin

if(i_enable1 == 1'b1)

begin

cnts <= cnts+16'd1;

if(cnts>=16'd200 & cnts<=16'd1848)

begin

i_real_dat1 <= ~i_real_dat1;

if (cnts[0]==1'b1)

i_imag_dat1 <= ~i_imag_dat1;

else

i_imag_dat1 <= i_imag_dat1;

end

end

else begin

cnts <= 16'd0;

i_real_dat1 <= 16'b1111110000000000;

i_imag_dat1 <= 16'b0000001111111111;

end

end

end

reg [19:0]cnts2;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts2 <= 20'd0;

i_before_fft1<=1'b0;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

else begin

if(cnts2==20'd25000)

cnts2 <= 20'd0;

else

cnts2 <= cnts2 + 20'd1;

if(cnts2==20'd0)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd1)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd2)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd3)

begin

i_before_fft1<=1'b1;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd4)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

if(cnts2>=20'd5 & cnts2<=20'd4+2047)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b1;

i_last_fft1 <=1'b0;

end

if(cnts2==20'd4+2048)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b1;

i_last_fft1 <=1'b1;

end

if(cnts2>20'd4+2048)

begin

i_before_fft1<=1'b0;

i_enable1 <=1'b0;

i_last_fft1 <=1'b0;

end

end

end

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

#2000

i_rst = 1'b0;

end

always #10 i_clk=~i_clk;

endmodule

00_053m4.完整算法代码文件获得

V

3944

3944

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?