目录

1.算法描述

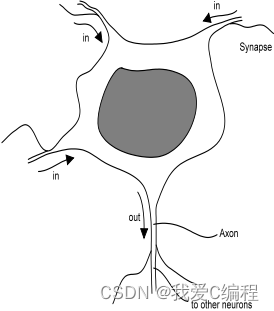

神经网络主要由处理单元、网络拓扑结构、训练规则组成。处理单元是神经网络的基本操作单元,用以模拟人脑神经元的功能。一个处理单元有多个输入、输出,输入端模拟脑神经的树突功能,起信息传递作用;输出端模拟脑神经的轴突功能,将处理后的信息传给下一个处理单元,如图1.1所示。

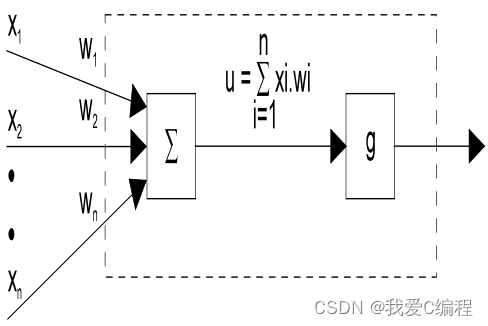

基本的神经处理单元其等效于人体的神经元,如图2所示,

=>

=>

具有相同功能的处理单元构成处理层。常用的多层感知机由输入层、输出层和若干隐含层组成,神经网络的拓扑结构决定了各处理单元、各层之间信息的传递方式与途径。训练规则利用转换函数进行数据处理的加权及求和,训练网络系统进行模式识别,并将其转换成潜在的输出值。神经网络的基本出发点,就是通过简单函数的多次迭代,实现对复杂映射的拟合和逼近。神经网络能够实现一对一、一对多的映射关系。因此,许多实际问题都可以用神经网络模型来解决。

神经网络的工作过程主要由两个阶段组成,一个阶段是学习期,即训练阶段,此时连接权值可调整,另一个阶段就是工作期,此时,其各个权值固定。

在学习阶段,训练集中已知类别的输入向量将随机输入给神经网络,每次的输入使得PE之间的连接权重根据一种固定的学习规则得到细致的调整,使得网络的输出向正确的方向转变。随着训练过程的推进,网络的性能得到的改善,直到网络中每一个PE都收敛到合适的权重为止。

在神经网络的学习阶段,当网络做出错误的判决的时候,那么通过神经网络的学习,应使得网络减少下次犯同样错误的可能性,通常情况下,系统将会给网络一个随机的权值,然后将信号输入到神经网络,网络将输入的模式进行加权求和、并与门限进行比较,然后进行非线性运算从而得到网络的输出。这个时候系统输出正确和错误的概率是相同的,那么这个时候,系统将正确的输出结果的连接权值增大,从而使下次输入同一个信号的时候,得到正确的输出结果。

通常情况下,按这种方法学习几次后,神经网络将判断的正确率大大提高,一般来说,网络中所含的神经元个数就越多,那么它能够记忆和识别的模式也越多。

当训练结束进入工作期时,权重系数保持不变,此外神经网络的输入是未知类别的向量,输入的信息经过神经元层层传播,最后在输出层上产生输出向量,根据此输出向量可以将对象划分到某一类中,从而实现对象的模式识别。

以上就是神经网络的基本工作过程。

————————————————

BP神经网络主要由输入层,隐含层以及输出层三个部分构成。

来自外界的信息通过输入层传输进入到隐含层进行处理,并由输出层输出处理结果。当BP神经网络的输出结果和其期望结果之间的误差较大的时候,则进入反向传播阶段,并进行进行审计网络权值的修正,直到输出结果和期望结果误差满足一定条件为止。

其中,信号的前向传播过程的主要步骤如下:

其中激活函数

采用查找表方法计算得到:

module fx1(

clk,

rst,

net,

fx

);

input clk;

input rst;

input[8:0]net;

output[8:0]fx;

reg [8:0]fx;

always @(posedge clk)

begin

if(!rst)

fx<=9'd0;

else begin

case(net) //查找结果

1:fx<=9'd0;

2:fx<=9'd2;

3:fx<=9'd5;

4:fx<=9'd7;

5:fx<=9'd10;

6:fx<=9'd12;

7:fx<=9'd15;

8:fx<=9'd17;

9:fx<=9'd20;

10:fx<=9'd23;

…………………….

511:fx<=9'd505;

512:fx<=9'd505;

default:fx<=9'd0;

endcase

end

end

endmodule

2.仿真效果预览

matlab2022a

vivado2019.2

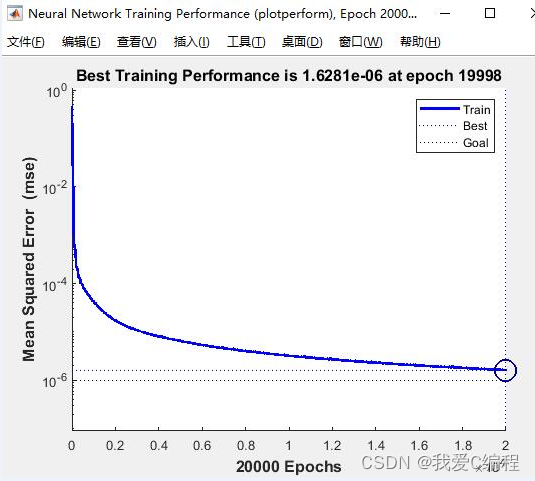

仿真结果如下:

A对应65,B对应66.。。。

错误率为:1个。总共检测23个。所以正确率为95.5%

3.verilog核心程序

% 将数据归一化

[pn,minp,maxp,tn,mint,maxt] = premnmx(X, Y);

% 隐层第一层节点数

NodeNum1 = 50;

% 隐层第二层节点数

NodeNum2 = 30;

% 输出维数

TypeNum = 1;

TF1 = 'tansig';

TF2 = 'tansig';

TF3 = 'tansig';

bp_train = newff(minmax(pn), [NodeNum1,NodeNum2,TypeNum], {TF1 TF2 TF3}, 'traingdx');

% 网络创建

bp_train.trainParam.show = 50;

% 训练次数设置

bp_train.trainParam.epochs = 20000;

% 训练所要达到的精度

bp_train.trainParam.goal = 1e-6;

% 学习速率

bp_train.trainParam.lr = 0.05;

% 训练

bp_train = train(bp_train, pn,tn);..........................................................

//feature

ABCD_signal ABCD_signal_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.i_sel (i_sel),

.o_feature2(o_feature)

);

//BP

wire signed[8:0] O1;

wire signed[8:0] O2;

wire signed[8:0] O3;

wire signed[8:0] O4;

BP_PRO BP_PRO_u(

.clk (i_clk),

.rst (i_rst),

.X (o_feature),

//16

.sda11(16'd20550),

.sda12(16'd10553),

.w11t (16'd45002),

.w12t (16'd46211),

.w13t (16'd32112),

.w14t (16'd34522),

.w25t (16'd10552),

.w26t (16'd40553),

.w27t (16'd10112),

.w28t (16'd30452),

//8

.SDA1 (8'd112),

.SDA2 (8'd67),

.SDA3 (8'd211),

.SDA4 (8'd92),

.W11 (8'd132),

.W12 (8'd112),

.W21 (8'd122),

.W22 (8'd172),

.W31 (8'd132),

.W32 (8'd202),

.W41 (8'd172),

.W42 (8'd202),

.O1 (O1),

.O2 (O2),

.O3 (O3),

.O4 (O4)

);

//Output

check_out check_out_u(

.i_clk(i_clk),

.i_rst(~i_rst),

.i_o1(O1),

.i_o2(O2),

.i_o3(O3),

.i_o4(O4),

.o_o (o_checkout)

);

//计算正确率

cal_error cal_error_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.i_regresult(o_checkout),

.o_check_clk(o_check_clk),

.o_check_count(o_check_count),

.o_error (o_error),

.o_correct (o_correct)

);

05_053_m4.完整verilog

V

4055

4055

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?