FPGA IP 源码解密

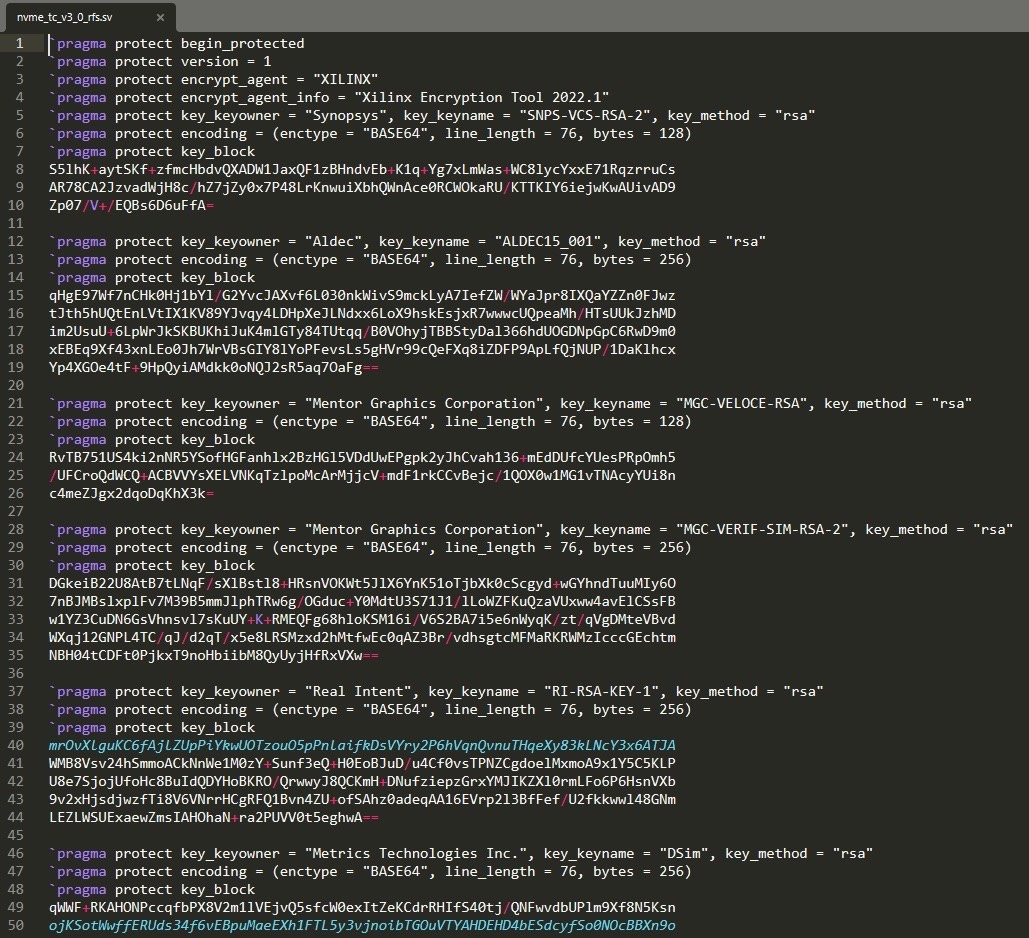

Xilinx Vivado各版本(最新版本2022.1)加密的IP文件解密复原为Verilog或者VHDL源码

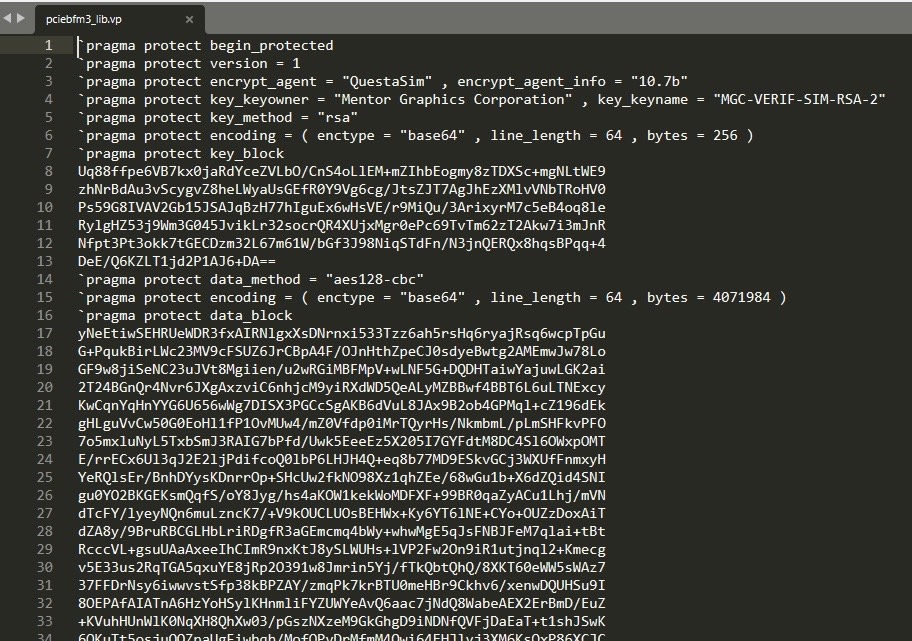

Modelsim可以编译仿真的vp加密文件均可以解密复原为Verilog或者VHDL源码

符合P1735格式保护的代码基本都可以解密还原源代码

ID:68888686908339284

s***3

FPGA IP 源码解密:保护知识产权与技术逆向分析

摘要:

随着信息技术的快速发展,FPGA(Field-Programmable Gate Array)成为了硬件设计领域中的重要工具之一。然而,在FPGA设计中,保护知识产权成为了一项重要的议题。本文将围绕Xilinx的Vivado软件及其加密功能展开,探讨FPGA IP源码解密的方法与技术。根据最新版本2022.1,我们将深入介绍如何解密复原被加密的IP文件,并还原为Verilog或VHDL源码。同时,我们还将讨论如何使用Modelsim来编译仿真vp加密文件,并实现解密还原的过程。此外,我们还将探讨符合P1735格式保护的代码的解密方法,以便更好地保护和利用FPGA的知识产权。

-

引言

在当今数字时代,知识产权保护尤为重要。对于FPGA设计领域而言,保护其知识产权同样至关重要。然而,为了保护知识产权,开发者们往往会使用各种加密技术来加密其FPGA IP源码,以防止未经授权的访问和使用。Xilinx的Vivado软件为用户提供了强大的加密功能,使得FPGA IP的保护变得更加安全可靠。然而,对于一些特定的需求,我们有时需要将加密的IP文件解密复原为Verilog或VHDL源码,以便进行修改、调试或重新设计。本文将介绍如何实现这一目标。 -

Xilinx Vivado的IP文件加密与解密

Xilinx Vivado是业界知名的FPGA设计工具,其强大的加密功能得到了广大开发者的肯定。在Vivado中,开发者可以针对自己的IP核进行加密,以确保其知识产权的安全。然而,对于一些特殊需求,我们需要对这些加密的IP文件进行解密复原,以便进行进一步的修改和优化。在最新版本2022.1中,Xilinx引入了一种解密复原机制,使得我们可以将加密的IP文件还原为Verilog或VHDL源码。通过使用这种机制,开发者可以更加灵活地使用FPGA IP,并保护其知识产权。 -

使用Modelsim编译与仿真加密的VP文件

除了Xilinx Vivado的解密复原功能外,我们还可以通过使用Modelsim进行编译和仿真加密的VP文件。Modelsim是一款业界领先的仿真工具,被广泛应用于硬件设计和验证领域。通过对加密的VP文件进行编译和仿真,我们可以获取其对应的仿真结果,并结合其他分析工具进行进一步的解密工作。基于这些仿真结果,我们可以逐步还原出加密的VP文件的Verilog或VHDL源码,为后续设计和优化提供了有力的支持。 -

符合P1735格式保护的代码的解密方法

P1735是一种常见的FPGA IP保护格式,具有防止非法访问和使用的功能。然而,对于符合P1735格式保护的代码,我们仍然可以通过一些特定的解密方法来还原其源代码。通过深入研究P1735格式的特性和机制,我们可以分析和提取其中的加密信息,从而还原出原始的Verilog或VHDL源码。这为我们保护和利用FPGA的知识产权提供了更多的选择和可能性。 -

结论与展望

本文主要探讨了FPGA IP源码解密的方法与技术,并围绕Xilinx Vivado软件及其加密功能展开了讨论。我们介绍了如何利用Vivado最新版本2022.1的解密复原机制,将加密的IP文件解密还原为Verilog或VHDL源码。同时,我们还探讨了使用Modelsim编译以及仿真加密的VP文件的方法,以及针对符合P1735格式保护的代码的解密方法。通过这些方法和技术,我们可以更好地保护和利用FPGA的知识产权,促进数字时代的创新与发展。

参考文献:

[1] Xilinx Inc. Vivado Design Suite User Guide: Programming and Debugging (UG908). Xilinx, Inc., 2022.

[2] Modelsim User Manual. Mentor Graphics Corporation, 2022.

[3] P1735 Standard for Embedded Security in IP (SPIRIT Consortium). IEEE Computer Society, 2010.

相关的代码,程序地址如下:http://fansik.cn/686908339284.html

240

240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?