前言

将静态rtl中的595控制模块复制到动态rtl文件夹中,即完成595控制模块的复用。

一、代码

module top_seg_595

(

input wire sys_clk , //系统时钟,频率50MHz

input wire sys_rst_n , //复位信号,低电平有效

output wire stcp , //输出数据存储寄时钟

output wire shcp , //移位寄存器的时钟输入

output wire ds , //串行数据输入

output wire oe //输出使能信号

);

wire [19:0] data ;

wire [5:0] point ;

wire seg_en ;

wire sign ;

generat

#(

.CNT_MAX(23'd999_999),

.DATA_MAX(20'd999_999)

)

generat_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n),

.data (data ),

.point (point ),

.seg_en (seg_en ),

.sign (sign )

);

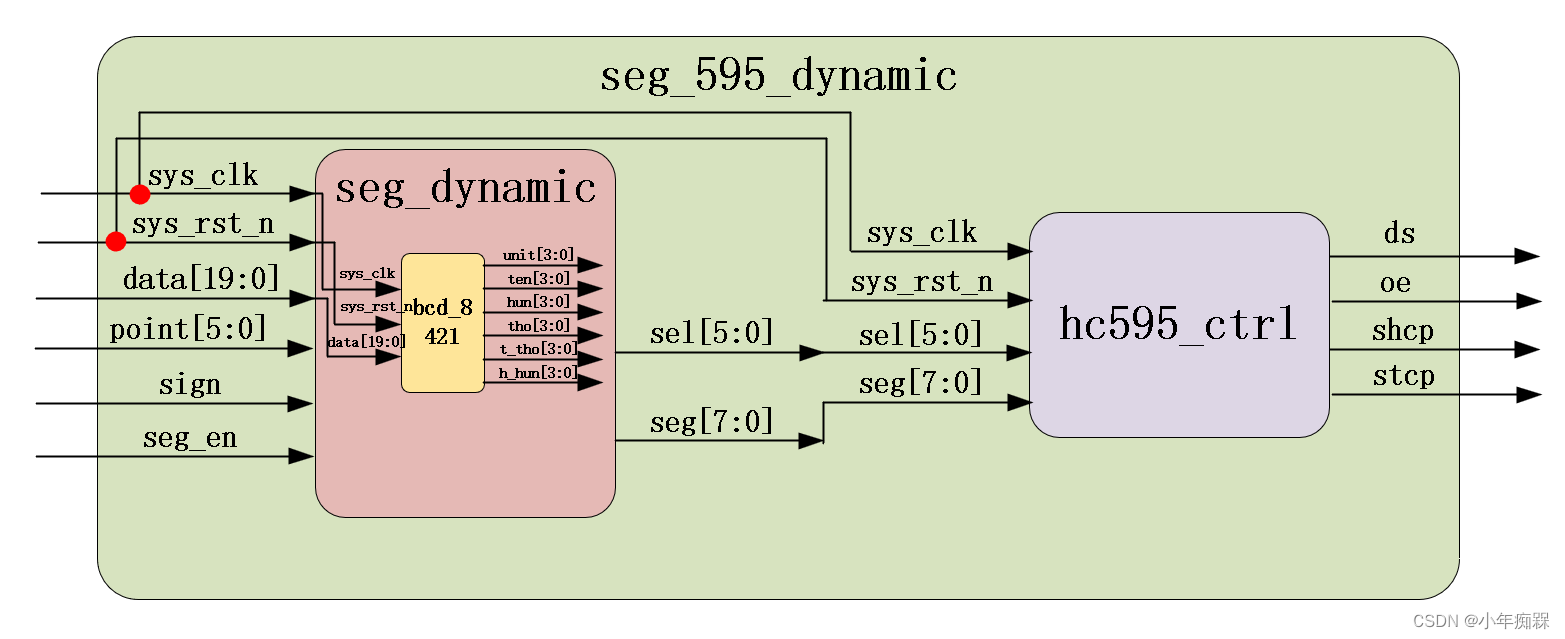

seg_595_dynamic seg_595_dynamic_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.data (data ),

.point (point ),

.seg_en (seg_en ),

.sign (sign ),

.stcp (stcp ),

.shcp (shcp ),

.ds (ds ),

.oe (oe )

);

endmodule

二、仿真代码

`timescale 1ns/1ns

wire stcp ;

wire shcp ;

wire ds ;

wire oe ;

reg sys_clk ;

reg sys_rst_n ;

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#30

sys_rst_n <= 1'b1;

end

//clk:产生时钟

always #10 sys_clk <= ~sys_clk;

//重新定义参数值,缩短仿真时间

defparam top_seg_595_inst.seg_595_dynamic_inst.seg_dynamic_inst.CNT_MAX=19;

defparam top_seg_595_inst.data_gen_inst.CNT_MAX = 49;

top_seg_595 top_seg_595_inst

(

.sys_clk (sys_clk ), //系统时钟,频率50MHz

.sys_rst_n (sys_rst_n ), //复位信号,低电平有效

.stcp (stcp ), //输出数据存储寄时钟

.shcp (shcp ), //移位寄存器的时钟输入

.ds (ds ), //串行数据输入

.oe (oe ) //输出使能信号

);

endmodule

5159

5159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?