前言

RAM是随机存取存储器(Random Access Memory)的简称,是一个易失性存储器;其工作时可以随时对任何一个指定的地址写入或读出数据。这是ROM所并不具备的功能。

ROM ip核使用时首先使用mif或hex进行初始化,将其模拟为非易失性存储器,只能对内部数据进行读取。

Altera推出的ip核分为单端口RAM和双端口RAM,双端口RAM ip核分为简单双端口RAM ip(一个端口只能读,另一个只能写)核和真正双端口RAM ip核(两个端口都能进行数据的读写)。

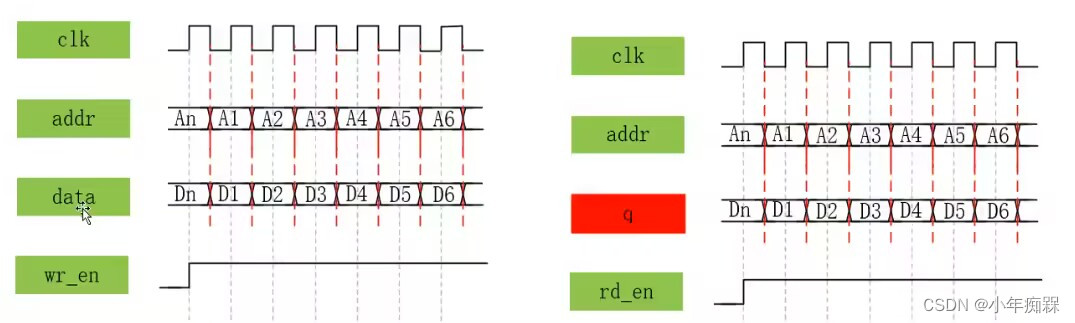

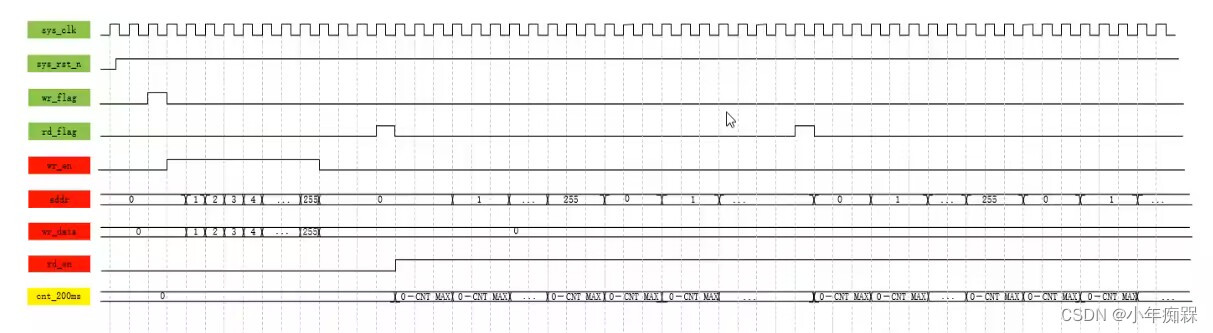

该图表示RAM读写的基本操作。

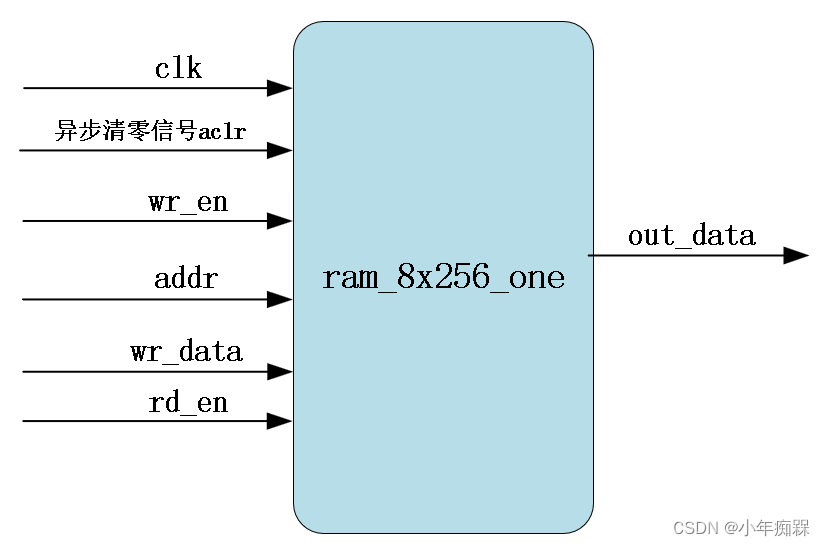

一、单端口RAM IP核功能介绍

1.data是数据写入端口;

address被数据读操作和数据写操作共用,即读写操作不能同时进行;

2.wren写使能信号高电平有效;

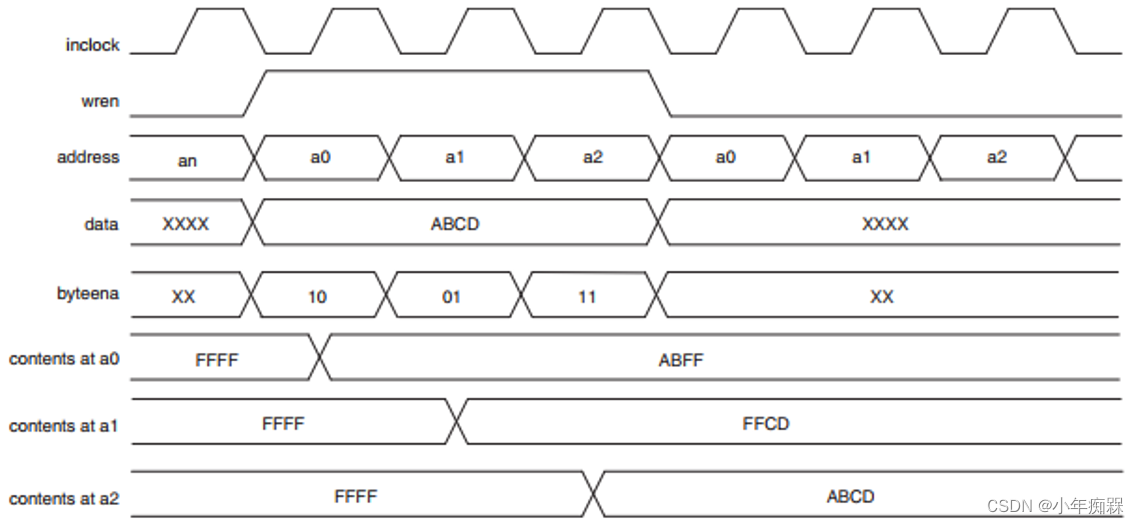

3.byteena字节使能信号充当数据掩码的作用,10读高位AB,01读低位CD,11全读为ABCD;

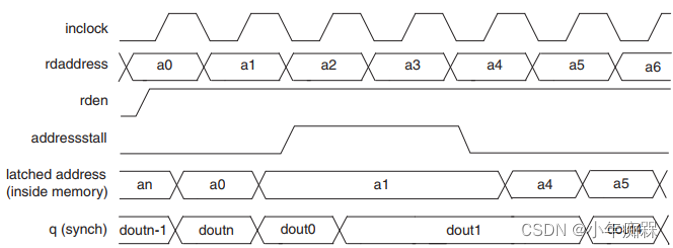

4.addressstall地址时钟使能信号:锁定当前写入的信号;

5.时钟输入端口inclock,单端口RAM ip核有两种时钟模式,一种是单时钟,此时数据的输入输出只使用inclock这一个端口;另一个模式是双时钟,输入输出各有一个端口。

6.时钟使能信号clockena,为有效高电平时输入的时钟才有效;

7.读使能信号rden;

8.异步清零信号aclr;

9.读数据输出q。

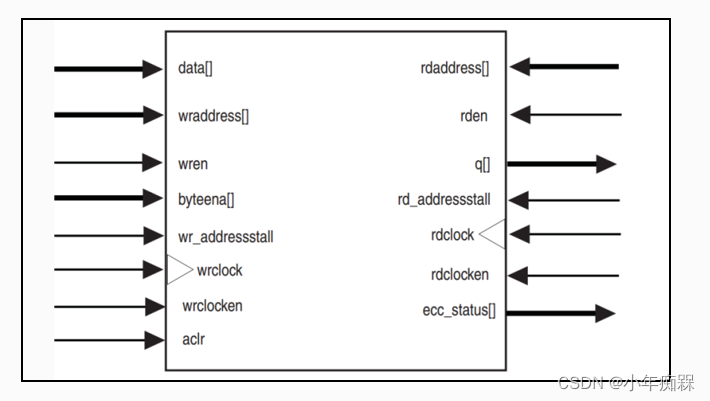

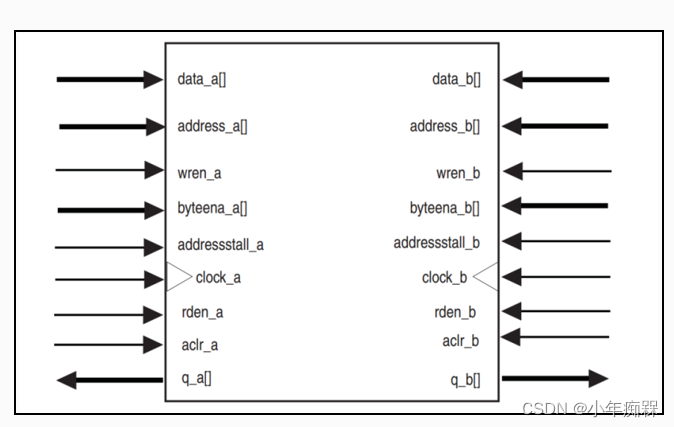

二、双端口RAM IP核

简单双端口RAM IP核:

左侧是写端口,右侧是读端口。

真正双端口RAM IP核:

左边是a组端口,右边是b组端口。

无论是简单双端口RAM IP核,还是真正双端口RAM IP核,都使用RAM:2-PORT。

二、实验框图及波形图设计

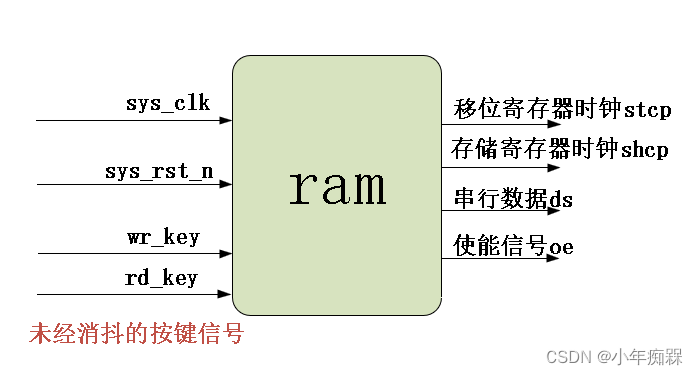

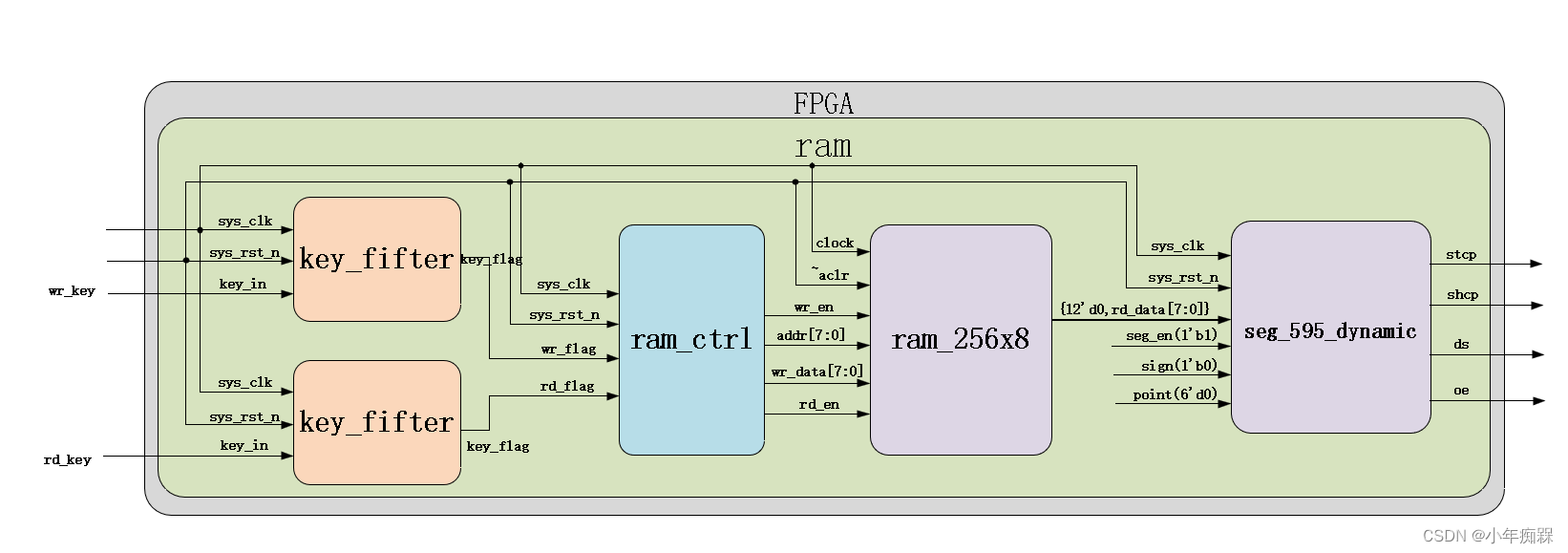

顶层模块框图:

子功能模块划分——首先需要对未消抖的模块进行消抖处理(同rom),消抖后的模块作为输入信号需要传入ram_ctrl模块(控制ram ip核的数据写入以及数据的读取):

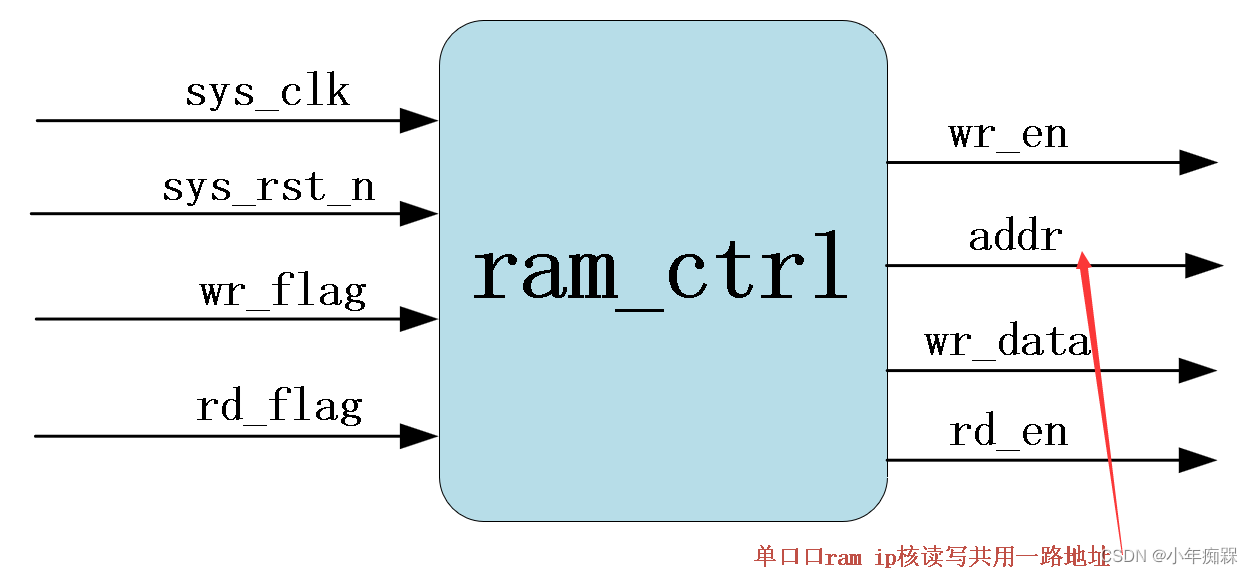

ram_ctrl模块输出的信号需要传入ip核,这里使用一个框图表示ip核:

读出的数据需要传入数码管动态显示模块进行数据的显示(同rom)。

系统框图:

1.复位信号低电平有效,复位清零信号高电平有效,故对复位信号取反传入(加反相器)。

2.8位宽传20位宽要补12个零。

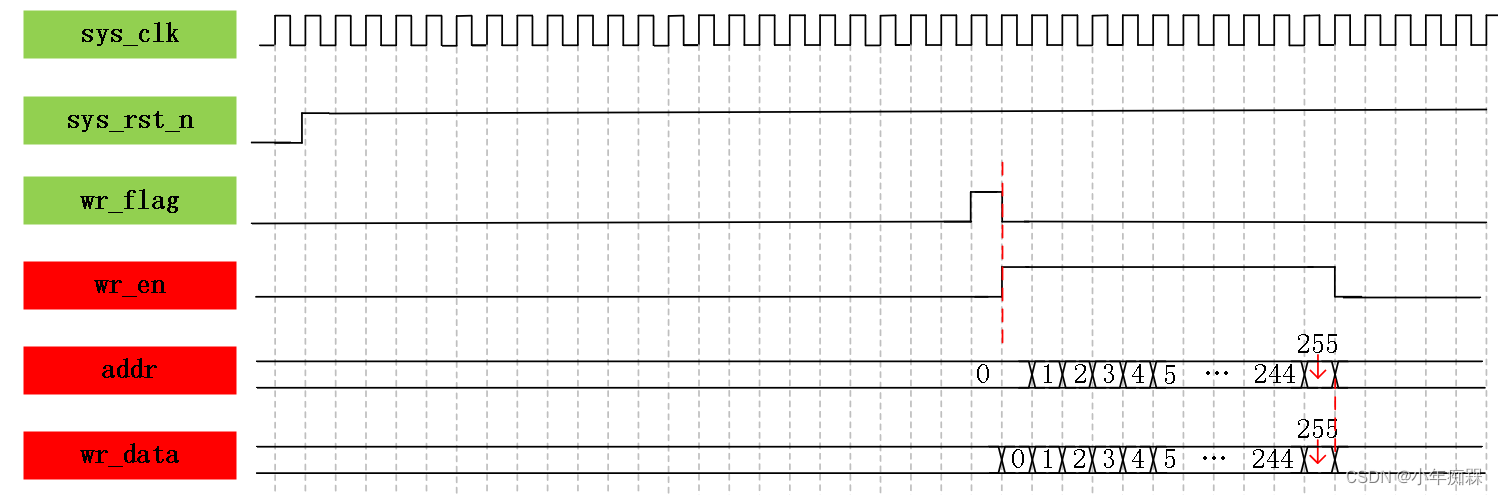

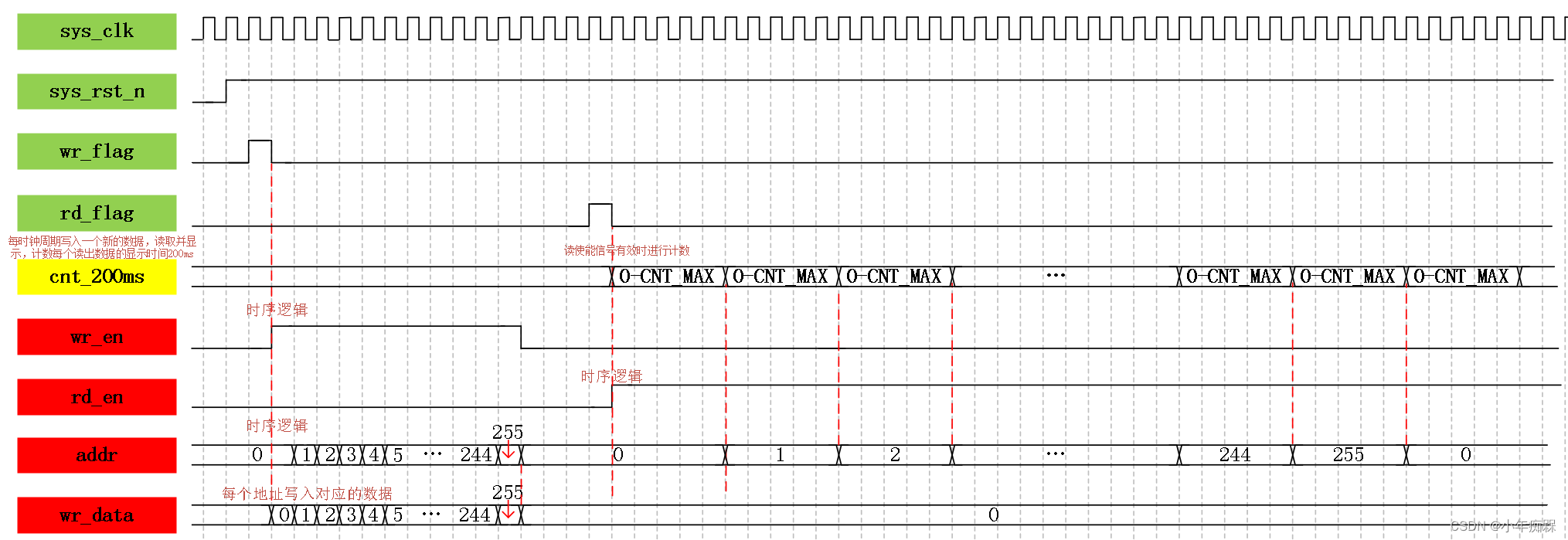

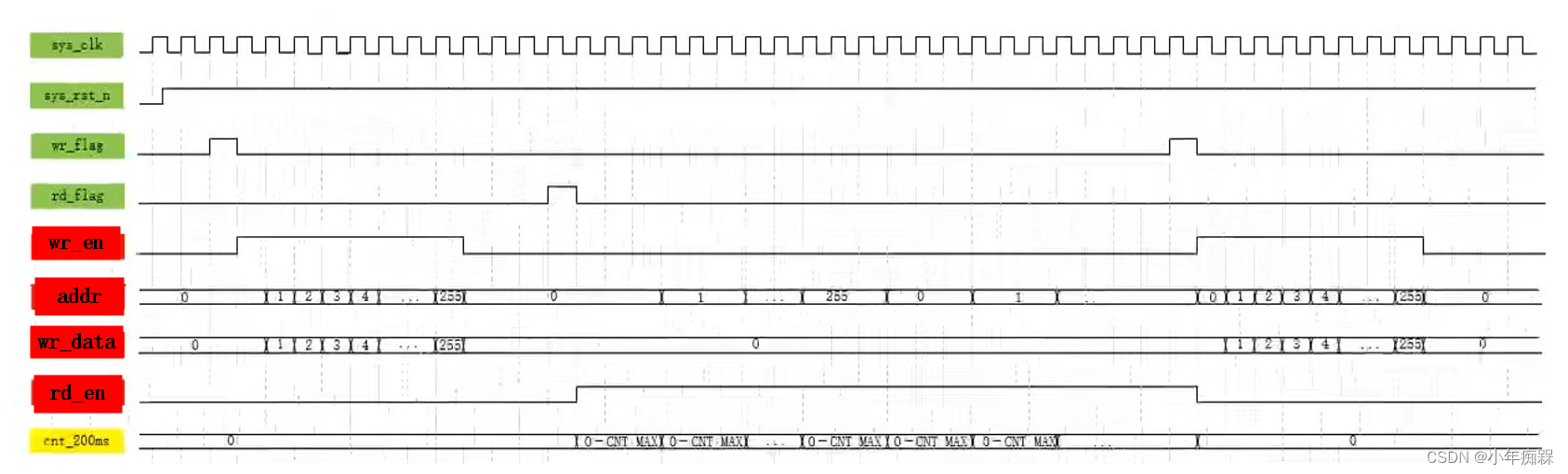

波形图:

数据写入部分:

数据读取部分:

当读数据时按下写数据:

当读数据时按下读数据:重新计数。

三、代码

rtl代码:

module ram_ctrl

(

input wire sys_clk,

input wire sys_rst_n,

input wire wr_flag,

input wire rd_flag,

output reg wr_en,//always

output reg [7:0] addr,//always

output wire [7:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

460

460

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?