一、IP核的定义

IP(Intellectual Property)即知识产权。在半导体产业将IP核定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。简而言之,这里的IP即电路功能模块。

在数字电路中,将常用的且比较复杂的功能模块(FIFO RAM SDRAM)设计成参数可修改的模块,让其他用户可以直接调用这些模块,这就是IP核。

二、IP核的意义

随着FPGA的规模越来越大,它的设计也是越来越复杂。随着设计规模增大,复杂度提高,使用 IP 核可以提高开发效率,减少设计和调试时间,加速开发进程,降低开发成本,是业界的发展趋势。

三、IP核的分类(分类依据:产品交付方式)

-

HDL语言形式 —

软核

硬件描述语言;可进行参数调整、复用性强;布局、布线灵活;设计周期短、设计投入少 -

网表形式 —

固核

完成了综合的功能块;可预布线特定信号或分配特定的布线资源 -

版图形式 —

硬核

硬核是完成提供设计的最终阶段产品—掩膜Mask;

缺乏灵活性、可移植性差;更易于实现IP核的保护。

四、IP核的缺点

- IP核往往不能跨平台使用

- IP核不透明,看不到内部核心代码

- 定制IP需额外收费

五、Altera IP核的分类

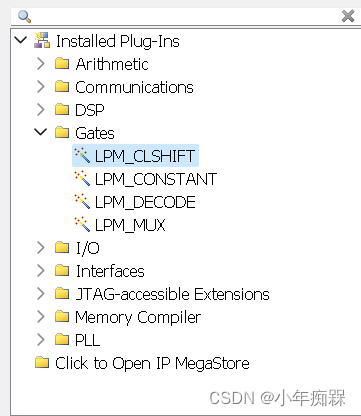

Altera提供的IP核如下:

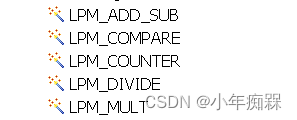

首先第一大类是数学运算IP核Arithmetic:包含四类,第一类是LPM类型的整数运算IP核,LPM表示参数化类型IP核库。

第二类是ALT类型的整数运算IP核,ALT表示Altera特定的IP核。

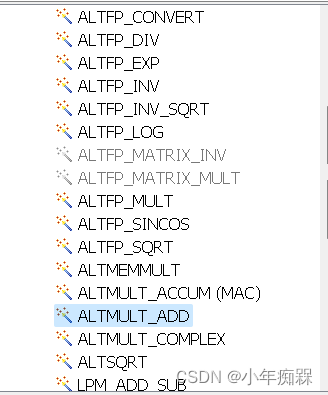

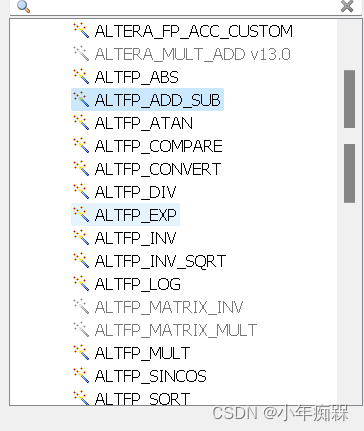

第三类是浮点数运算IP核。

第四类是逻辑运算IP核。

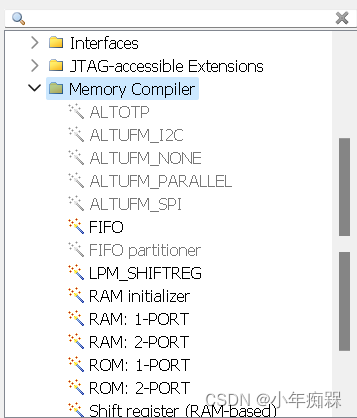

第二大类是存储器IP核。

第三大类是数字信号处理IP核。

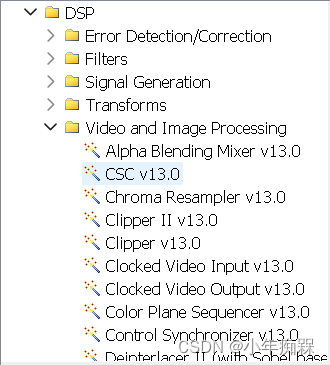

第四大类是数字通信类的IP核。

下一类是视频和图像处理IP核。

接下来是输入输出IP核。

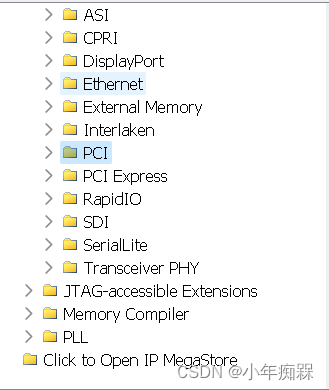

下面是接口IP核,有PCI和以太网接口等。

下面是接口IP核,有PCI和以太网接口等。

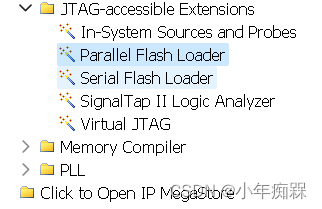

最后是FPGA调试部分的IP核,有并行flash、串行flash等。

最后是FPGA调试部分的IP核,有并行flash、串行flash等。

2571

2571

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?