前言

时钟对fpga来说是十分重要的,但板载晶振提供的时钟信号的频率是固定的,不一定能满足工程的需求,于是使用分频或倍频来产生需要的时钟。

分频器是数宇系统设计中最常见的基本电路之一。所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。

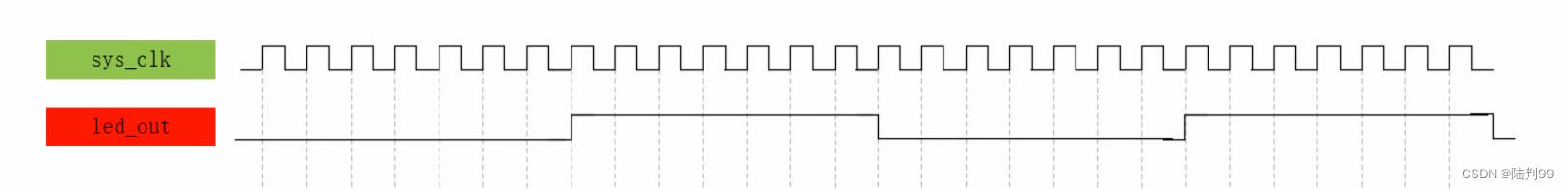

分频器分为偶数分频器和奇数分频器,和计数器非常类似,有时候甚至可以说就是一个东西。以计数器visio图示为例,输出信号的一个周期对应输入信号的若干个周期。

一、代码

1.rtl代码

代码如下(示例):

module divider_six

(

input wire sys_clk,

input wire sys_rst_n,

output reg clk_out

);

//声明寄存器变量

reg [1:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt<=2'd0;

else if(cnt == 2'd2)

cnt<=2'd0;

else

cnt<=cnt+2'd1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_out<=1'b0;

else if(cnt == 2'd2)

clk_out<=~clk_out;

else//复位信号为高无效且没有记数到最大值

clk_out<=clk_out;//保持为原来的电平

endmodule

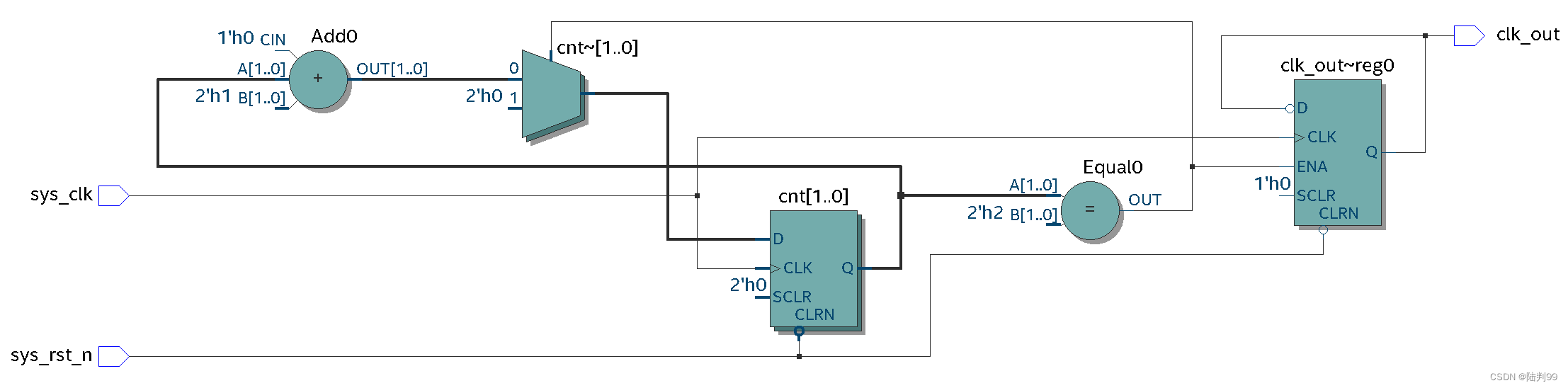

2.RTL Viewer

可以看出与计数器差别不大,只是位宽不同。

3.仿真代码

`timescale 1ns/1ns

module tb_divider_six();

reg sys_clk;

reg sys_rst_n;

wire clk_out;

initial

begin

sys_clk=1'b1;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end

always #10 sys_clk=~sys_clk;

divider_six divider_six_inst

(

.sys_clk (sys_clk),

.sys_rst_n(sys_rst_n),

.clk_out (clk_out)

);

endmodule

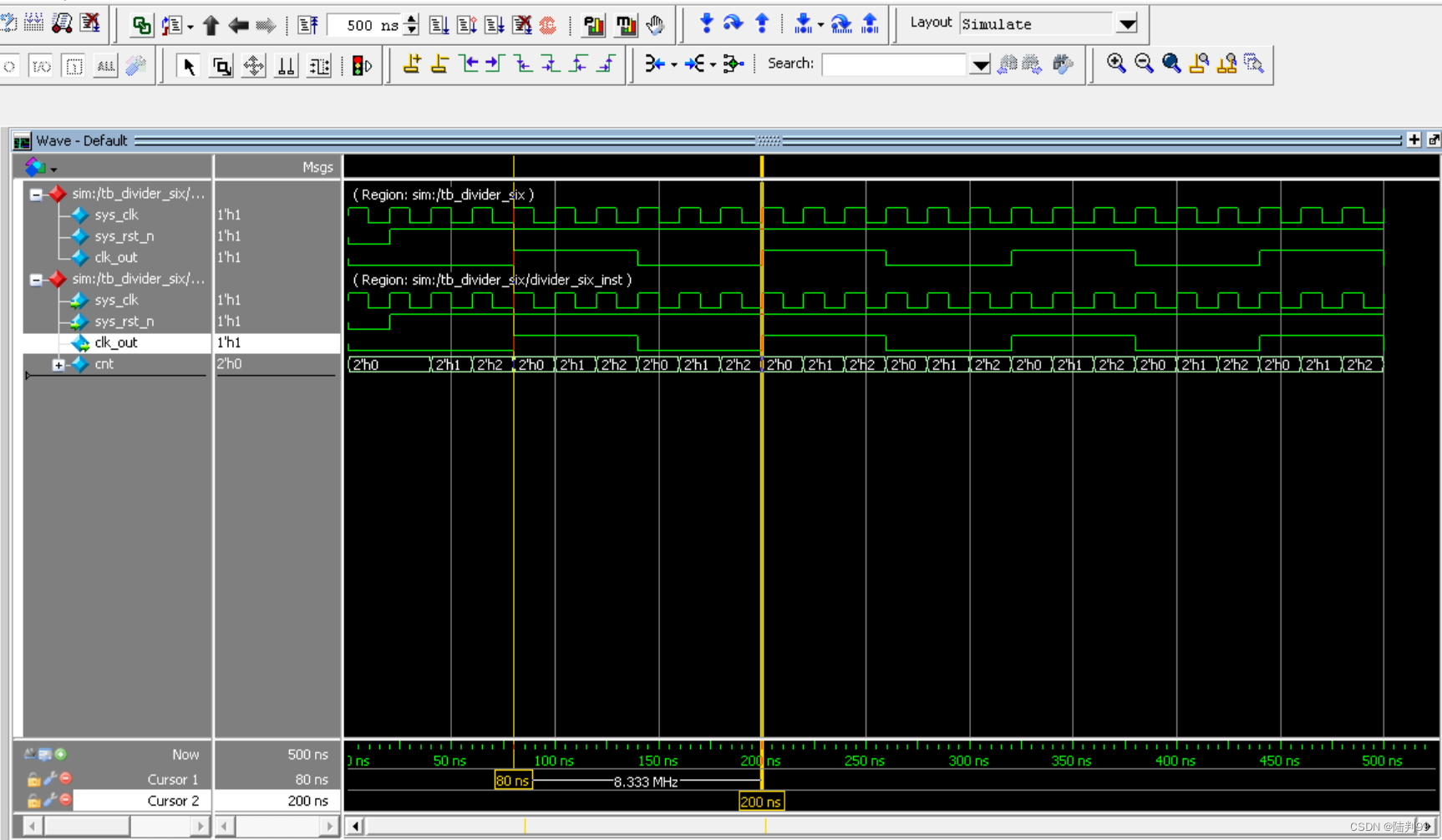

三、仿真结果

将120ns转化为8.333MHz,可以看出:8.333MHz为50MHz的6分频。

737

737

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?