下文主要介绍源同步输出时,输出时钟的几种产生方式以及相应的时钟约束指令

源同步输出的信号有时钟和数据信号,输出时钟是由fpga产生的,对于输出时钟有多种产生方式,例如:

1、通过fpga的锁相环产生输出时钟;

2、通过fpga的ALTDDIO IP核产生输出时钟;

3、通过状态机控制产生输出时钟;

4、将驱动数据的时钟直接输出。

通过产生时钟直接作为输出时钟 和用一个时钟去驱动ALTDDIO IP核 产生输出时钟 这两种是比较常用的方式。在fpga里驱动数据输出用的时钟和 用来驱动ALTDDIO IP核 的时钟 可以是由相同的锁相环产生的,也可以是由不同的锁相环产生的。具体要看你输出的信号类型

以下情况可以用同一个锁相环:

(1)中心或边沿对齐的SDR输出;

(2)边沿对齐的DDR输出。

以下情况应该用不同的锁相环:

(1)中心对齐的DDR输出;

(2)一个时钟直接作为驱动外部器件的时钟(这样可以补偿时钟和数据间的不同延迟);

(3)输出时钟和数据中心或边沿对齐(比如时钟和数据延迟50°,这样的话就只能用锁相环去生成对应的延迟);

(4)精确调试时钟和数据间的相位关系

下面是几种常用的时钟输出方式及时钟约束命令:

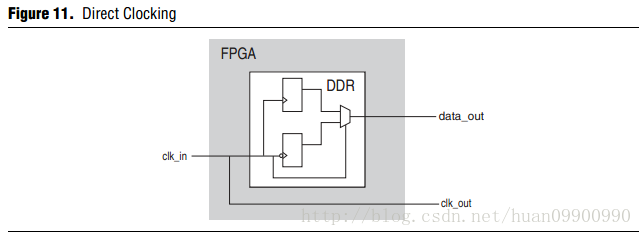

1、输入时钟直接输出:

输入fpga的时钟直接用来作为输出的时钟和发送数据的时钟

对输入fpga的时钟和输出时钟做约束,命令如下:

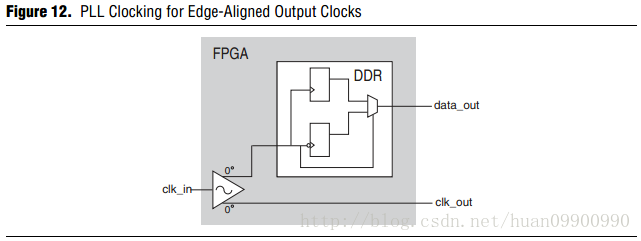

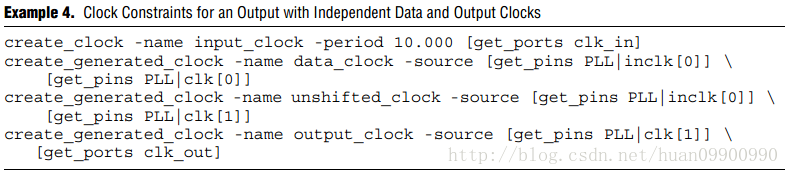

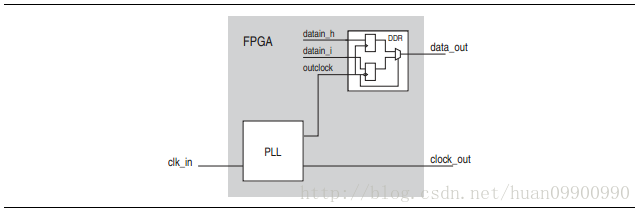

2、用锁相环来产生两个独立的时钟:输出时钟和数据时钟。

输出时钟和数据边沿对齐。

此时需与约束的时钟有:输入fpga时钟clk_in,通过锁相环生成的两个时钟,以及输出fpga的时钟clk_out

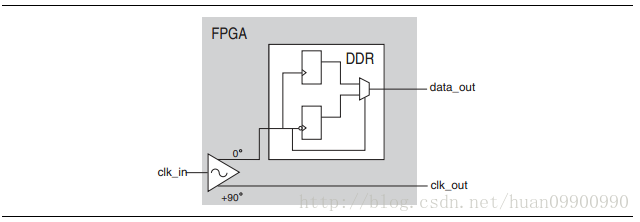

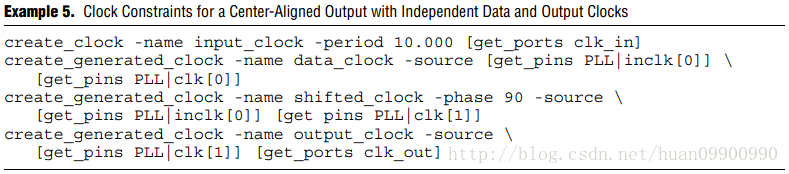

3、DDR输出数据与时钟中心对齐

此时输出的时钟相对于输出数据有一个90°的相位偏移,用PLL去产生一个相对于数据有90°偏移的时钟。

此时约束输出时钟有一个90°的相位偏移

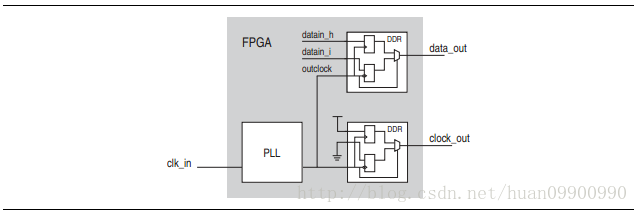

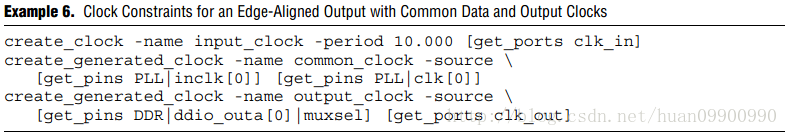

4、DDR输出时,输出时钟和数据时钟共用一个时钟,输出时钟通过例化的ALTDDIO IP核输出

约束指令如下:

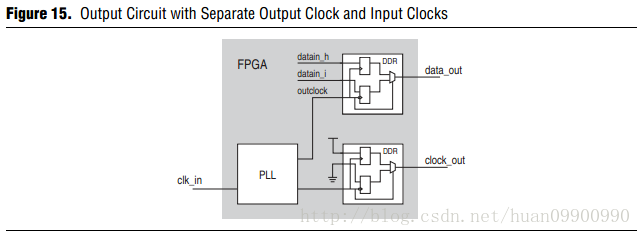

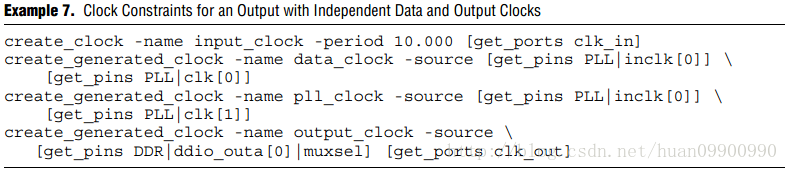

5、同一锁相环产生驱动ALTDDIO 模块时钟和数据时钟

PLL输出的两个端口 一个输出时钟发送到外部器件, 一个输出时钟用来发送数据到外部器件

约束指令如下:

6、同一锁相环产生输出到外部的时钟和驱动数据发送的时钟

约束指令如下:

581

581

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?