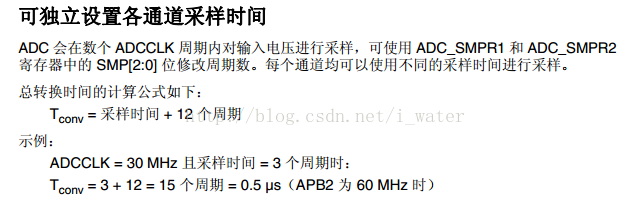

对单个ADC而言,AD采样的采样时间满足此关系:

我用的ADCCLK=42MHz,针对单ADC而言,最大采样率为42M / (12 + 3) =2.8M // 取ADC_SampleTime_3Cycles

要采 100KHz的信号32点,则采样率需达到3.2MHz(根据以上计算,好像有那么一小丢丢够不着。。。),没关系,多重ADC可以解决这个问题。

要采 1MHz的信号32点,则采样率需达到32MHz,使用STM32根本达不到(你不用花时间啦)。。。但是,可以尽量提高采样率,我们可以试一试,有时候就算明知不可为,我们还是值得让它走到它命运的巅峰(^--^)。

以下是官方例子的说明,我们可以稍加揣测:

In this example, the system clock is 144MHz, APB2 = 72MH

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2801

2801

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?