初学初步学习GoWin的FPGA的内部时钟OSC配置,主要有几点:

1、内部OSC的原始晶振频率。

2、需要分频FERQ_DIV。

3、使能时钟。

4、时钟例化。

根据自己的FPGA芯片型号,确定芯片中的的频率,然后根据自己需要的频率计算出FREQ_DIV。

图1

根据FREQ_DIV配置图2中的红框中的数值,注意只能为偶数。

根据FREQ_DIV配置图2中的红框中的数值,注意只能为偶数。

图2

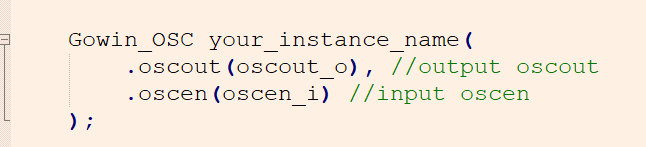

然后点OK后,会打开gowin_osc_tmp.v文件,然后将模块配置到自己的工程。,此处应注意,一定要进行使能,要不配置完后,时钟不会运行,不会运行,不会运行,重要的化说三遍。

图3

若后边想要修改分频的频率,只需将gowin_osc.v中的osc_inst.FREQ_DIV的值进行修改就可以。

图4

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?