1、DCDC Layout优先级

输入电容 > 输出电容 > 电感

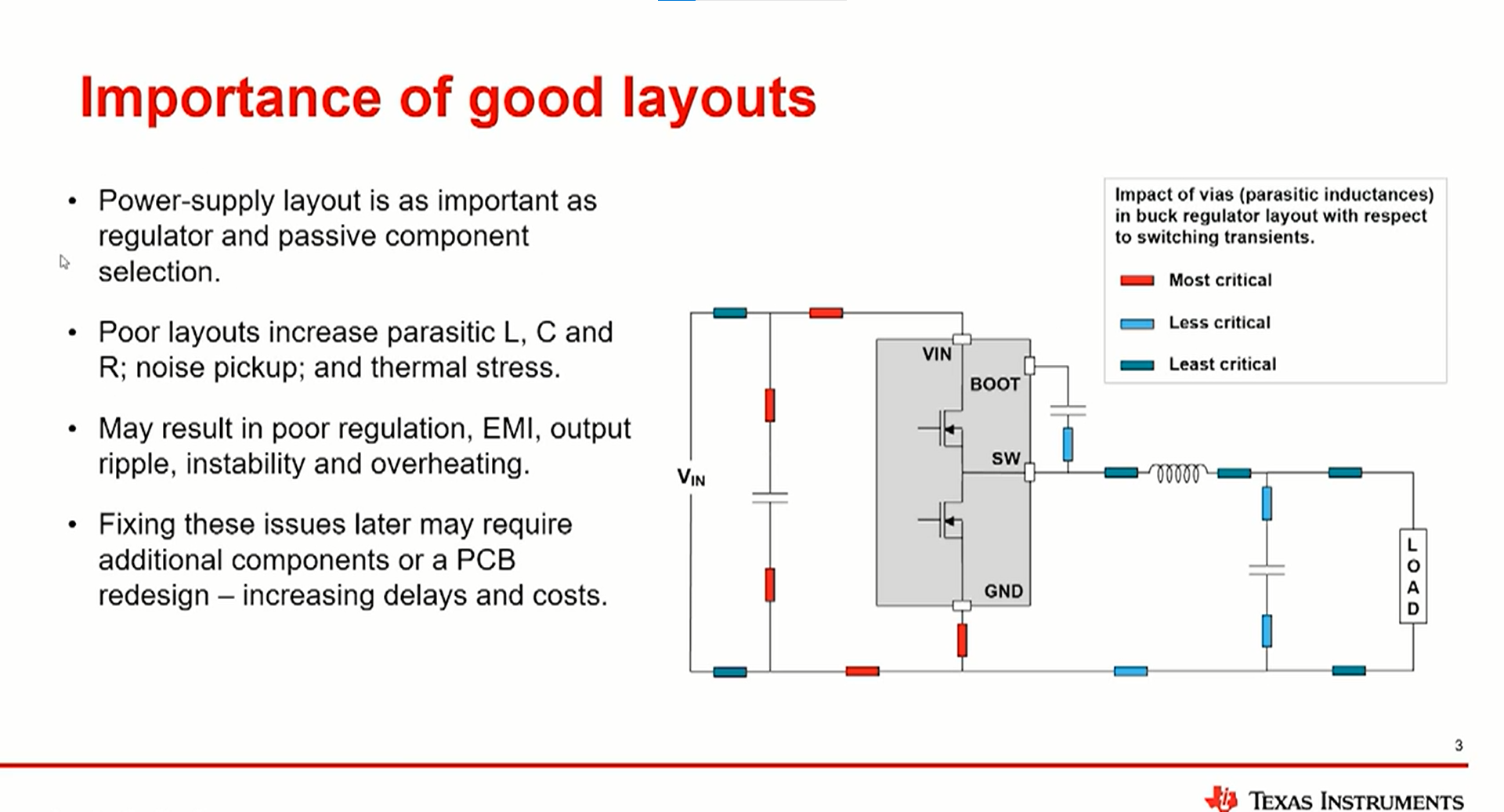

2、较差layout可能导致的问题

-

较差的电压调整率

-

输出电压不稳定

-

SW/LX输出过冲变大,可以用Snubber电路或Boost自举电阻压制,但是增加成本且效率变差

-

输出电压纹波和噪声变大

-

EMI变差

-

散热效果变差

-

寿命和可靠性差

3、Layout要点

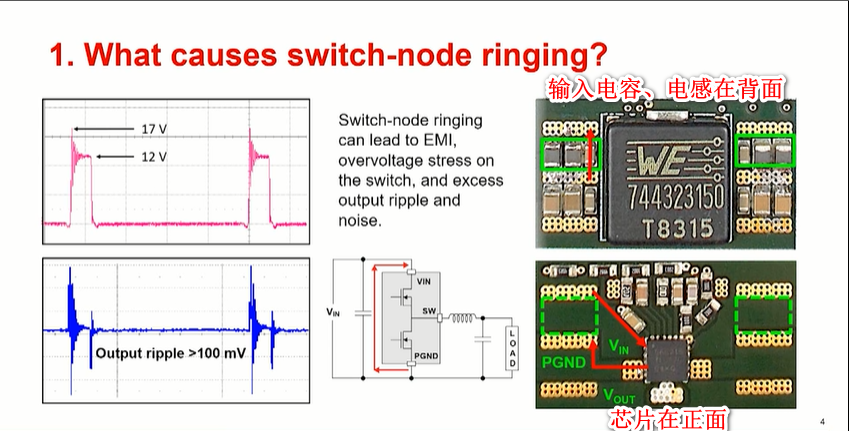

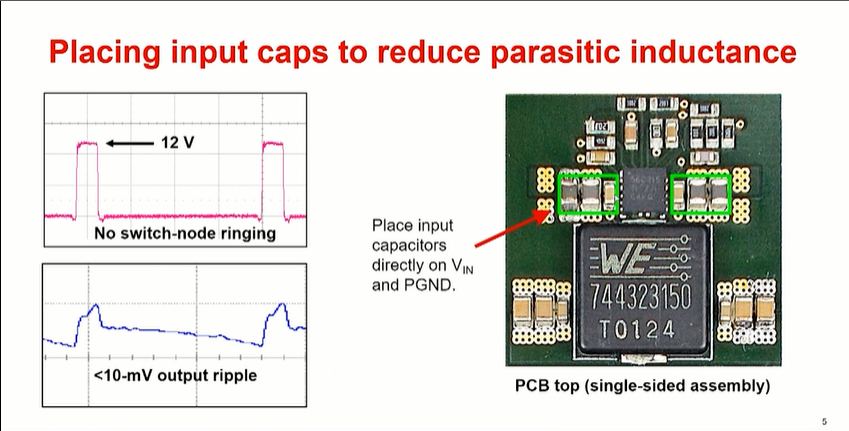

- 开关导通回路小,即输入电容(小电容优先)同时尽量靠近芯片管脚VIN和GND,且放在同一面,不要VIA,尽量降低寄生电感

- 输出纹波变差

- SW/LX管脚过冲变大

注意:上面这个例子两种layout改变的参数较多,并不能证明输入电容位置的改变就能带来质的变化,如电感位置的变化也会带来改善。

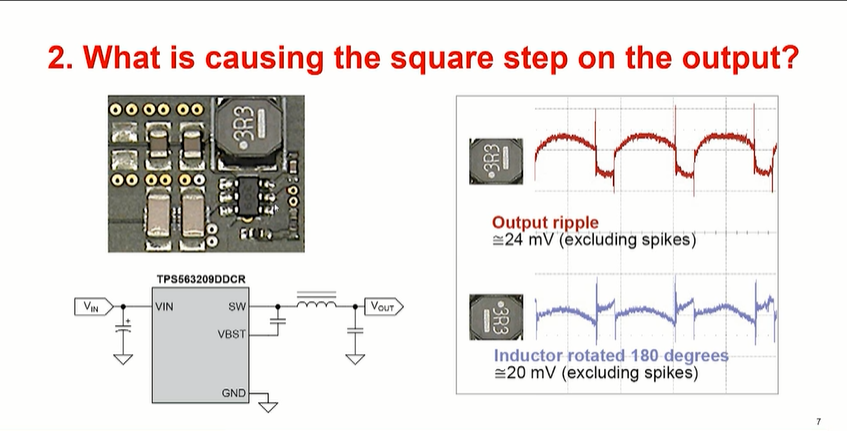

- 开关关闭回路小,即输出电感靠近芯片管脚,输出电容靠近电感

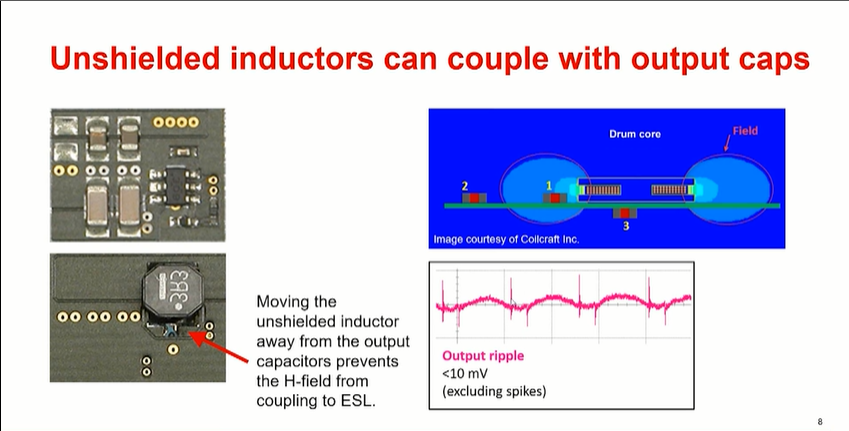

- 输入电容和输出电容相隔1~2cm

- 非屏蔽/半屏蔽电感下方铜皮挖空(第一层即可)

- 在电感下方铺铜会在接地面上产生涡流;涡流会影响功率电感的电感量并增加系统损耗

- 接地面噪声会影响其他高速信号

- 反馈信号走线远离电感、SW/LX管脚、BS管脚和其他高频信号

- SW/LX管脚到电感之间的走线并非越大越好

还有一些说法:

- 输出电容可以离非屏蔽/半屏蔽电感稍远一些

- 全屏蔽电感下方不用挖空

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?