芯片制造是一个物理过程,存在着工艺偏差(包括掺杂浓度、扩散深度、刻蚀程度等),导致不同批次之间,同一批次不同晶圆之间,同一晶圆不同芯片之间情况都是不相同的。

在一片wafer上,不可能每点的载流子平均漂移速度都是一样的,随着电压、温度不同,它们的特性也会不同,把他们分类就有了PVT(Process,Voltage,Temperature)。

Process Corner

Process分为5个不同的corner(第一个字母代表NMOS,第二个字母代表PMOS):

- TT:Typical N Typical P

- FF:Fast N Fast P

- SS:Slow N Slow P

- FS:Fast N Slow P

- SF:Slow N Fast P

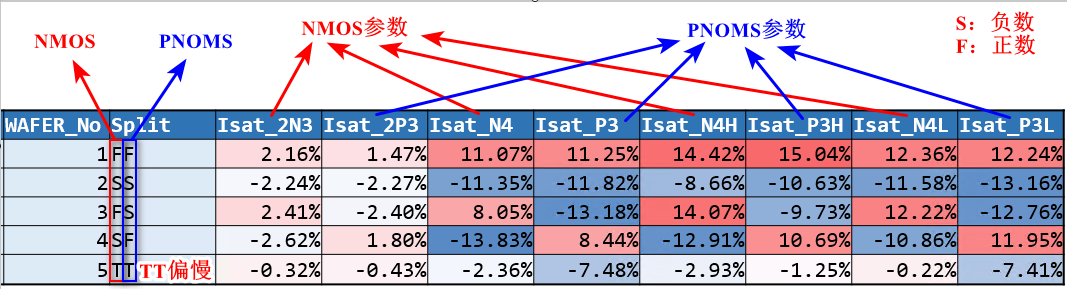

Process Corner都是针对不同浓度的N型和P型掺杂来说的。NMOS和PMOS在工艺上是独立做出来的,彼此之间不会影响。通过Process注入的调整,模拟器件速度快慢,同时根据偏差大小设定不同等级的FF和SS。正常情况下大部分是TT,而以上5种corner在+/-3sigma可以覆盖约99.73%的范围,这种随机性的发生符合正态分布。

根据偏差大小设定不同等级的 FF 和 SS,如 2FF 表示往快的方向偏2个Sigama,3SS 表示往慢点方向偏3个Sigama,1.5SS 表示往慢点方向偏1.5个Sigama 。

PVT对芯片性能的影响

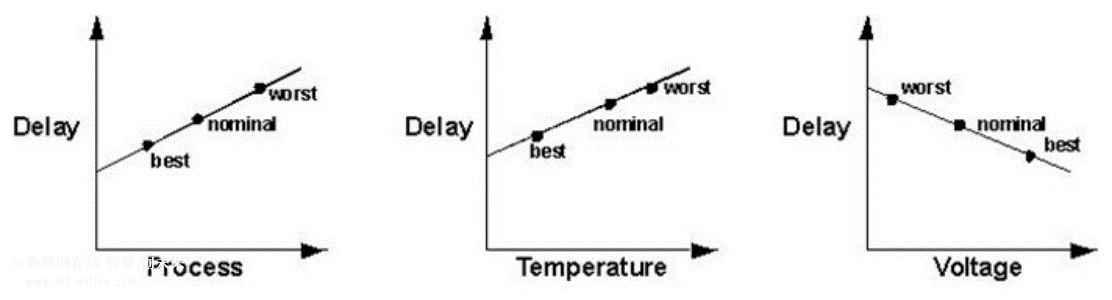

PVT对Timing影响

Process Corner

工艺角越慢,延迟越大,setup time越小,hold time越大。

Temperature

温度越高,延迟越大,setup time越小,hold time越大。

Voltage

电压越高,延迟越小,setup time越大,hold time越小。

PVT对IO Driving Strength影响

Process Corner

工艺角越慢,IO Driving Strength越弱。

Temperature

温度越高,IO Driving Strength越弱。

Voltage

电压越高,IO Driving Strength越强。

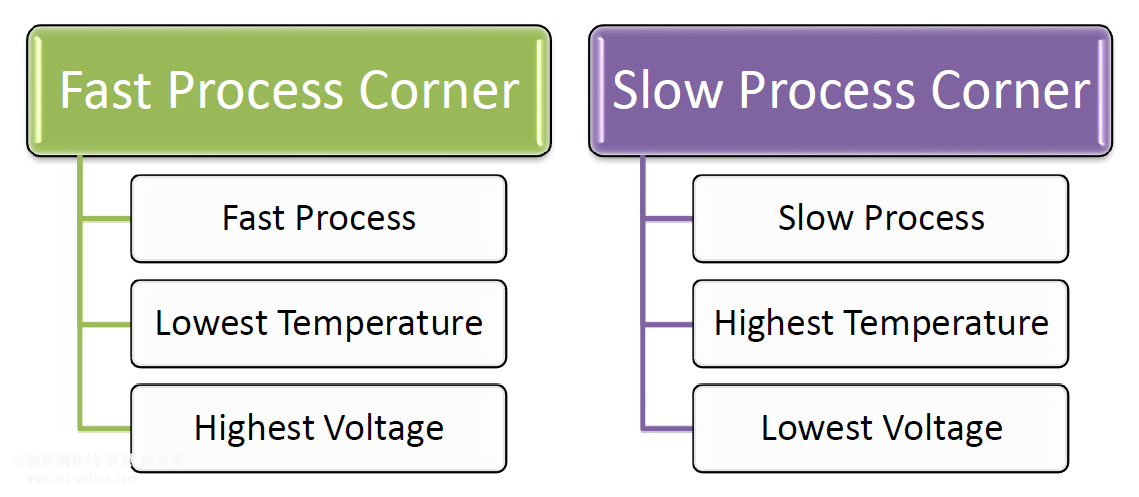

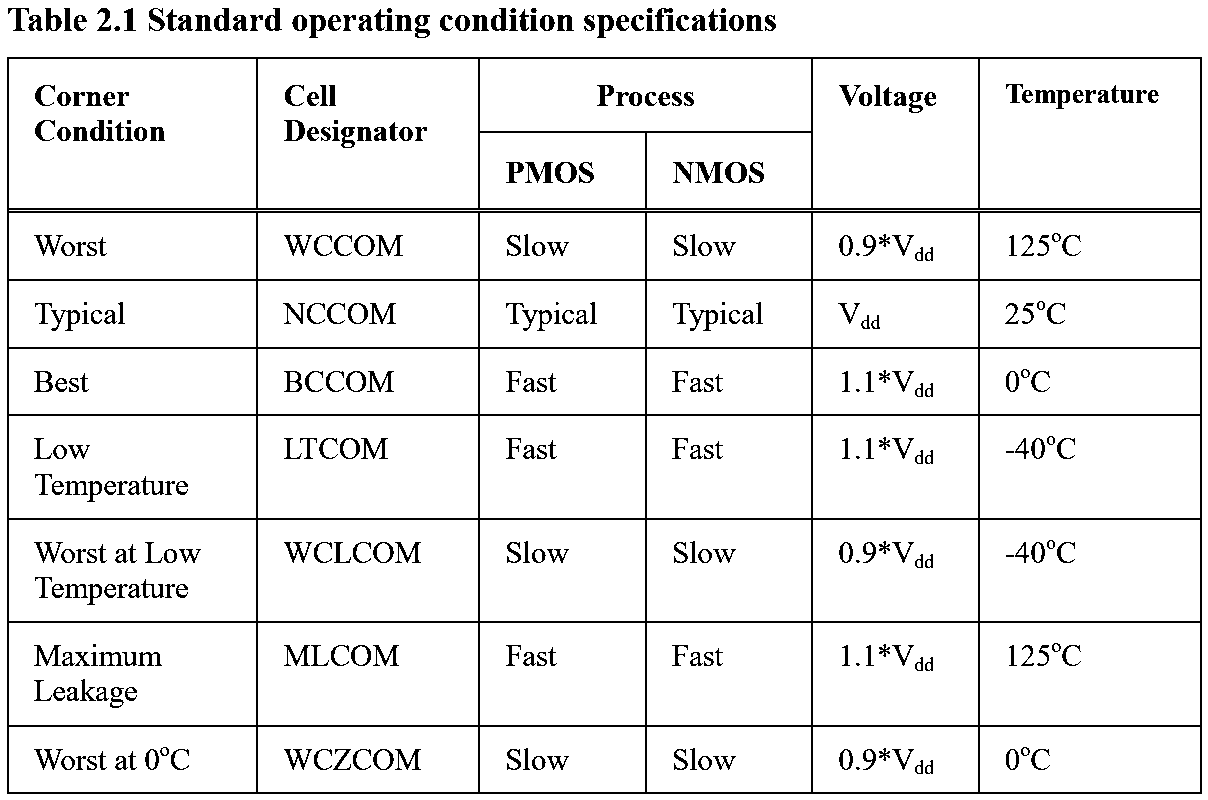

不同的PVT条件组成了不同的corner,另外在数字电路设计中还要考虑RC corner的影响,排列组合后就可能有超过十种的corner要分析。但是在FPGA设计中的静态时序分析一般仅考虑Best Case和Worst Case,也称作Fast Process Corner 和Slow Process Corner,分别对应极端的PVT条件。

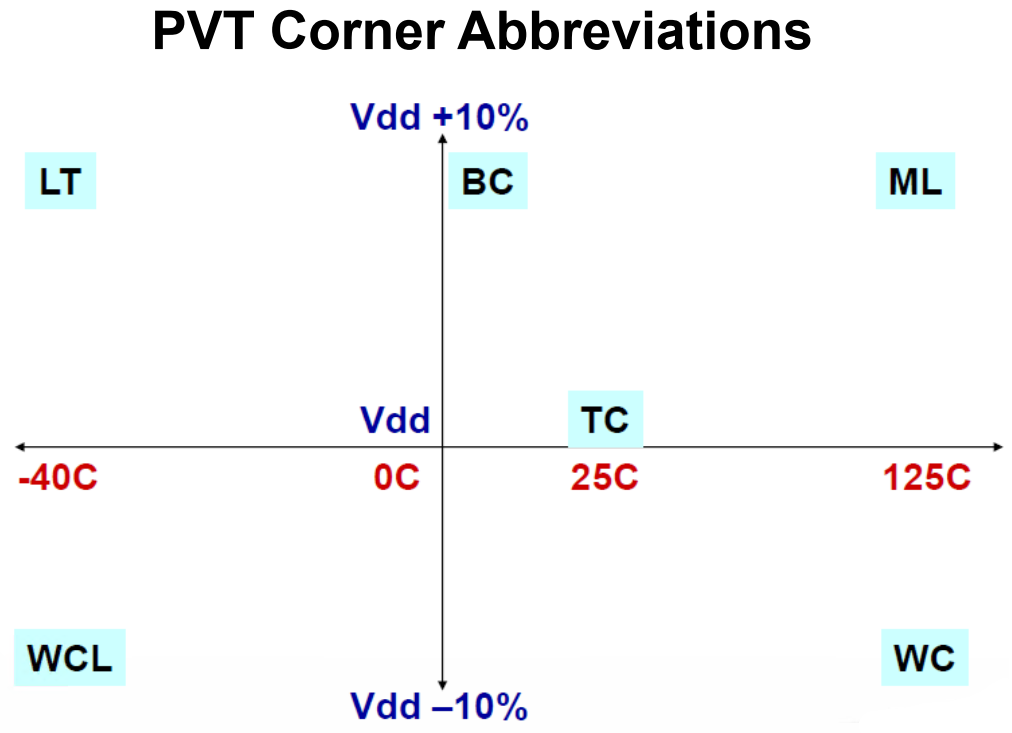

TSMC Standard I/O PVT

| Name | Description | Core Voltage | I/O Voltage | Temp | Process |

|---|---|---|---|---|---|

| LT | Low Tempeature | 1 .1 *Vdd | 1 .1 *Vddpst | -40 | FF |

| BC | Best Case | 1 .1 *Vdd | 1 .1 *Vddpst | 0 | FF |

| TC | Typical Case | 1 .0*Vdd | 1 .0*Vddpst | 25 | TT |

| WC | Worst Case | 0.9*Vdd | 0.9*Vddpst | 125 | SS |

| WCL | Worst Case Low Temperature | 0.9*Vdd | 0.9*Vddpst | -40 | SS |

| WCZ | Worst Case Zero Temperature | 0.9*Vdd | 0.9*Vddpst | 0 | SS |

| ML | Maximum Leakage | 1 .1 *Vdd | 1 .1 *Vddpst | 125 | FF |

流片Corner Wafer介绍

有关流片验证的一些看法

Vivado使用误区与进阶——如何读懂用好 Timing Report?

2028

2028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?