在电子器件组装过程中,EOS(Electrical Over Stress)与 ESD(Electrical Static Discharge)造成的集成电路失效约占现场失效器件总数的50%,且通常伴随较高不良率以及潜在可靠性问题,是产线一大杀手。

当问题发生时,应该如何查找真因、寻找解决方案,一直以来都是工程师的难题。阔智通测集成电路失效分析实验室,通过多年的行业积累,总结出一套相对完整的针对EOS/ESD的分析方法,通过失效分析、模拟验证等手段,可以更好地协助工程师提升产线良率及IC的可靠性。

⇲ 故障概念明晰

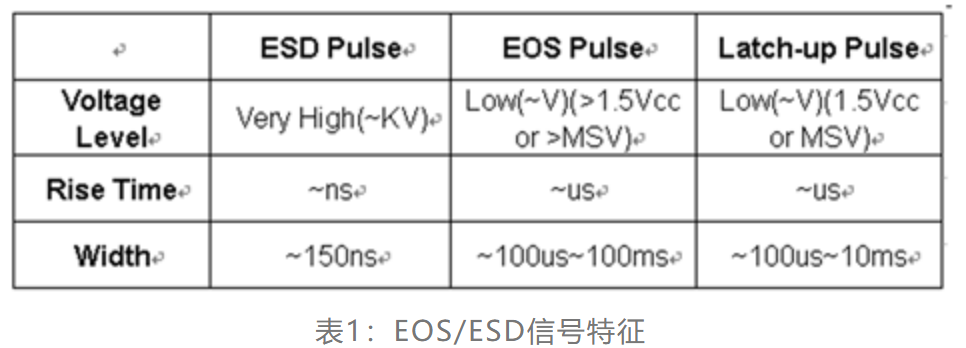

EOS全称电气过应力(Electrical Over Stress),其表现方式是过压或者过流产生大量的热能,烧坏元器件内部。EOS可指所有的过度电型故障,也包括下面要介绍的ESD。

ESD全称静电放电(Electrical Static Discharge),特指因静电造成的瞬时烧坏元器件的故障。我们知道静电虽然持续时间极短,但却可以产生巨大的电流和电压,这足以破坏元器件的内部结构。按照定义,ESD本质上仍是电气过应力故障,故而它可以看做EOS的特例。

⇲ 产线失效到底是由EOS还是ESD引起?

做失效分析时,最希望知道root cause是EOS还是ESD,确认失效机理及真因,是改善良率的第一步,也是非常关键的一步。我们区分EOS还是ESD会首先通过失效分析手法挖掘IC的物理失效现象,然后从现象上去区分。

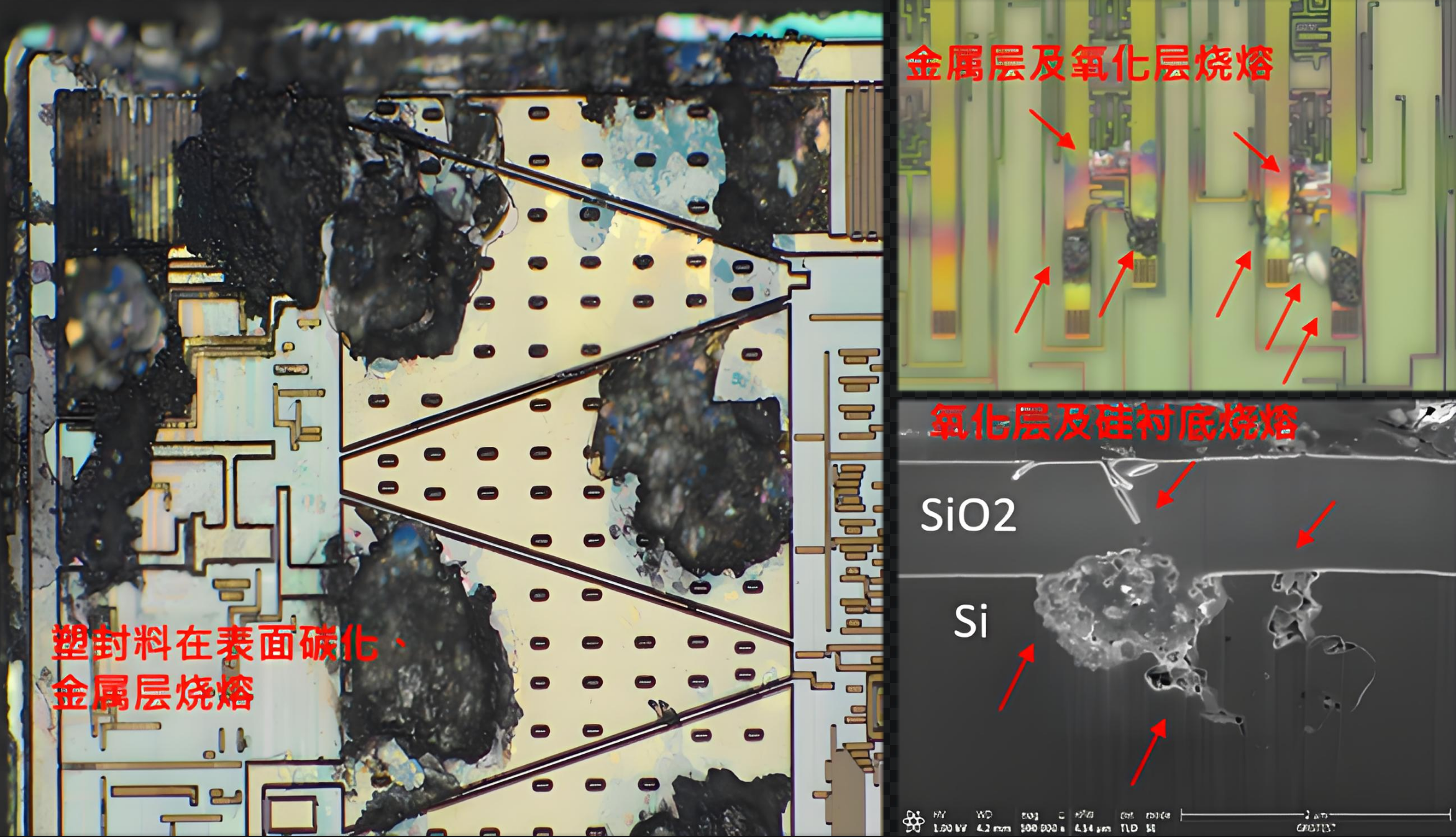

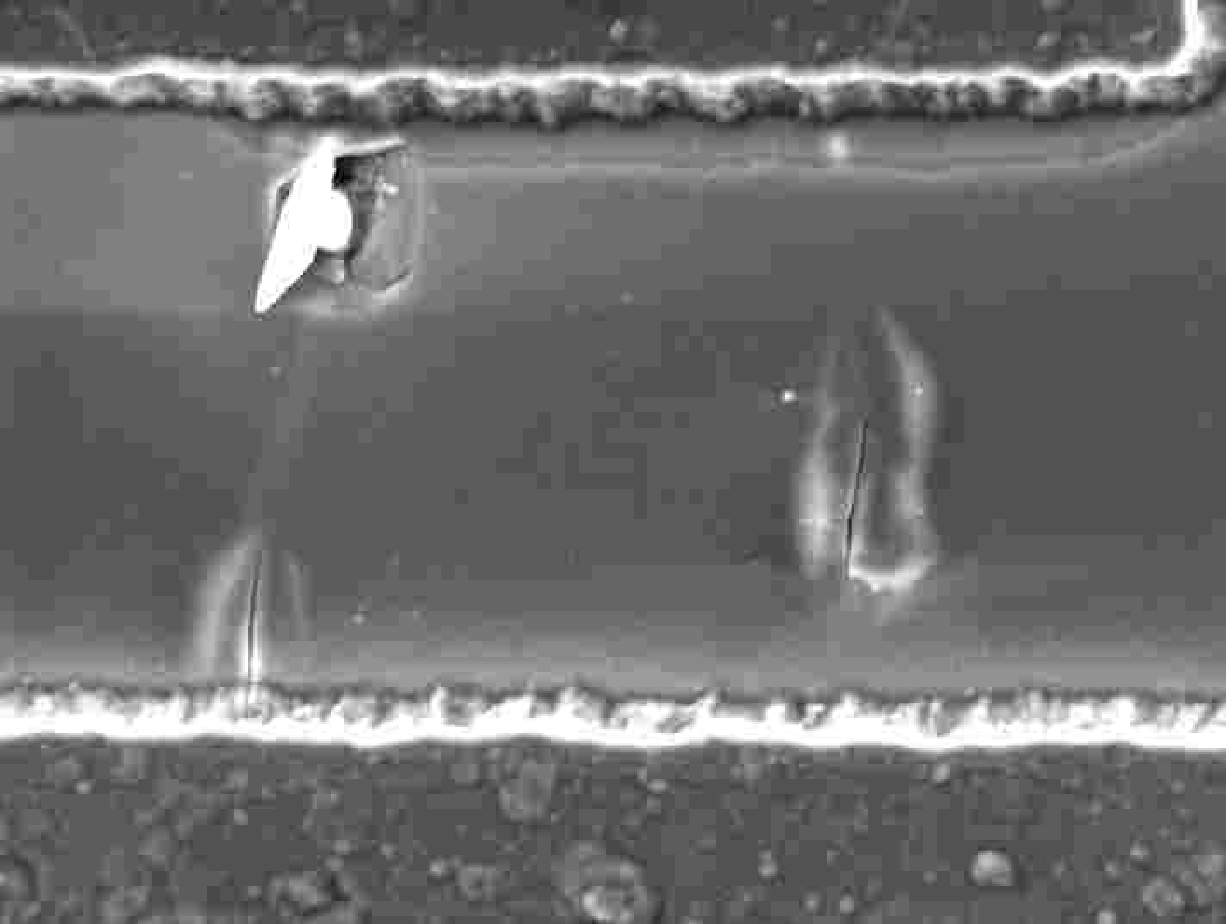

① EOS的概念核心是电气过应力,是长时间(几微秒到几秒)持续的过压或大电流,超过限额的电流使得器件损坏,一般呈现功率升高、高强度的发热、金属线膨胀、造成元器件整体大面积的损坏,甚至包括塑料封装烧毁,常见EOS物理失效表现:氧化层、金属层大面积熔融以及封装体碳化等现象,如下为典型EOS失效图片。

在EOS失效识别后,找原因过程大家经常遇到如何判断到底是过压造成的呢?还是过流造成?以利于排查电路相关连接电的电性能参数及变化的测试确认。那么两种情况(过压或过流)失效特征上有无区别?下面以功率MOSFET来测试验证探讨。

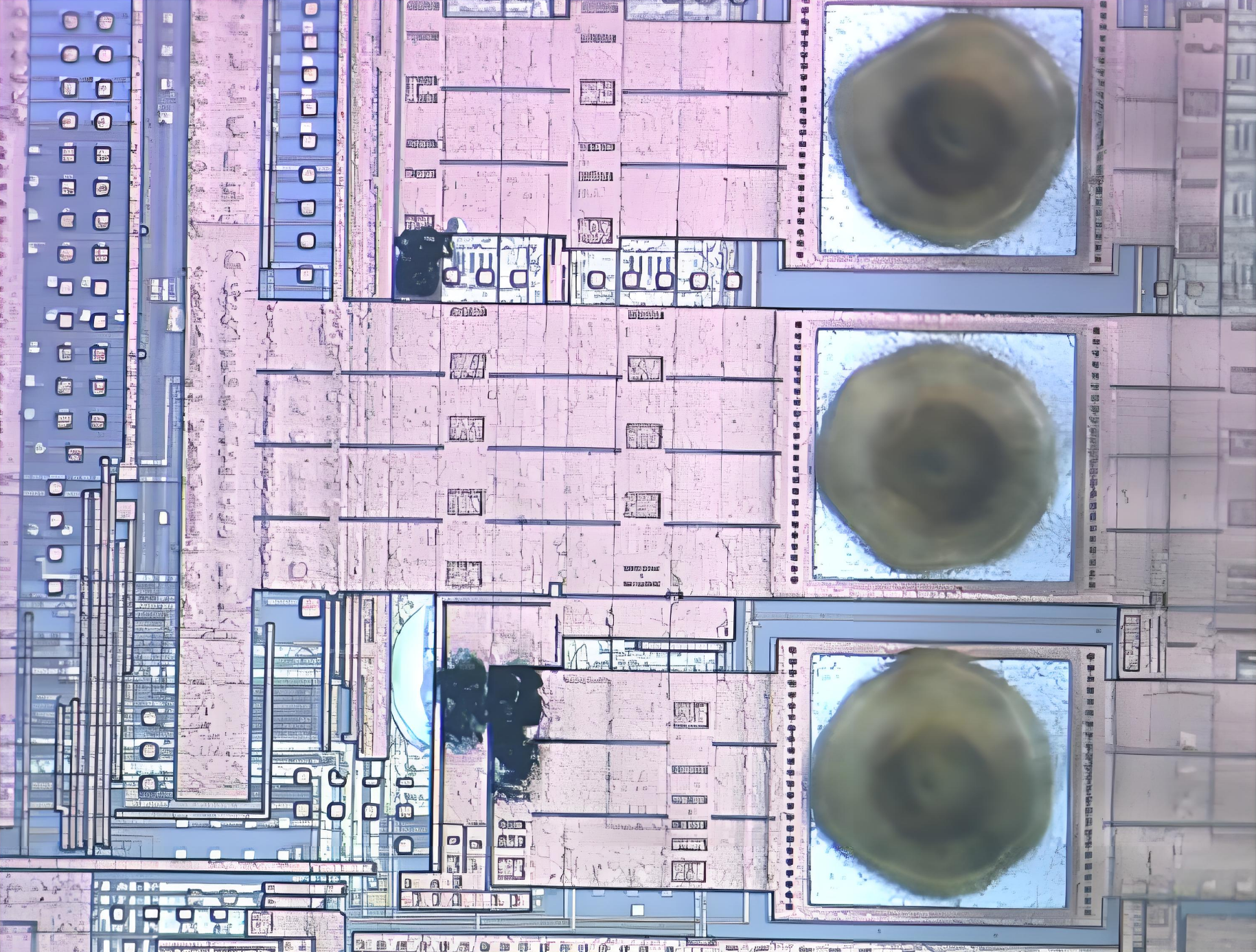

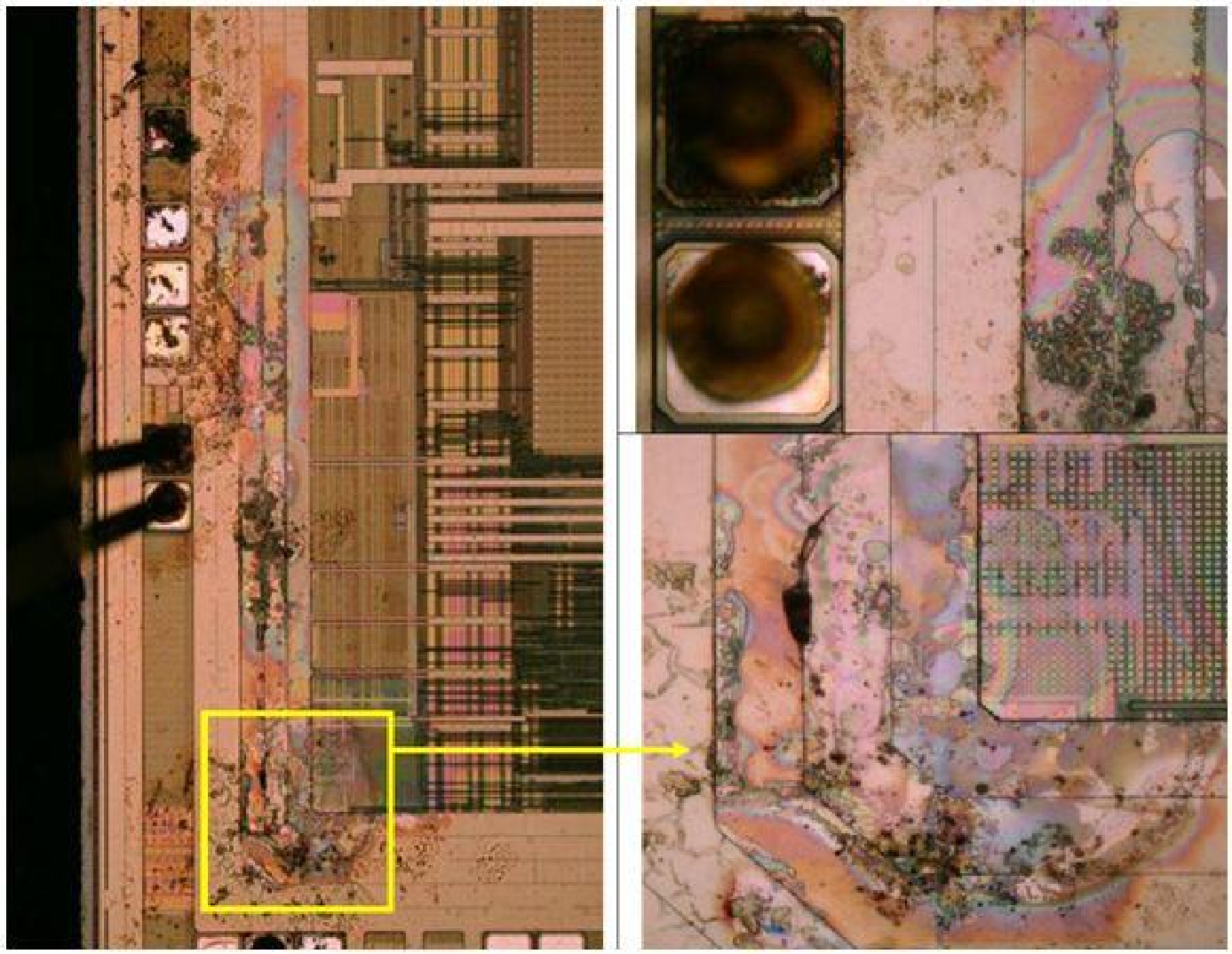

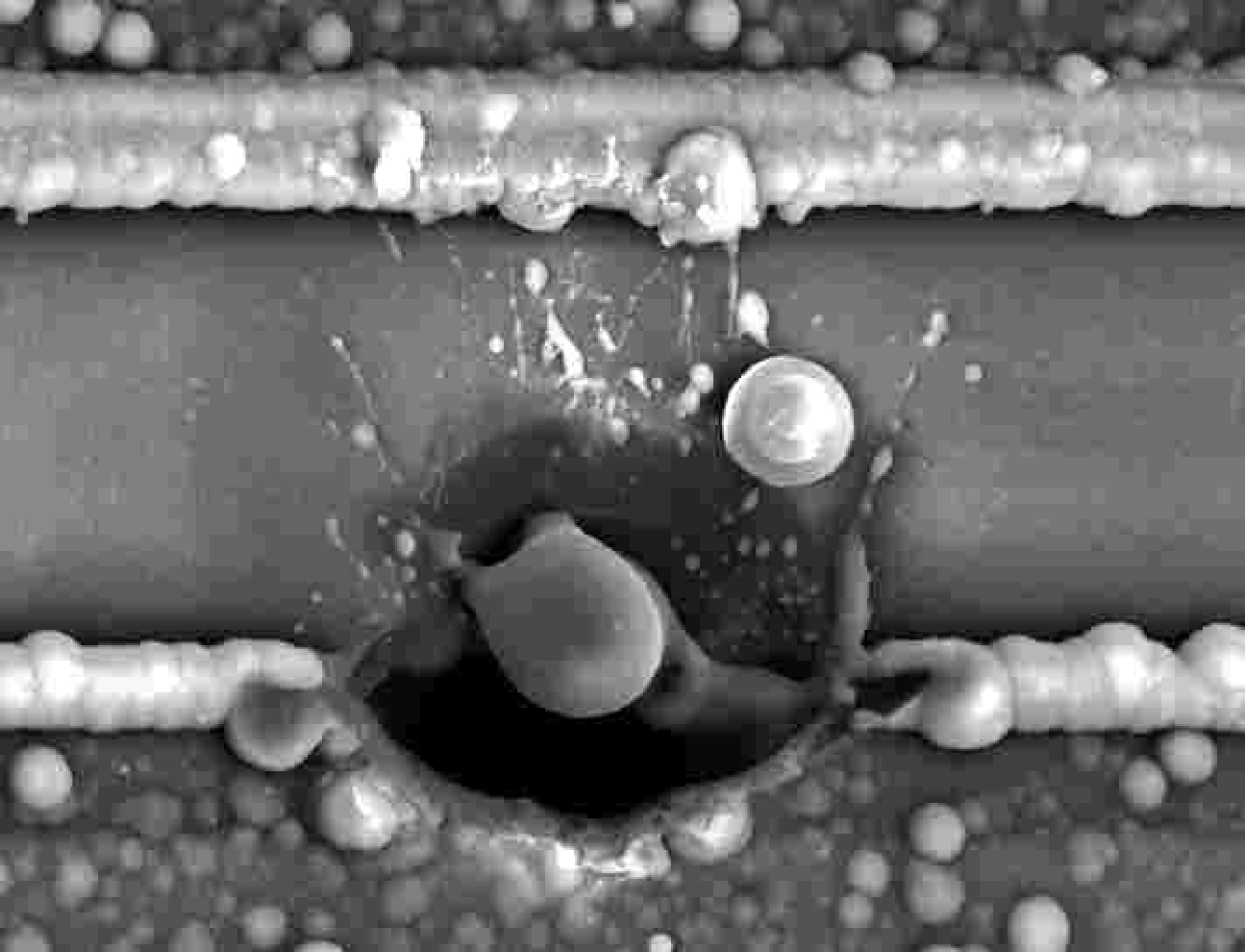

将过电压和过电流测试损坏的功率MOSFET去除外面的塑料外壳,对露出的硅片正面失效损坏的形态的图片。

a.过压测试后损坏测试图片

从图可以看到:过电压的失效形态是在硅片中间的某一个位置产生一个击穿小孔洞,通常称为热点,其产生的原因就是因为过压而产生雪崩击穿,在过压时,通常导致功率MOSFET内部寄生三极管的导通[1],由于三极管具有负温度系数特性,当局部流过三极管的电流越大时,温度越高,而温度越高,流过此局部区域的电流就越大,从而导致功率MOSFET内部形成局部的热点而损坏。

硅片中间区域是散热条件最差的位置,也是最容易产生热点的地方,可以看到,上图中,击穿小孔洞即热点,正好都位于硅片的中间区域。

b.过压测试后损坏测试图片

从图可以看到:在过流损坏的条件下,所有的损坏位置都是发生的S极,而且比较靠近G极,因为电容的能量放电形成大电流,全部流过功率MOSFET,所有的电流全部要汇集中S极,这样,S极附近产生电流 集中,因此温度最高,也最容易产生损坏。

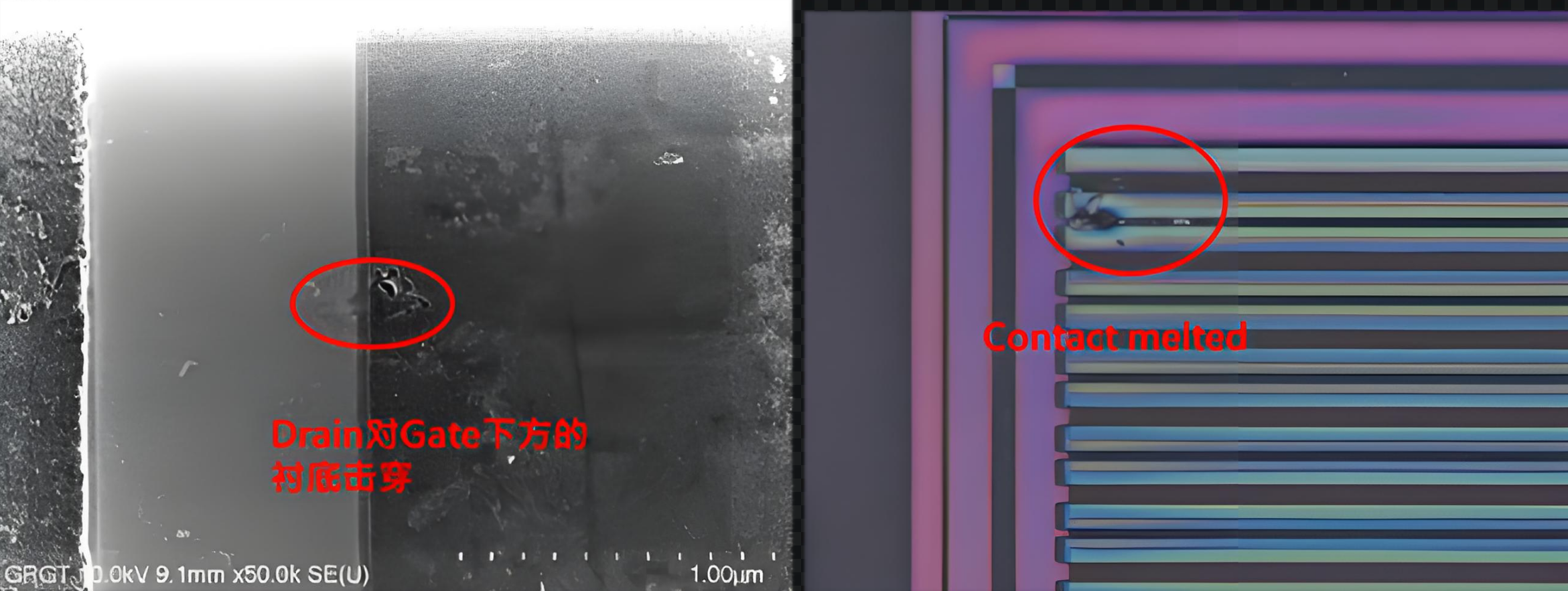

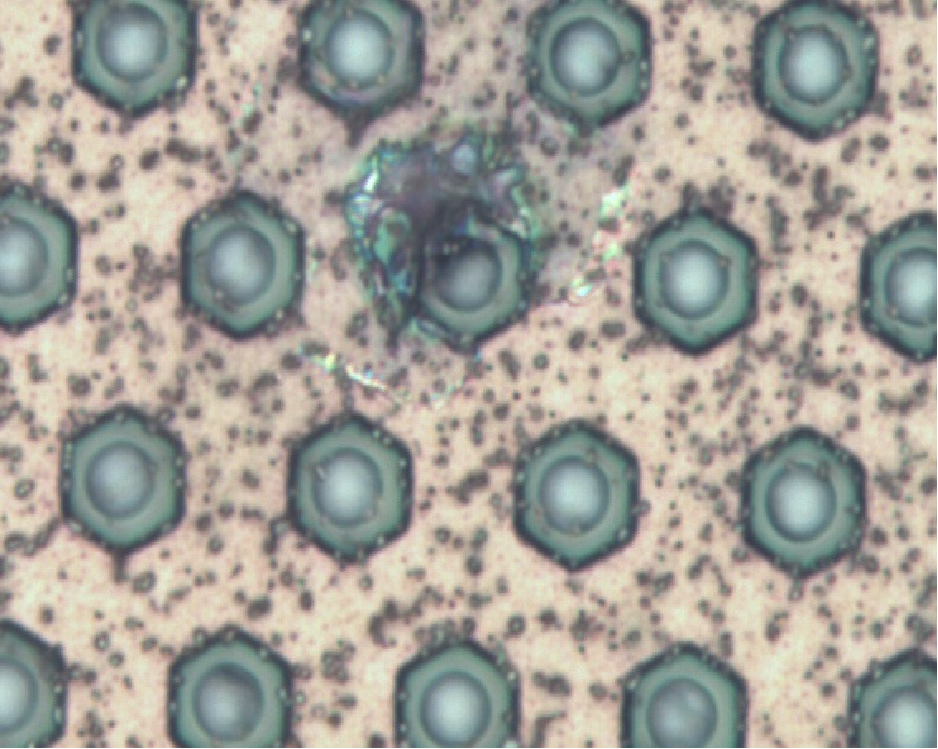

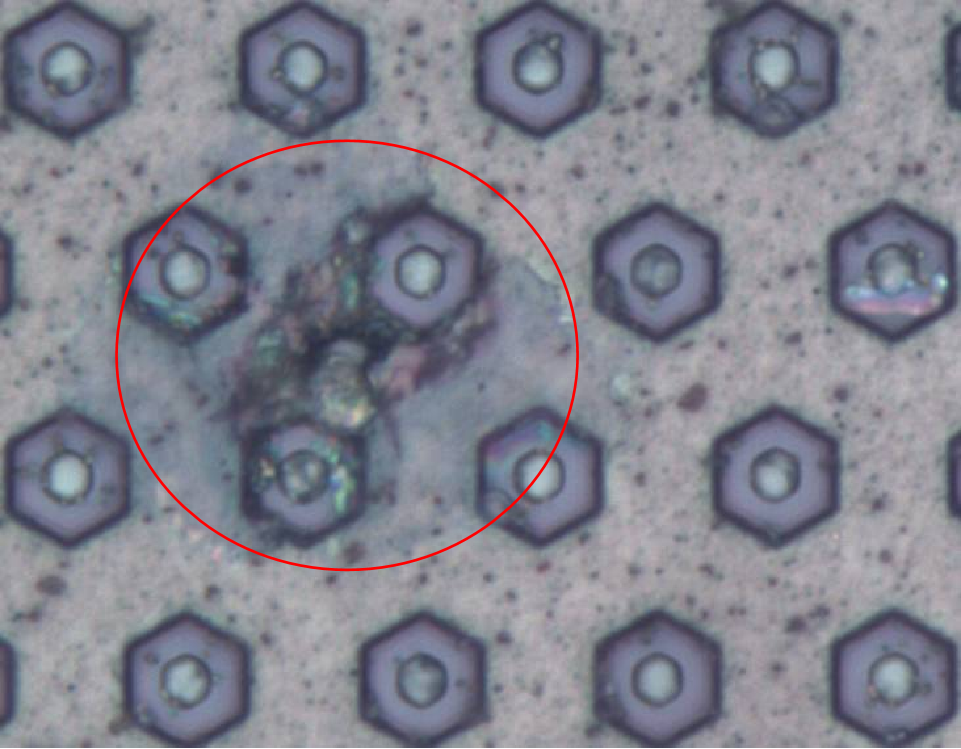

② ESD特指静电所引起的过点损坏,持续时间要短得多,可以是几皮秒到几纳秒,释放的总能量有限,故而导致的经常是晶体管级别的损坏,深藏在元器件内部结构,总体可见性不强,确定故障点往往需要更复杂的开盖测试等流程,常见ESD物理失效表现:衬底击穿、多晶硅熔融、GOX pin hole、contact melted、metal melted等,如下为典型ESD失效图片。

⇲ 为什么EOS和ESD会造成不同的失效现象?

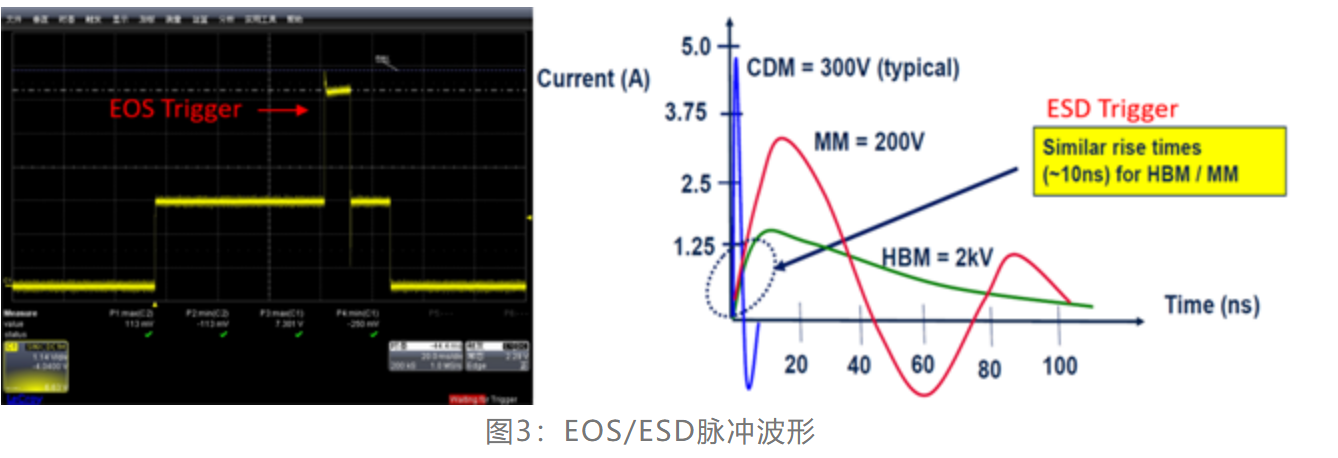

ESD从广义上属于EOS的一种,但是现场应用中我们通常把ESD单独归类,除此之外的过电应力统归于EOS。EOS 是指长时间(几微秒到几秒)持续的过压或大电流造成的局部过热导致的失效,其电压、电流相对ESD较低,但是持续时间长能量更高,经常有同一功能区块多处大面积的burnout现象。ESD 单指在静电放电过程中瞬间高电压(通常在几千或上万伏特)大电流(1~10A)状态下引发的失效现象,主要特征为放电时间极短(1~100ns),因此一般呈现为轻微的点状失效。

⇲ 什么情况下无法区分EOS/ESD?

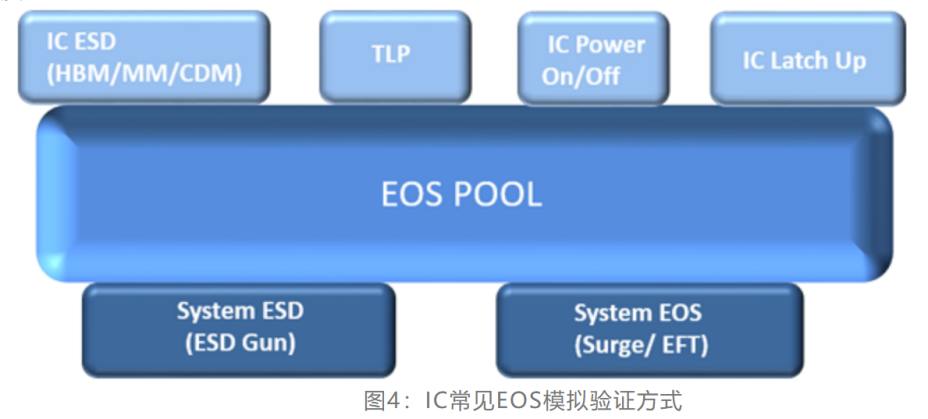

一种情况是短脉冲EOS(持续时间几个微秒)与ESD的物理损伤十分相似,比如只造成很小面积的金属熔融,这种情况就很难区分是EOS还是ESD的能量造成。另一种情况是IC先经过了ESD损伤,在后续功能验证时大漏电流诱发了burnout现象,使得IC表面同时存在EOS和ESD的物理失效特征,尤其常见于PAD旁边的IO buffer线路上,这种情况下单从物理失效现象是无法判断初始失效是否由ESD导致。当遇到EOS/ESD无法区分的情况,需要通过模拟实验进一步验证,对IC或系统使用不同模型进行EOS/ESD模拟测试(图4)test to fail,并针对失效IC进行分析

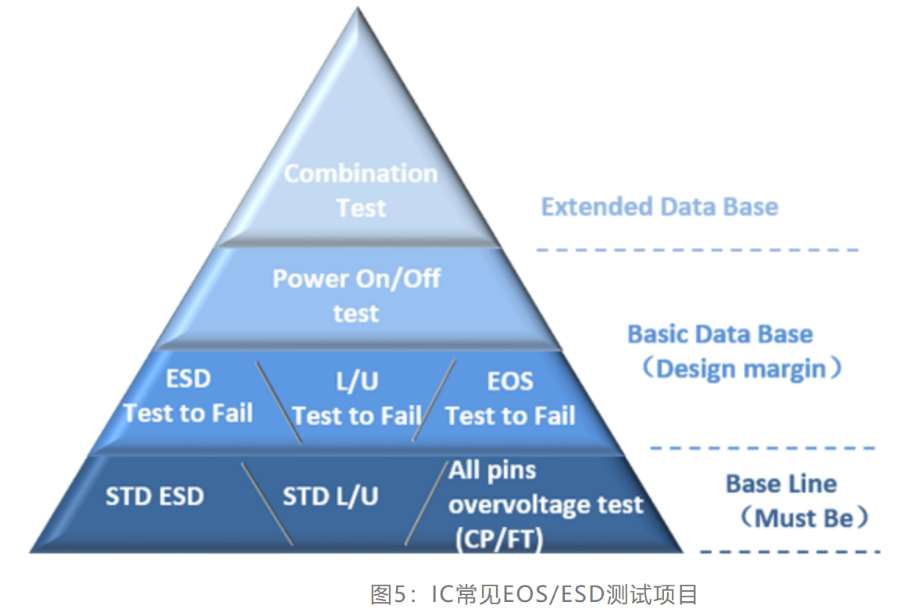

通过对比验证批芯片与实际失效芯片的物理失效现象(失效线路位置及失效发生的物理深度),不仅可以用来归纳真因,还可以了解IC或系统在不同条件下的耐受等级,从而进一步指导优化产线防护或IC的可靠性设计。针对新投产芯片也可以考虑从多维度进行EOS/ESD的验证与分析(图5),不断提升IC的可靠性品质。

综上所述,当产线发生EOS/ESD失效时,应该从哪些方面进行分析及改良?建议参考以下流程进行:

1.针对失效IC进行电性及物理失效分析,确认其物理失效现象(失效点对应的电路位置及失效的物理深度),配合现场失效信息收集,初步推断EOS/ESD失效模型;

2.针对EOS/ESD无法判断的情况,对相关IC或系统进行EOS/ESD模拟试验,验证其电压、电流耐受等级,并针对失效芯片执行失效分析,对比实际失效状况,归纳真因及梳理改善方向;

3.探测现场容易发生EOS/ESD的位置(例如使用ESD Event Detector或高频示波器),针对产线应用进行改良。

⇲ EOS/ESD原因及失效来源

1、能够造成EOS的原因,有测试程序切换(热切换)导致的瞬变电流/峰值/低频干扰、电源(AC/DC) 干扰和过电压、测试设计超过系统的承受上限、从其他装置发送的脉冲、接地反弹等。

2、能够导致ESD的原因,就是工作流程中可能生成静电的环节,包括人对物料的接触、摩擦起电、感应生电等。静电积累到一定程度,就会引发放电现象,导致失效的发生。

3、集成电路IC常见EOS/ESD失效来源:

① 生产人员/设备/环境的ESD防护不佳

② 使用易感应静电的材料

③ 模块测试开关引起的瞬态/毛刺/短时脉冲波形干扰

④ 热插拔引发的瞬间电压、电流脉冲

⑤ 电源供应器缺少过电保护装置及噪声滤波装置

⑥ 提供超过组件可操作的工作电源

⑦ 接地点反跳(接地点不足导致电流快速转换引起高电压)

⑧ 过多过强的ESD事件引发EOS

⑨ 其他设备的脉冲信号干扰

⑩ 不正确的上电顺序

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?