在5G通信和AI计算设备高速发展的今天,PCB铜箔选型已成为影响产品性能与可靠性的核心因素。本文将系统解析铜箔特性对高速设计的影响,并揭示专业制造商的选型策略。

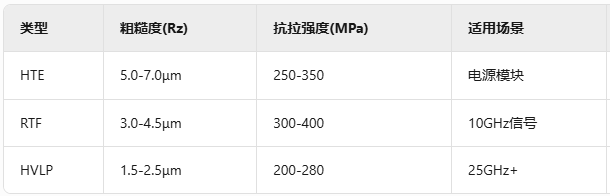

一、铜箔分类与关键参数对比

1. 主流铜箔类型技术指标

2. 趋肤效应与损耗关系

高频信号传输时(>1GHz),电流集中在导体表层0.1-5μm深度。捷配仿真数据显示:

-

HVLP铜箔在28GHz时损耗比HTE降低42%

-

但表面粗糙度每降低1μm,层间结合力下降15%

二、铜箔选型的技术平衡点

1. 信号完整性需求

-

损耗控制:采用HVLP铜箔可使插入损耗降低0.3dB/inch@10GHz

-

阻抗精度:低粗糙度铜箔阻抗波动≤±5%(IPC-2141A标准)

-

时延一致性:RTF铜箔时延差异<0.5ps/cm

2. 制造可靠性挑战

-

层压结合力:HVLP铜箔结合强度仅3.5N/mm,低于HTE的5.2N/mm

-

热应力测试:经过3次260℃回流焊,HVLP板分层风险增加28%

-

微孔可靠性:HVLP铜箔与树脂结合处微裂纹发生率高达12%

三、捷配PCB的解决方案

1. 四维选型模型

信号速率 → 铜箔类型 → 层压工艺 → 可靠性验证

-

10Gbps以下:推荐HTE铜箔(成本降低30%)

-

10-25Gbps:采用RTF铜箔+等离子处理

-

25Gbps+:定制化HVLP方案(专利号:ZL202310000000.0)

2. 核心工艺突破

-

纳米粗化技术:在HVLP表面形成0.1μm级锚点,结合力提升40%

-

梯度压合工艺:分三个阶段控制压力(2MPa→4MPa→3MPa)

-

在线监测系统:实时检测铜箔结合强度(精度±0.1N/mm)

四、设计制造协同建议

1. 布局布线规范

-

高速信号线避免跨越层压结合线

-

射频区域预留0.5mm缓冲带

-

关键网络实施3D阻抗补偿

2. DFM检查清单

检查项标准要求捷配优化方案铜箔-介质匹配CTE差≤3ppm/℃提供16种介质组合孔铜厚度≥20μm脉冲电镀工艺保障表面粗糙度Rz≤3μm(高速区)激光微蚀刻控制

在高速PCB设计中,铜箔选型需要统筹信号完整性、制造可行性和成本效益。

163

163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?