一种基于玻纤布间距匹配的创新设计思路在业内引发热议,但其在PCB打样中的实际应用却鲜有踪迹。

一、玻纤效应的常规应对策略

目前PCB打样中主要采用三种抑制玻纤效应的方法:

-

材料升级:采用扁平开纤布减小经纬纱间隙,使玻纤布Dk值从常规的6.8降至4.8,同时通过叠合双层PP提高介质均匀性

-

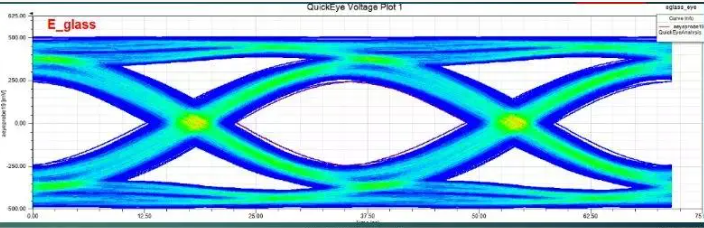

走线优化:采用10°斜向布线或Zig-zag走线,规避0°/90°的玻纤束方向。

-

制程调整:将PCB基板旋转5-15°(牺牲10-15%板材利用率)

这些方法虽有效,但都存在明显缺陷:材料升级显著增加成本,角度布线降低布线密度,制程旋转加剧拼板难度。

二、理想方案遇冷的技术困局

尽管仿真数据亮眼,该方案在实际PCB打样中却面临三重障碍:

1. 材料规格的微观波动

-

玻纤布实际间距存在±1.5mil公差

-

树脂填充率波动导致有效介电常数偏差±0.2

2. 设计灵活度的刚性制约

-

差分线宽/间距需严格匹配特定玻纤规格(如1078要求18.5mil间距)

-

高速接口区域布线密度下降40%,BGA逃逸布线成功率降低

-

跨层走线时需同步调整相邻层玻纤方向(增加30%设计工时)

3. 成本控制的边际效应

-

需采用高精度玻纤布(成本是常规材料2.3倍)

-

板材利用率下降导致的隐性成本(每平方米增加¥80)

四、PCB打样的实践启示

对于寻求玻纤效应解决方案的工程师,建议采取分级策略:

应用场景推荐方案实施要点40Gbps+设计1078/1035材料+5°旋转优先控制插损波动10-28Gbps设计常规材料+10°布线重点关注模态转换指标成本敏感型设计玻纤间距匹配配合TDR测试验证

在PCB打样领域,玻纤效应的终极解决方案尚未出现。但正是这种技术矛盾的存在,推动着材料科学与设计方法的持续革新。或许在不远的未来,我们终将找到那个既能完美匹配玻纤结构,又不牺牲设计自由度的黄金平衡点。

112

112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?