高速数字电路与精密模拟系统并存的现代电子设备中,四层PCB的信号隔离设计已成为决定产品可靠性的核心技术。

一、分层架构的底层逻辑优化

1.

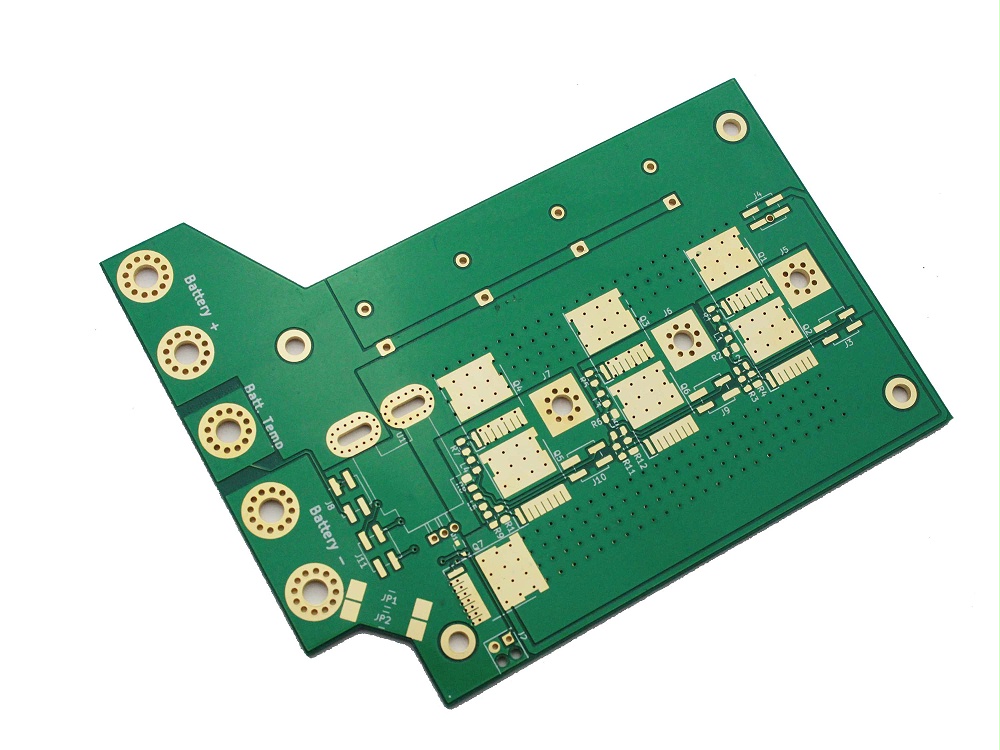

采用"信号-地-电源-信号"结构(TOP-Signal/GND-Power/Bottom-Signal),关键参数配置需满足:

-

信号层到地平面间距≤6mil,实现阻抗波动率<5%

-

电源层与地平面间距4-6mil(FR4材质),形成75pF/平方英寸的平面电容

-

底层信号优先布设低速总线,保留30%无铜区域用于散热

2.

-

物理隔离:模拟区(传感器/ADC)与数字区(MCU/FPGA)间距≥10mm

-

混合器件处理:将ADC/DAC作为"噪声边界",模拟引脚朝模拟区,数字引脚朝数字区

-

电源网络隔离:模拟电源与数字电源在入口处通过磁珠单点连接,分割线宽度≥50mil

二、关键信号隔离技术规范

1.

-

地线包围:在关键信号线两侧布置0.5mm地线,每隔2mm打地过孔,实测降低8-12dB高频噪声

-

差分对传输:跨区信号采用差分线传输,线距保持2倍线宽(如6mil线宽对应12mil间距)

-

三明治走线:时钟信号上下层均为地平面,线宽6mil并串联22Ω电阻,辐射噪声降低5-7dB

2.

-

L型电流路径:大电流走线总长≤15mm,采用2oz厚铜使压降减少30%

-

去耦电容阵列:在电源分割线两侧布置0.1μF+10μF电容,形成π型滤波结构

-

盲埋孔应用:HDI设计中采用0.1mm激光孔替代机械孔,减少30%空间占用

三、地平面处理的进阶技巧

1.

-

相比分割地平面,完整地平面可使数字噪声回路阻抗降低40%,实测地弹噪声从120mVpp降至50mVpp

-

特殊场景处理:高精度测量电路实施"铜皮挖空+磁珠桥接",挖空区面积<芯片封装1.5倍

2.

-

地过孔伴随:信号换层时,在过孔周围1mm布置4个对称地过孔,回流路径电感从3nH降至0.8nH

-

正交布线原则:顶层与底层信号走线垂直交叉,串扰减少40%

3.

-

板边5mm区域布置λ/20间距地过孔阵列(如2.4GHz电路间距6mm),辐射降低30%

-

隔离带设置0.4mm宽环氧树脂填充槽,阻断电磁耦合路径

四、EMC/EMI专项优化方案

1.

-

SW节点开窗设计,铜箔扩展面积≥20mm²

-

采用X电容+共模电感构成π型滤波电路,噪声衰减≥15dB

-

敏感区域设置环形屏蔽过孔阵列(间距≤5mm)

2.

-

电源入口布置TVS管+RC滤波器,响应时间<1ns

-

数字电路区域铺0.1mm厚铜箔屏蔽层,接地过孔密度≥50个/in²

五、量产级工艺控制标准

1.

-

基材:FR-4(TG≥170℃),高频场景选用罗杰斯4350B

-

磁芯:铁硅铝材料(A19/μ02300)降低漏感至5%以下

-

绝缘胶带:3M1206(CTI≥600V)满足安规要求

2.

-

贴片温度:245℃±5℃持续60s,避免焊点虚焊

-

波峰焊预热:220℃±10℃维持30s,防止基板变形

-

三防处理:丙烯酸涂层厚度50μm,盐雾测试通过96小时

168

168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?