W25Q128

器件的基本介绍

-

W25Q128是一个可以存储声音、文本和数据的一个芯片,支持双/四SPI

-

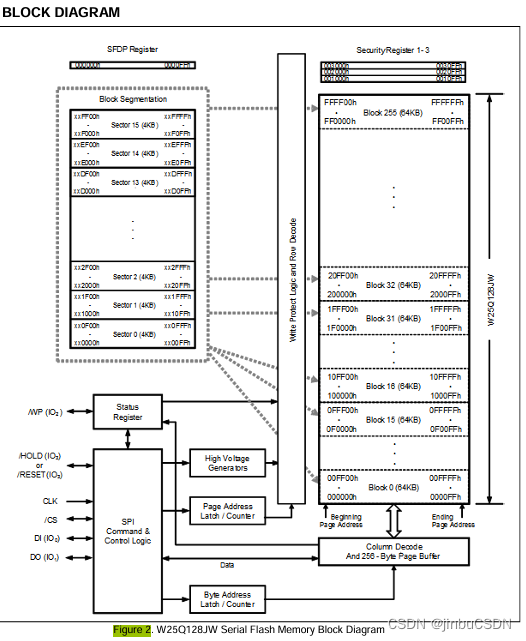

W25Q128的存储架构

-

存储架构:256块,每块有16个扇区,每个扇区有16页,每页有256个字节

-

容量的计算(2^8x2^4x2^4x2^8=2^24字节B=2^14KB=2^4MB=16MB 、1kB=2^10B、1MB= 2^10KB、

-

W25Q128JW支持标准串行外设接口(SPI)、双SPI、四SPI:串行时钟、片选信号、串行数据I/O0(DI)、I/O1(DO)、I/O2和I/O3,支持的时钟最大是133MHz

-

特性

-

器件名称、容量、接口

-

存储架构:

框图、内部结构

-

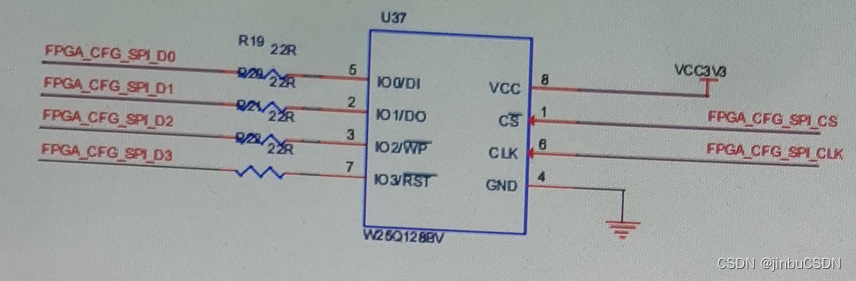

PCB图

-

框图

-

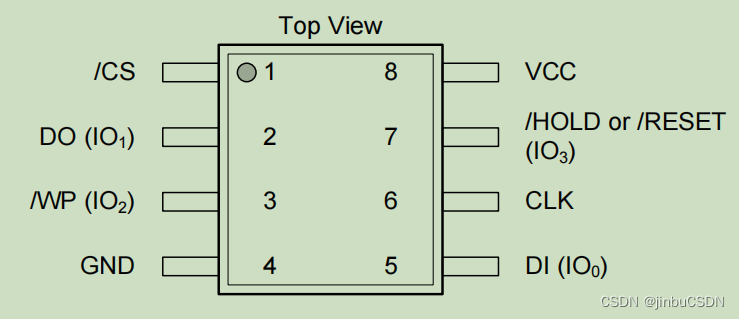

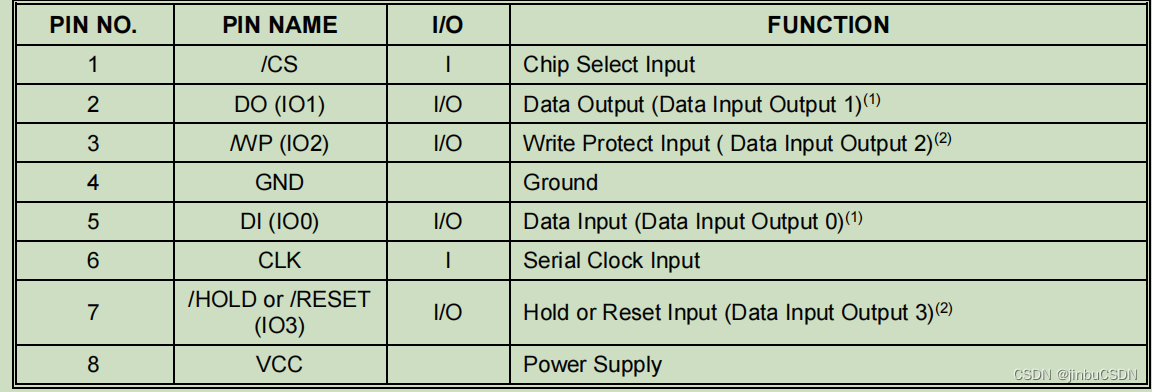

引脚说明

-

CS片选信号、低电平有效

-

DO数据输出

-

DI数据输入

-

CLk 时钟信号

-

时序

-

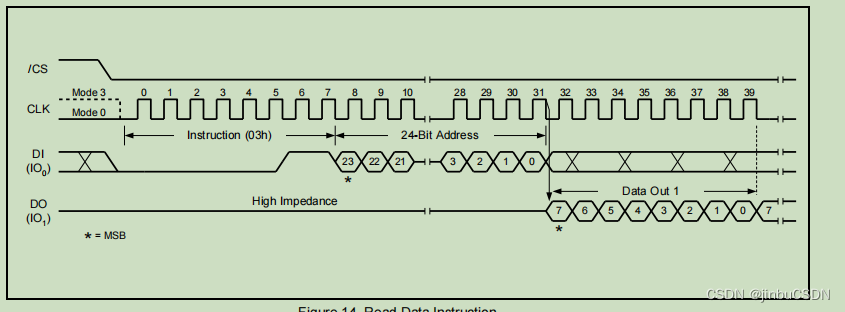

标准SPI接口,支持模式0和模式3,模式0空闲状态下SCK为低电平,模式3空闲状态下SCK为高电平

-

指令部分:要发送指令,是FPGA向Flash发送

-

Write Enable写使能06h

-

除了读之外,在执行所有的操作指令之前都有先发送写使能指令,然后Flash才能正常工作,状态寄存器写使能指令位置1;

-

发送写使能时序

-

一次发8bit,高位先发

-

-

Read Data 页读03h

-

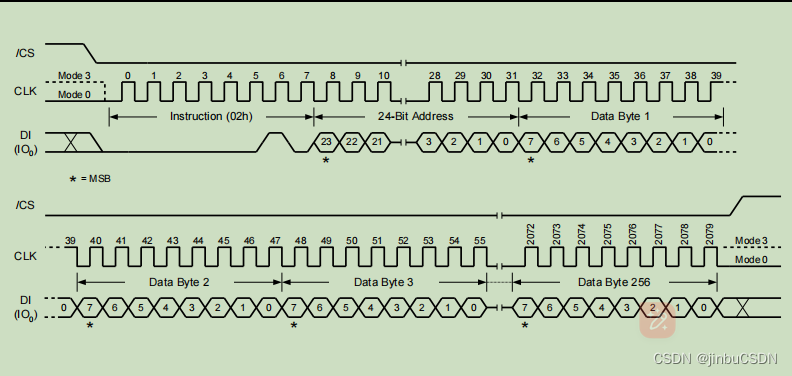

Page Program 页写02h

-

页写之前要先进行全擦除,然后再发送页写指令+地址+数据

-

最多一次发送256字节,

-

-

Chip Erase 全擦除C7h/60h

-

全擦除指令的作用是将寄存器全部为1;

-

全擦除指令发送前,要先发送写使能指令,全擦除完成后状态寄存器中的写入启用锁存器(WEL)位将重新变为0。

-

等待时间

-

发送全擦除指令时序

-

C7-1100_0111,60h-0110_0000

-

-

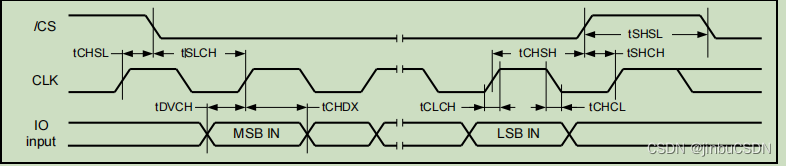

串行输入时序

-

注:

-

除了读数据以外,时钟频率最大为104MHz

-

读数据时钟频率最大为50MHz

-

CS建立时间向对于CLK:tSLCH最小5ns,tCHSH最小3ns

-

tSHSL读的时候最小为10ns,擦除或写的时候最小为50ns

946

946

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?