描述

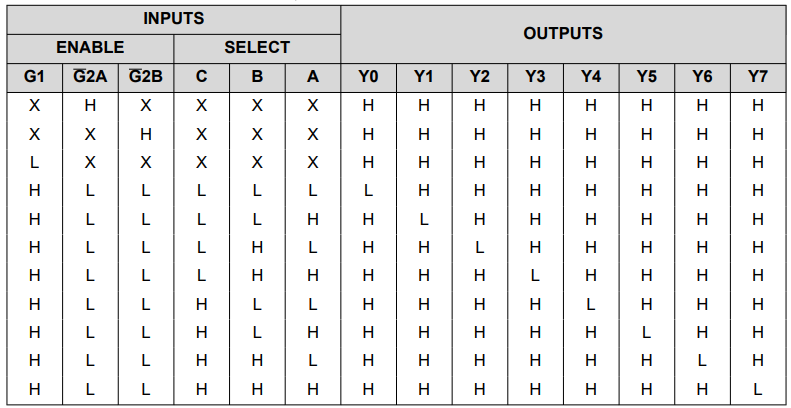

下表是74HC138译码器的功能表.

| E3 | E2_n | E1_n | A2 | A1 | A0 | Y0_n | Y1_n | Y2_n | Y3_n | Y4_n | Y5_n | Y6_n | Y7_n |

| x | 1 | x | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| x | x | 1 | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | x | x | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

①请用基础门电路实现该译码器电路,用Verilog将电路描述出来。基础门电路包括:非门、多输入与门、多输入或门。

输入描述:

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 输出描述:

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n 解题分析

3-8译码器

3-8译码器也是数字电路的基础之一。

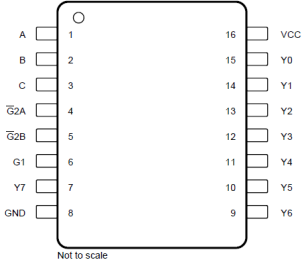

引脚图:

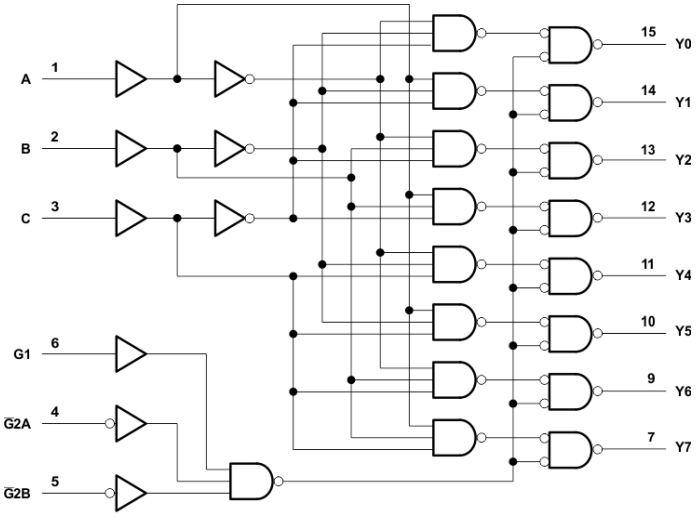

电路图:

真值表:

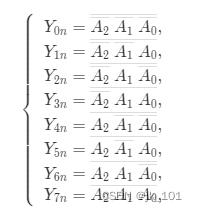

关系式:

当片选输入端E3==1且E2_n+E1_n==0时,输入输出有下述关系:

当片选输入端E3==0或者E2_n+E1_n==1时, 输出全部都是1。

参考代码

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

reg Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r;

always@(*) begin

casez({E3, E2_n, E1_n, A2, A1, A0})

6'b?1?_???: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1111;

6'b??1_???: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1111;

6'b0??_???: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1111;

6'b100_000: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b0111_1111;

6'b100_001: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1011_1111;

6'b100_010: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1101_1111;

6'b100_011: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1110_1111;

6'b100_100: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_0111;

6'b100_101: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1011;

6'b100_110: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1101;

6'b100_111: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1110;

default: {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r} = 8'b1111_1111;

endcase

end

assign {Y0_n, Y1_n, Y2_n, Y3_n, Y4_n, Y5_n, Y6_n, Y7_n} = {Y0_r, Y1_r, Y2_r, Y3_r, Y4_r, Y5_r, Y6_r, Y7_r};

endmodule

注:解题分析来源于网友,如有侵权,请告删之。

1274

1274

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?