在初学FPGA时,对于模块输入/输出端口类型定义,以及在top_down模块调用、testbench例化时常常会遇到端口类型定义模糊的情况,是reg型还是wire型?

模块端口声明

在verilog中的端口具有以下三种了类型:input、output、和inout。所有的端口隐含地声明为wire类型

如果输出类型的端口需要保存数值,则必须将其显式的声明为reg数据类型。output reg out;

input和inout类型的端口声明必须位wire型,因为reg类型的变量是用于保存数值的,而输入端口只反映与其相连的外部信号的变化,并不能保存这些信号的值。

对于模块的具体定义类型得从内部外部来分析这样更容易理解

输入端口

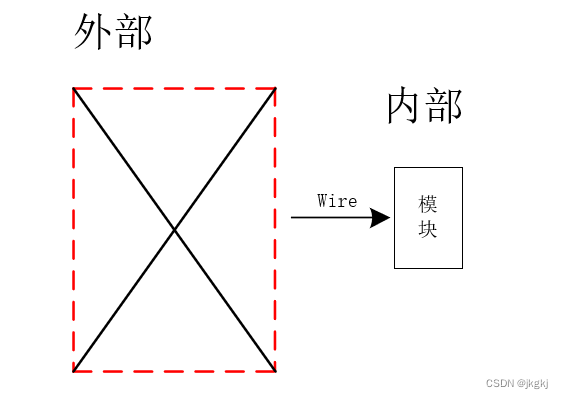

从模块自身(内部)来说,输入端口必须为wire(线网)型,他是从模块自身这个角度来看的,外部可看为黑盒,不论外部是哪种形式的信号,“我”只接收wire型

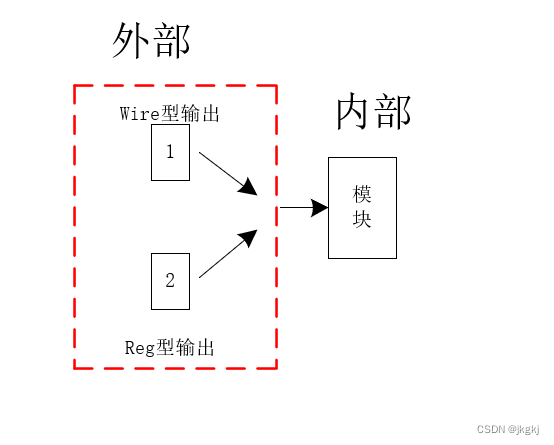

从外部模块的角度来看,输入端口可连接到wire或者reg数据类型的变量,这常常在top_down设计模块调用,以及tesbench模块例化的时候会遇到这种情况。

输出端口

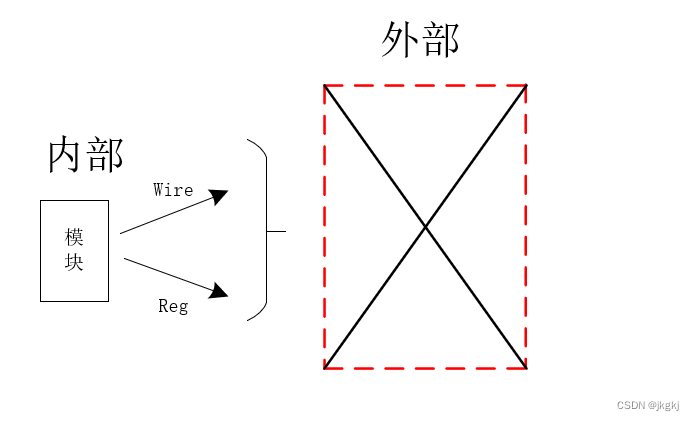

从模块内部来讲,输出端口可以是线网或者reg数据类型

从模块外部来看,输出必须连接到线网类型的变量,而不能连接到reg类型的变量。

输入/输出端口

从模块内部来讲,输入/输出端口必须为线网数据类

从模块外部来看,输入/输出端口也必须连接到线网类型的变量

299

299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?