FPGA编程入门

文章目录

一、1位全加器

1. 原理图

1.1. 半加器

创建工程过程

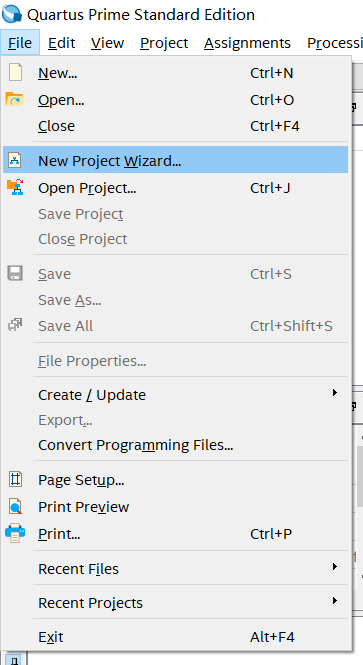

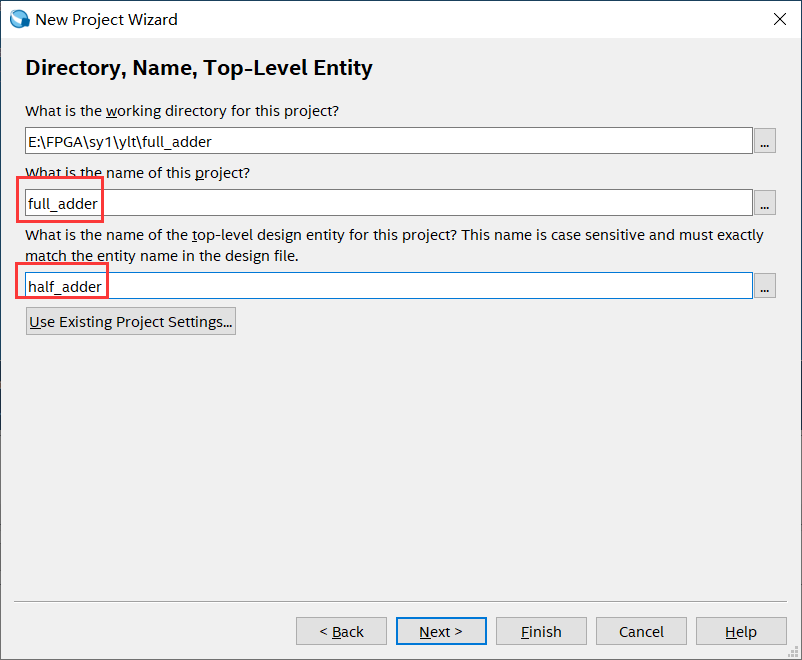

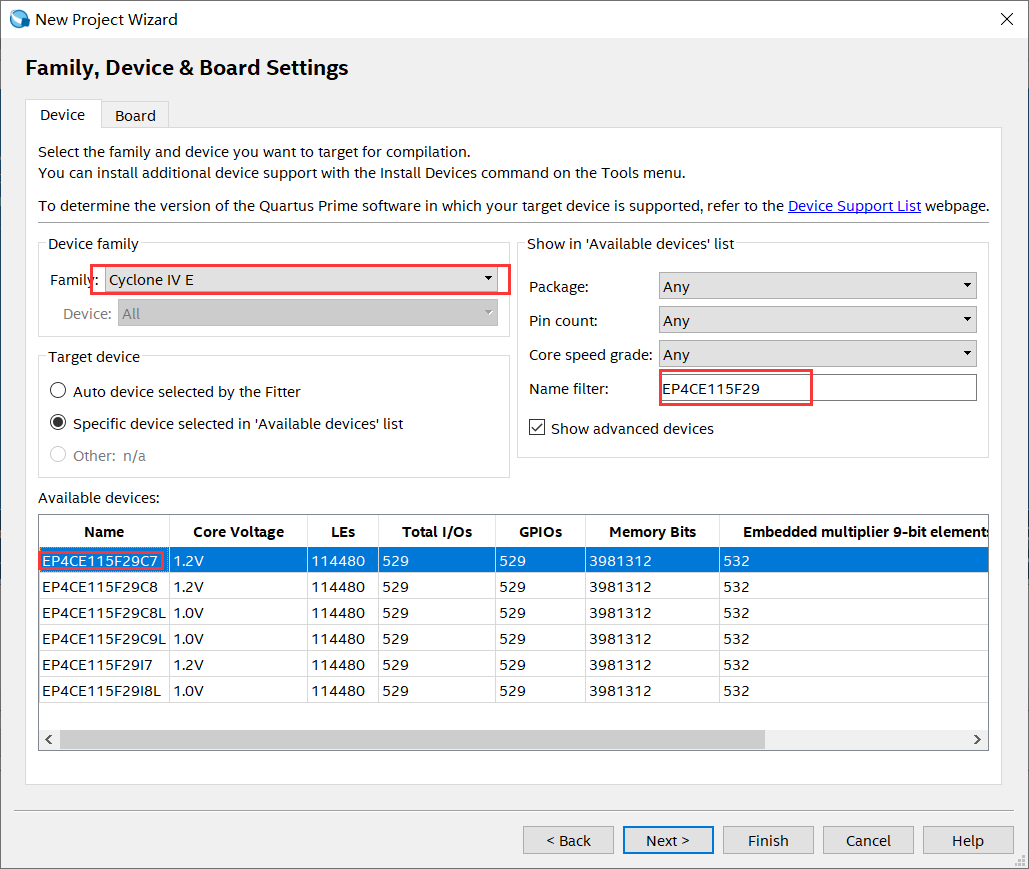

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

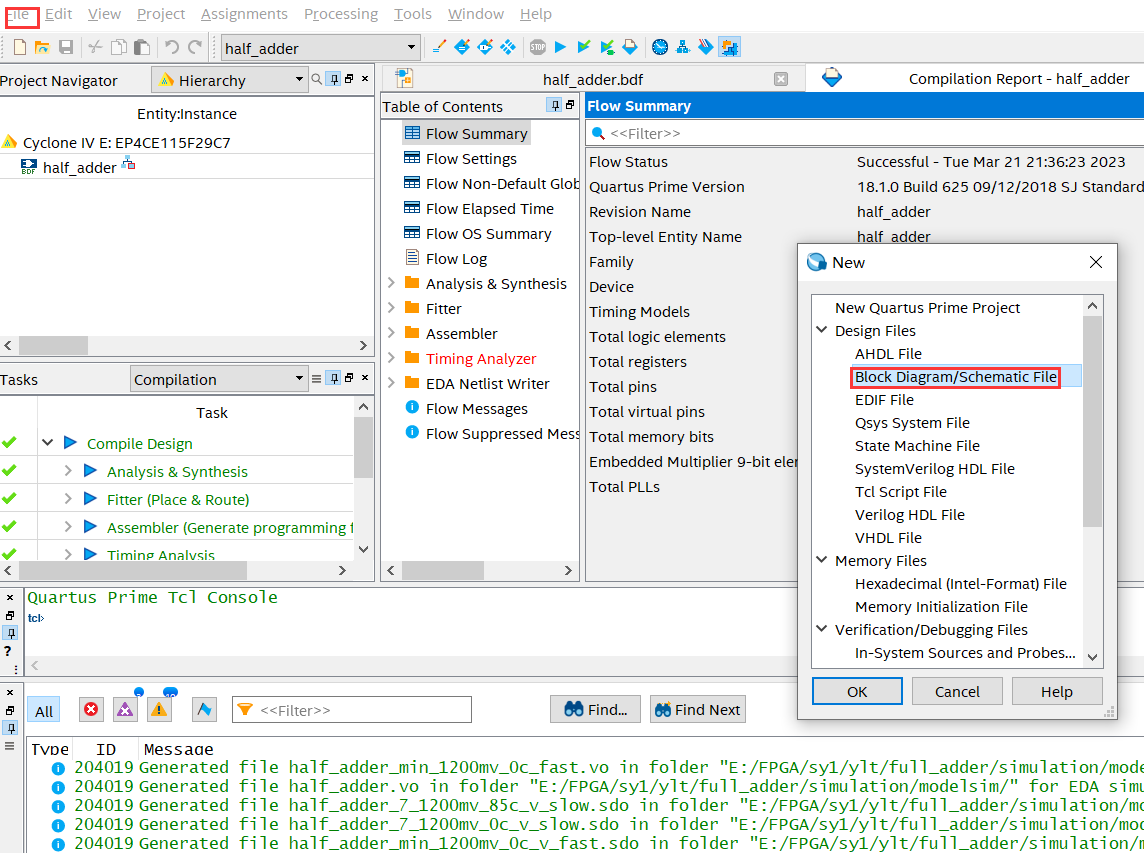

首先选择File->New,进入后选择Block Diagram/Schematic File

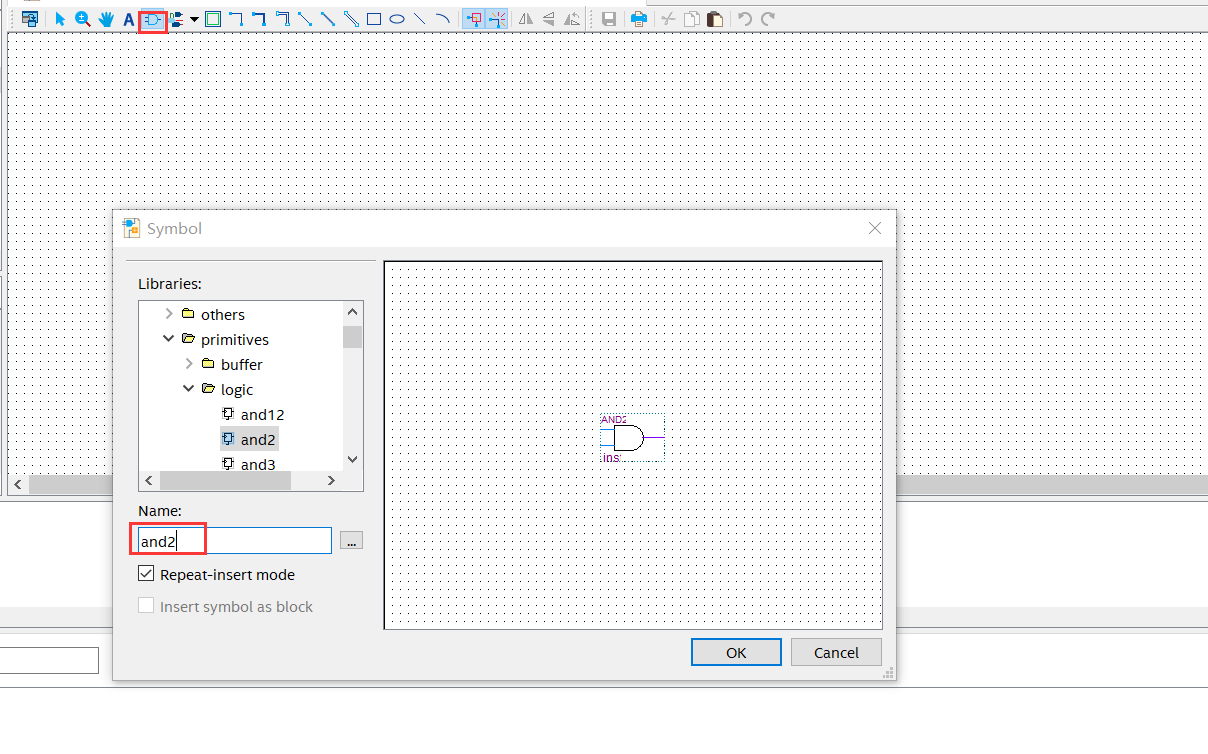

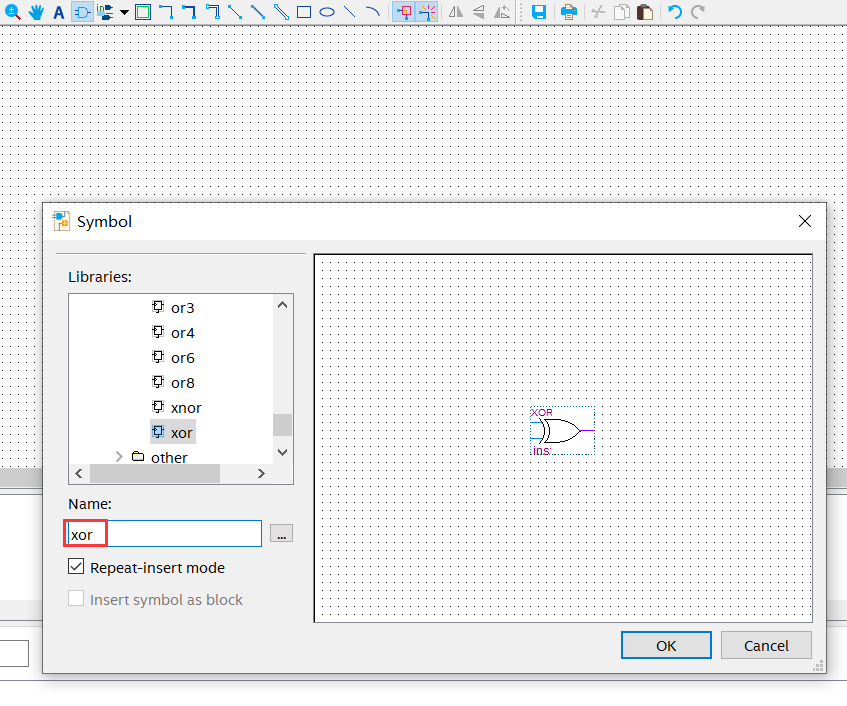

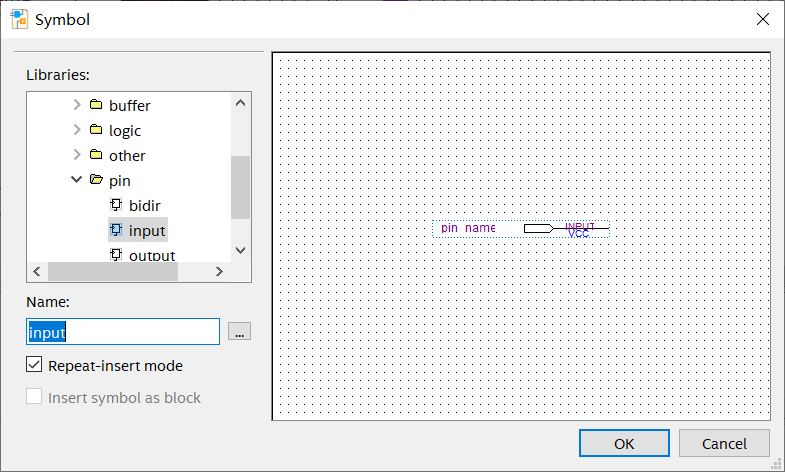

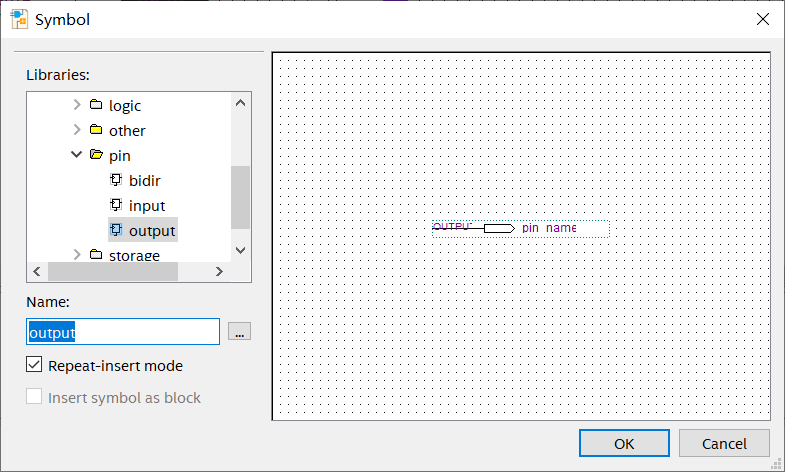

选择元件

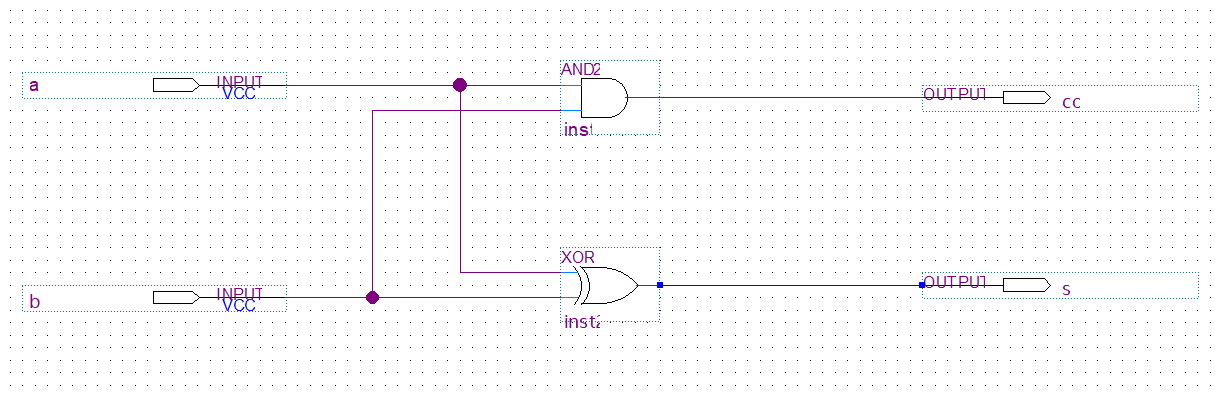

原理图

保存文件,并编译

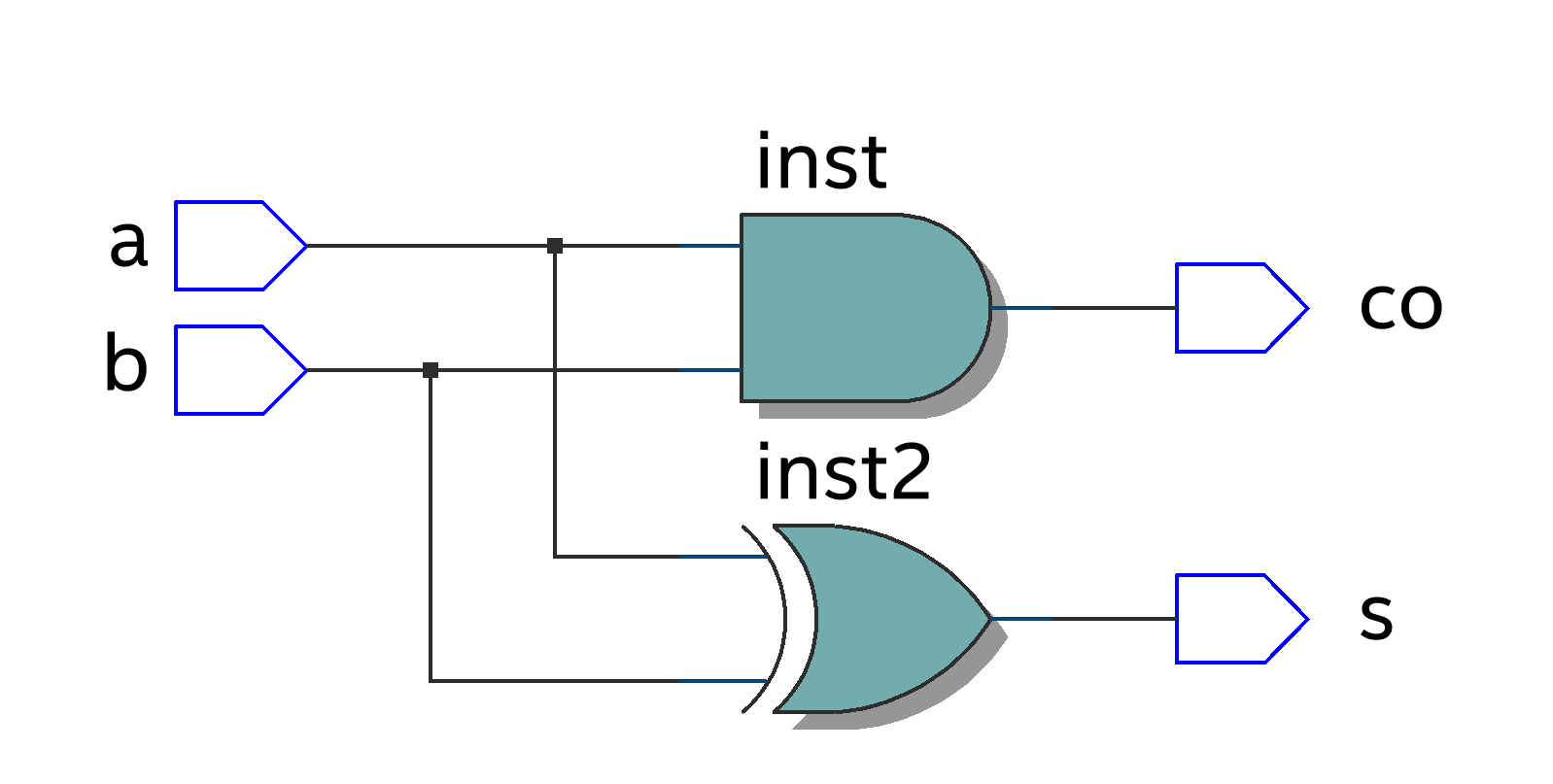

通过tool->Netlist Viewers->RTL Viewer,查看电路图

仿真模拟:

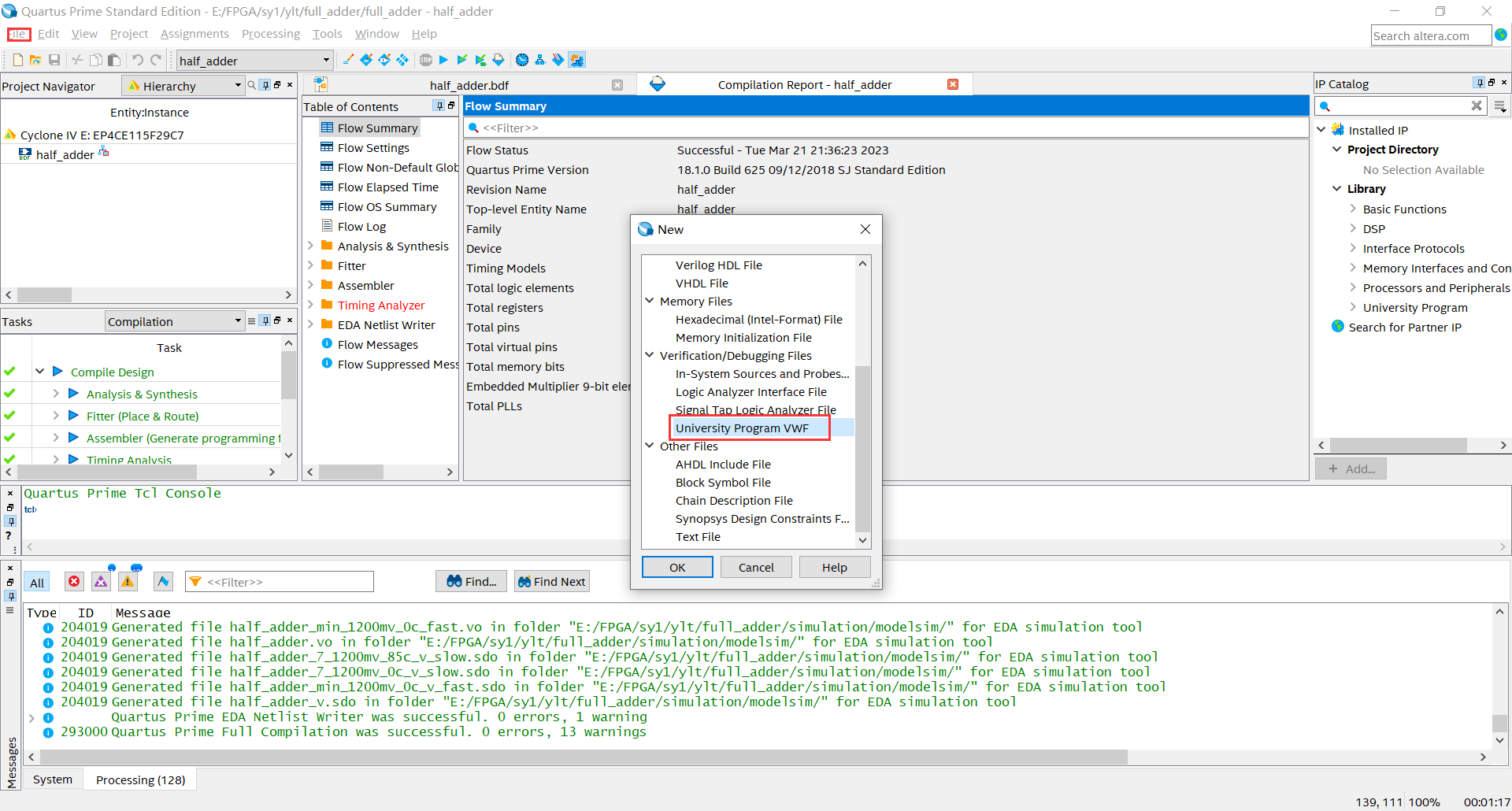

创建一个向量波形文件,选择菜单项 File→New->VWF

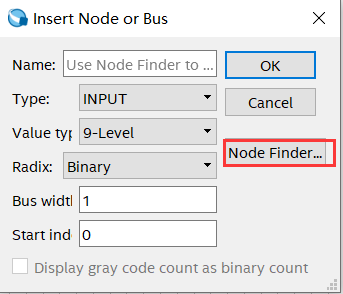

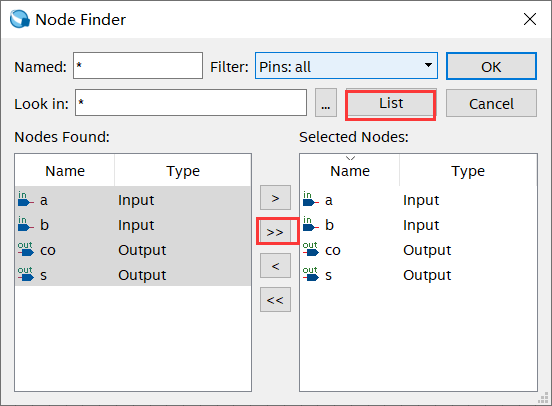

在波形文件编辑器左端大片空白处双击,出现“insert node or bus”对话框,点击“node finder”按钮。

添加信号

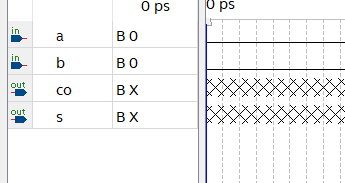

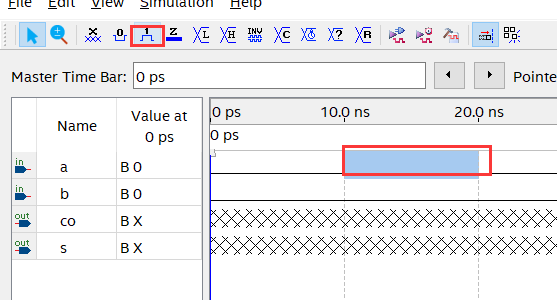

编辑信号

保存文件并启动功能仿真,结果如下

1.2 全加器

利用半加器元件实现全加器

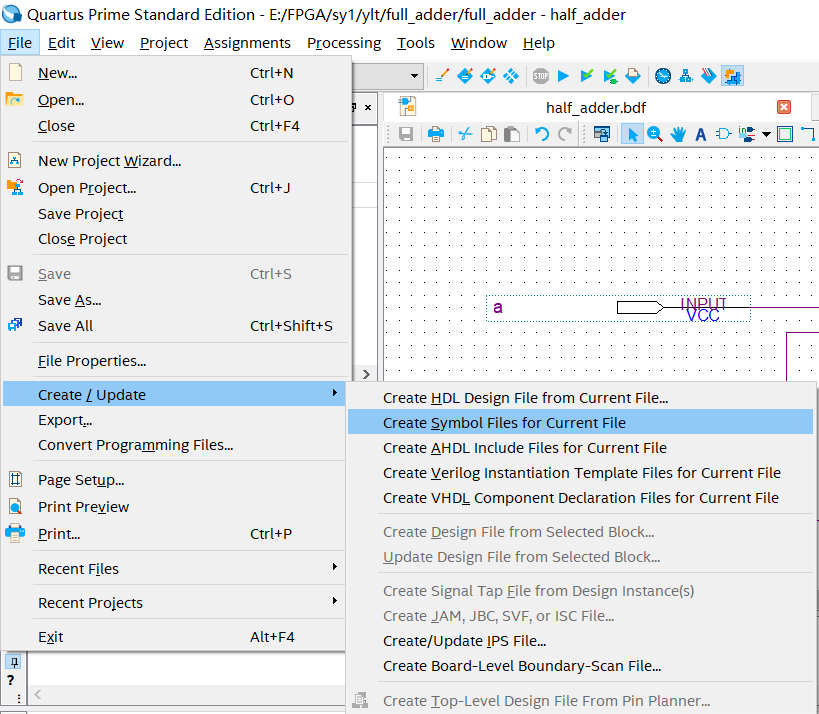

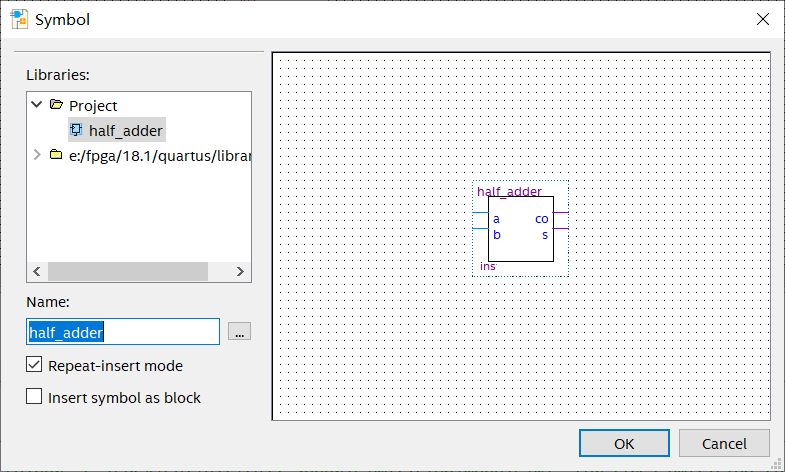

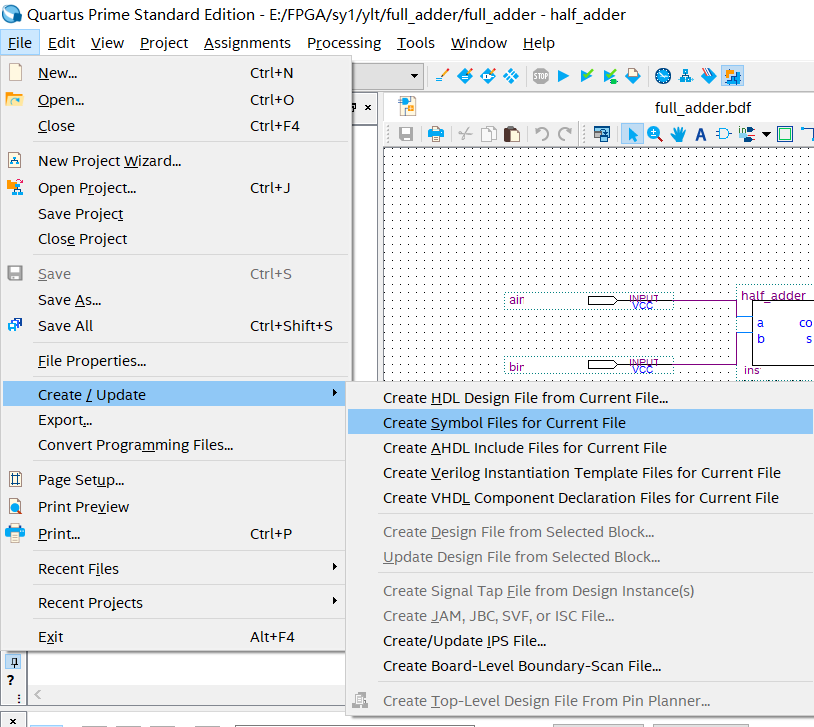

将设计项目设置为可调用的元件

在打开半加器原理图文件half_adder.bdf的情况下,选择菜中File中的Create/Update→CreateSymbolFilesforCurrentFile项,即可将当前文件h_adder.bdf变成一个元件符号存盘,以待在高层次设计中调用

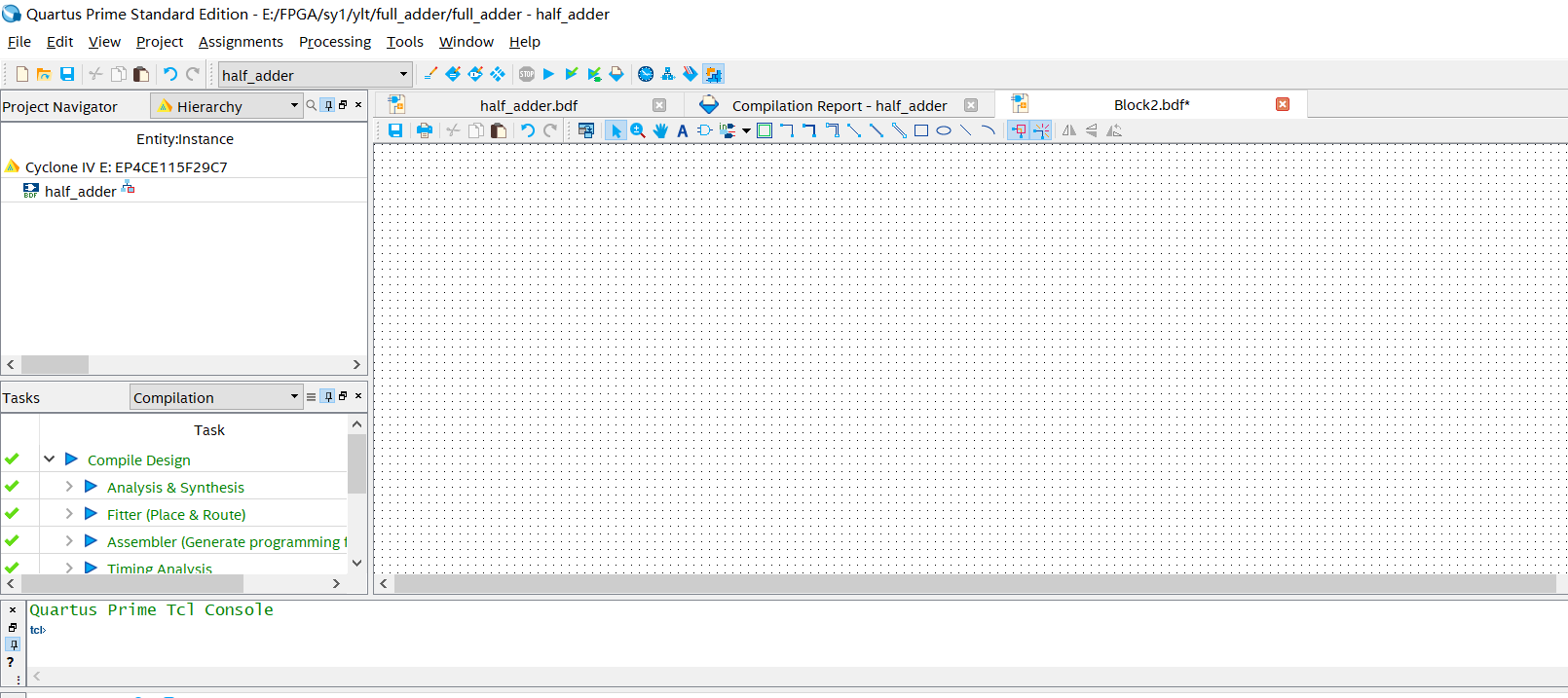

选择File->New,进入后选择Block Diagram/Schematic File

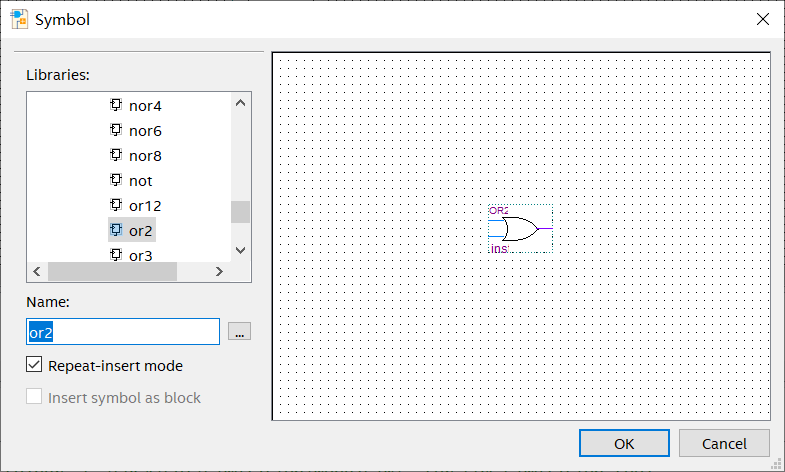

同上面一样,选择元器件

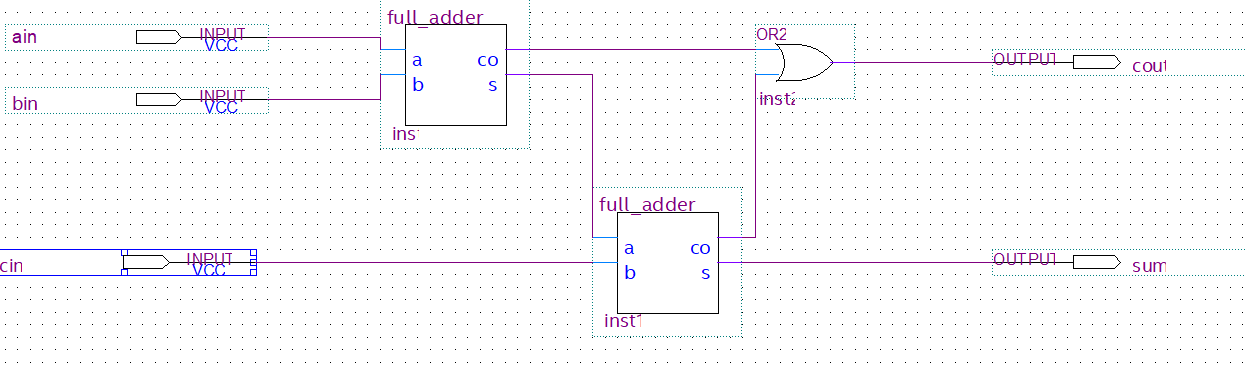

原理图如下

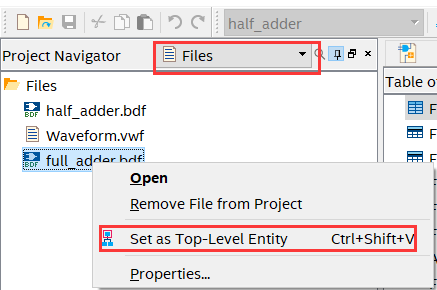

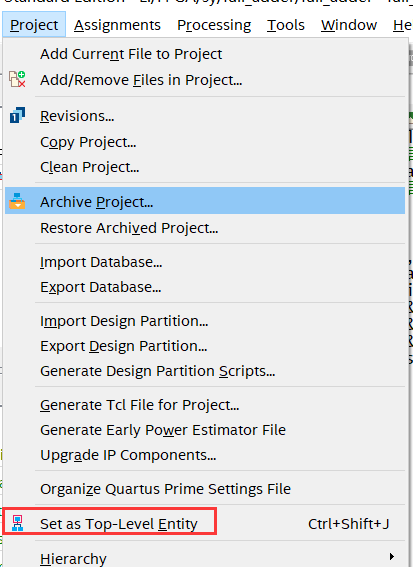

将全加器设置为顶层文件

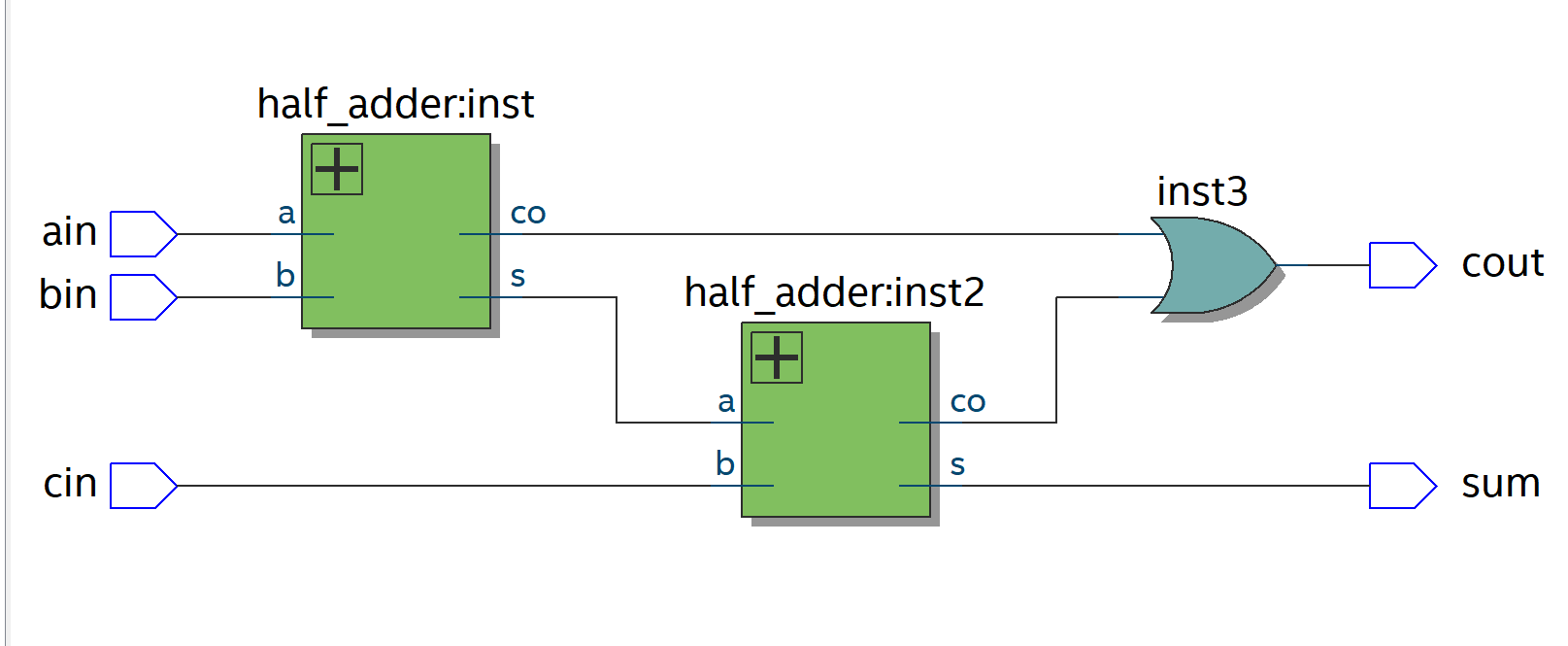

编译,查看RTL

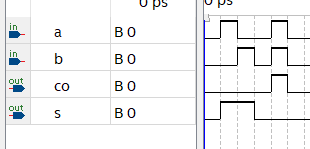

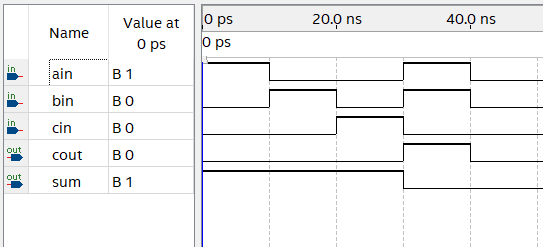

仿真模拟:

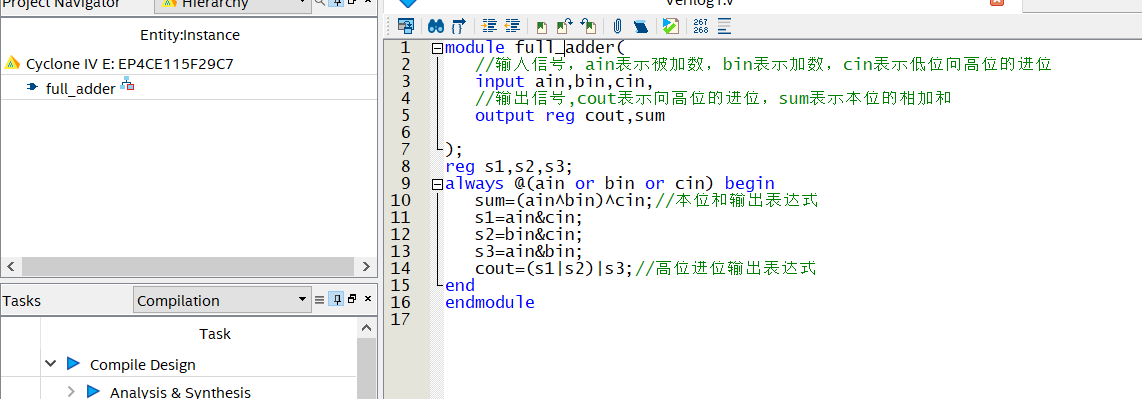

2. verilog实现1位全加器

重头开始创建一个项目,选择verilog HDL FILE

2.1 代码

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

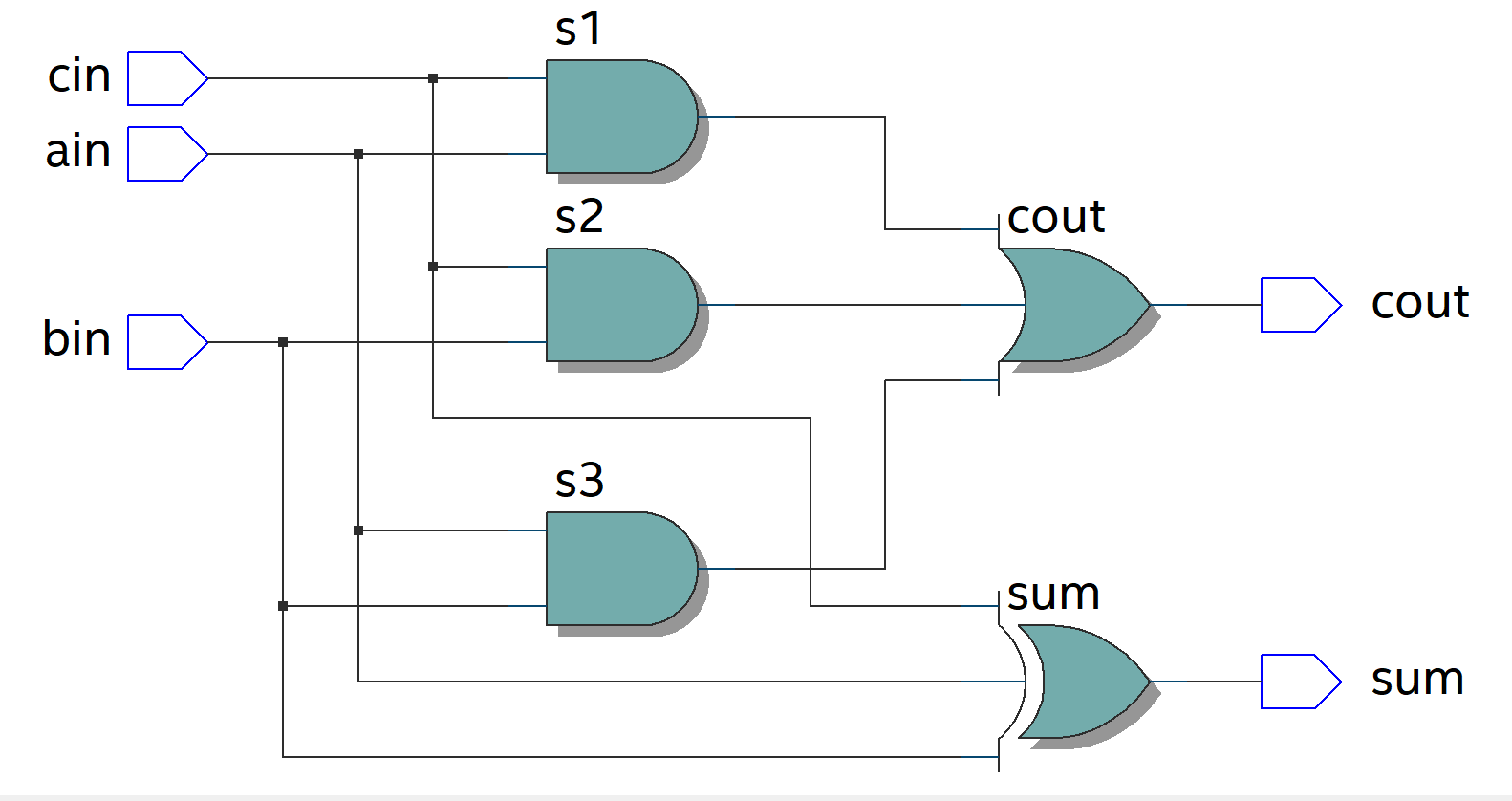

2.2 编译,查看RTL

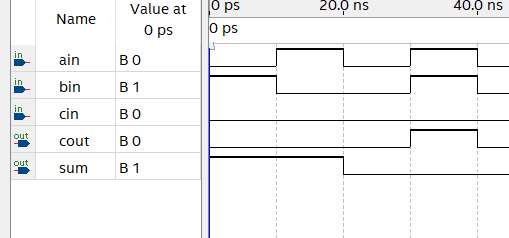

2.3 仿真实现

二、烧录到FPGA板上

将其设置为顶层文件

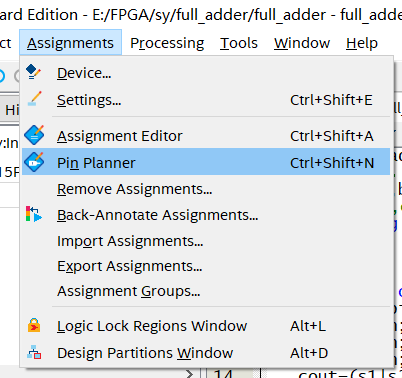

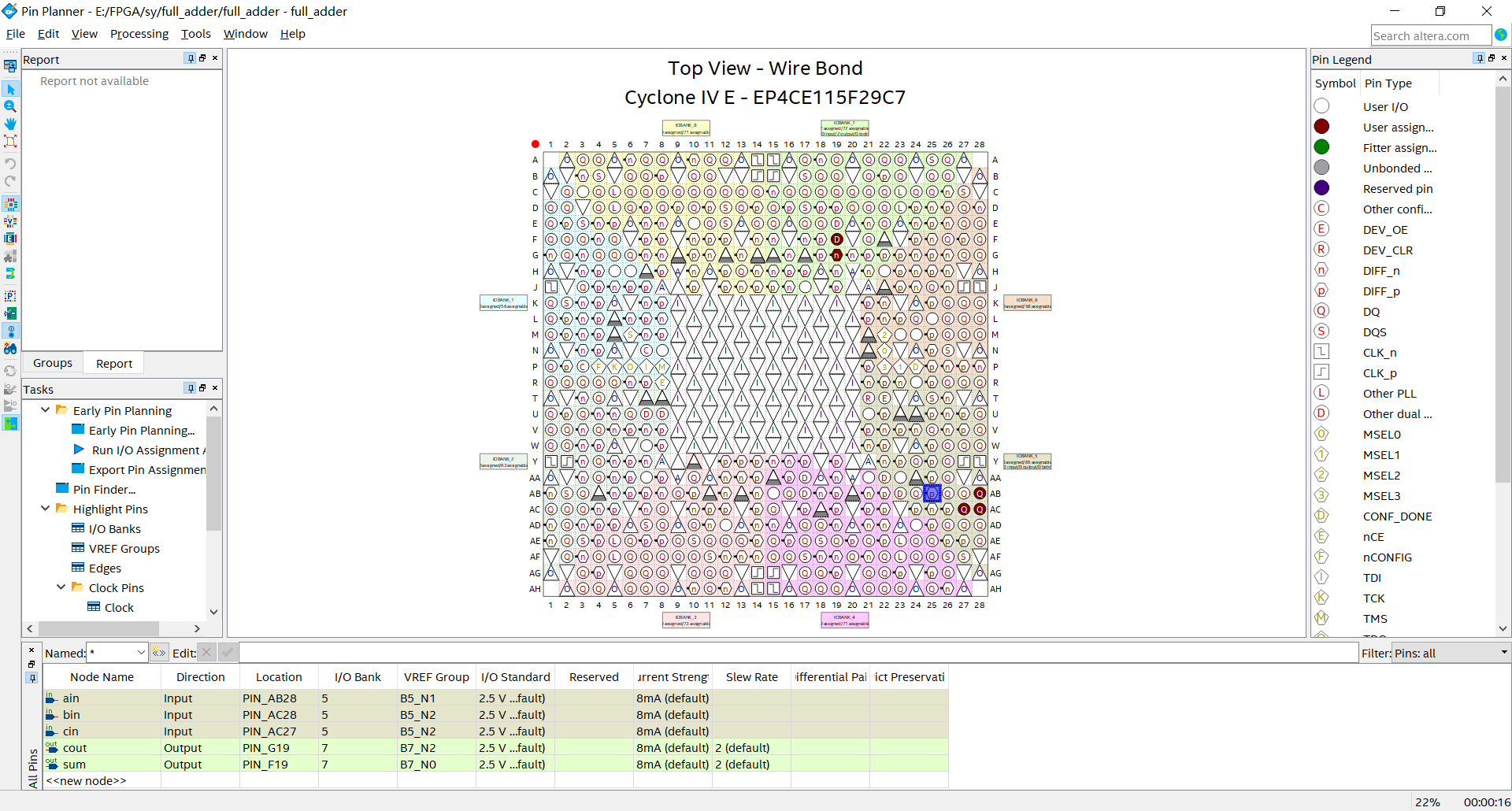

设置管脚

再编译一次

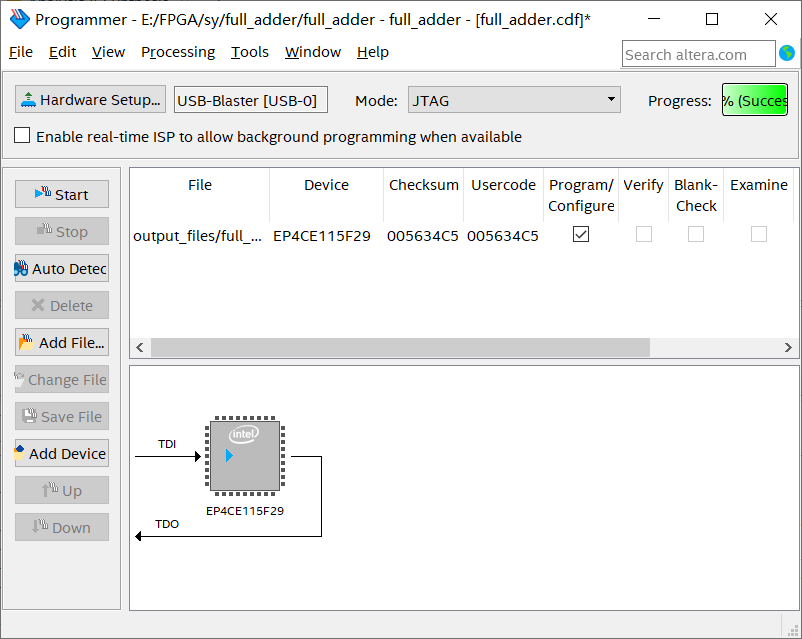

烧录

效果:

三、4位全加器

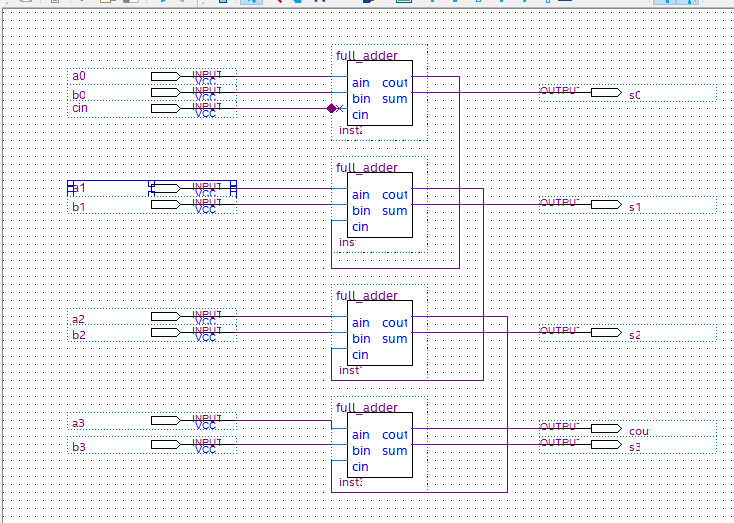

1. 原理图实现4位全加器

将1位全加器保存为元件

新建空白图层,搭建4位全加器

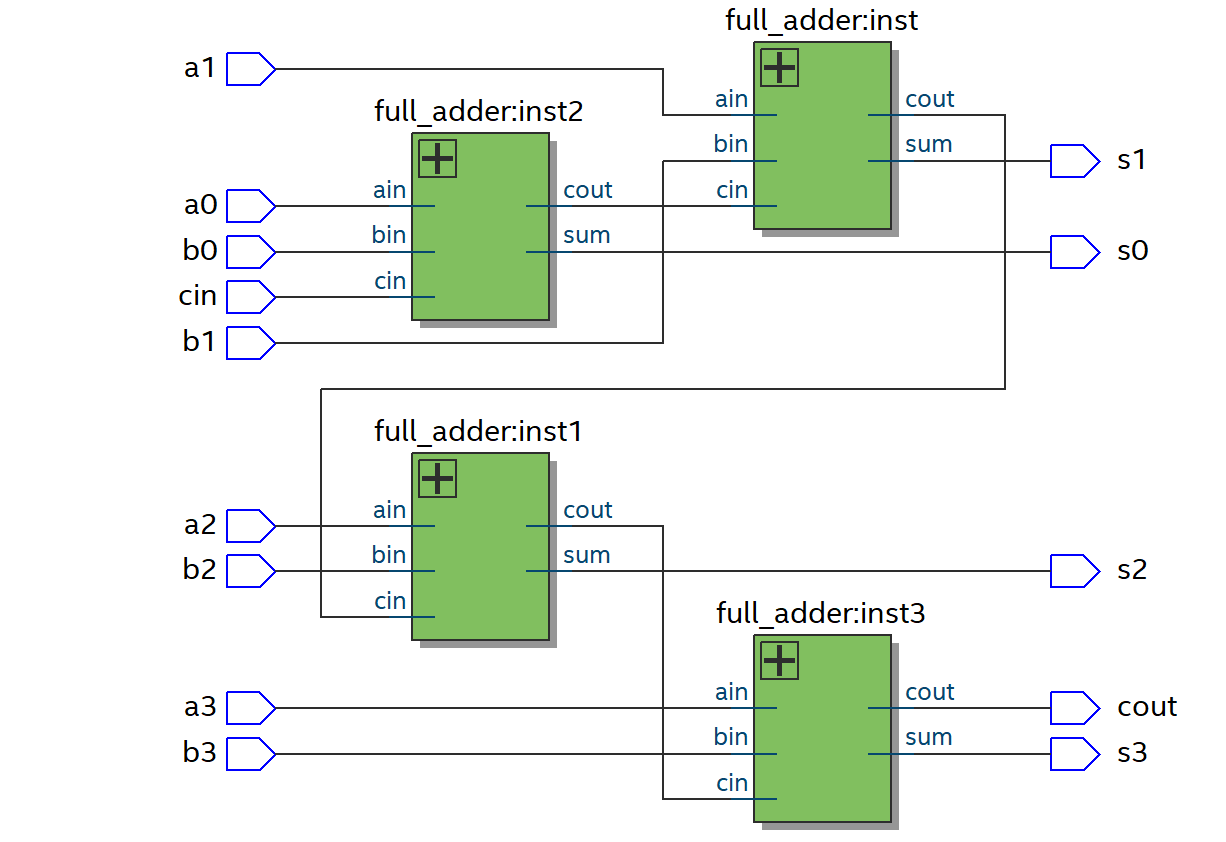

RTL

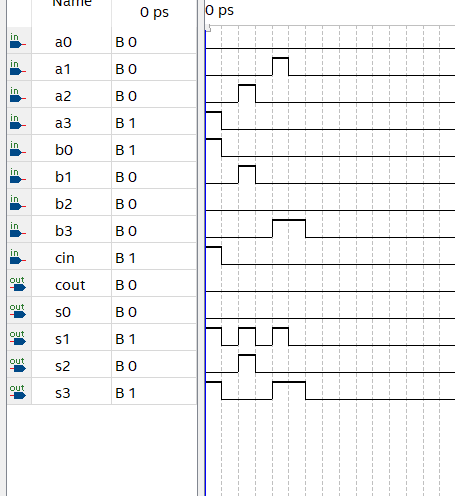

仿真实现:

2. verilog实现4位全加器

2.1 代码

module full_adder4(

input[3:0] a,b,

input cin,

output[3:0] sum,

output cout

);

assign{cout,sum} = a+b+cin;

endmodule

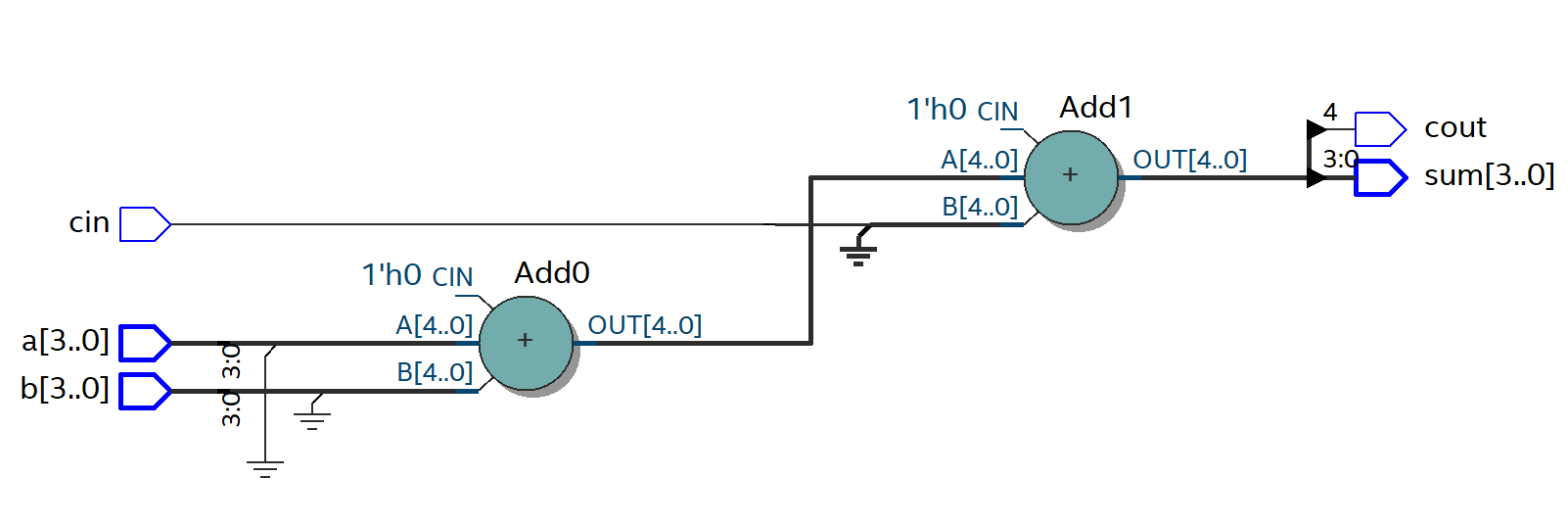

2.2 RTL

2.3 仿真实现

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-NTPoquER-1679451545698)(https://gitee.com/jiyny/pictures/raw/master/202303212052367.png)]

四、烧录

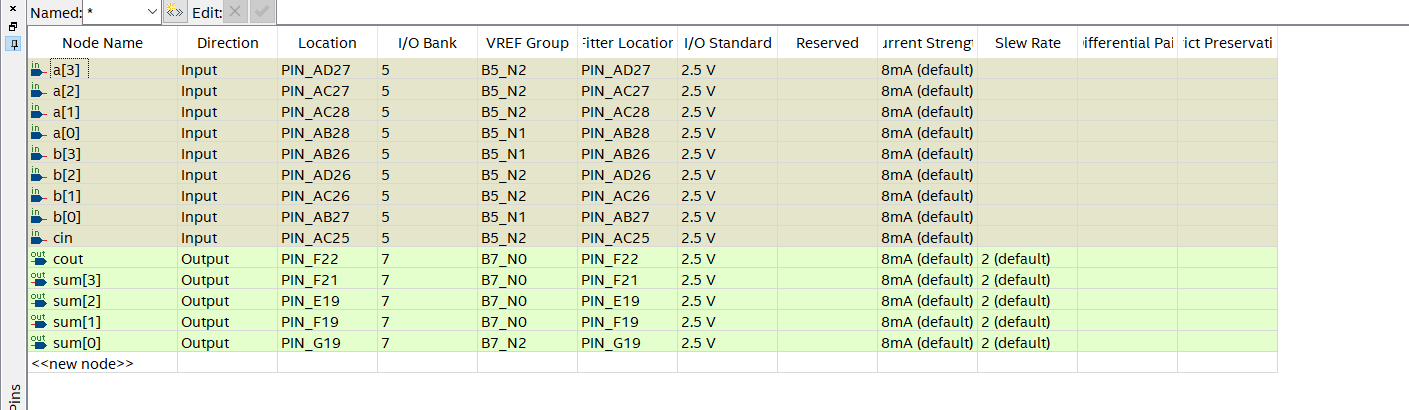

设置管脚

效果

五、总结

通过这次试验,掌握了项目的创建,原理图与verilog语言的编写,如何将写好的程序烧录到FPGA板中。也掌握了半加器,全加器的相关知识。

参考文章

https://blog.csdn.net/qq_43279579/article/details/115480406

https://blog.csdn.net/weixin_47554309/article/details/123743633

4650

4650

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?