PLL ,Phase-Locked Loop 锁相环

1、简单介绍

锁相环是一种反馈控制电路,其中电压控制振荡器和相位比较器 相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率 或相位调制信号的频率。锁相环可用来从固定的低频信号生 成稳定的输出频率信号。用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

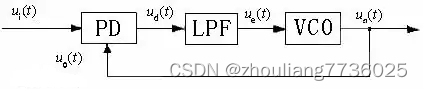

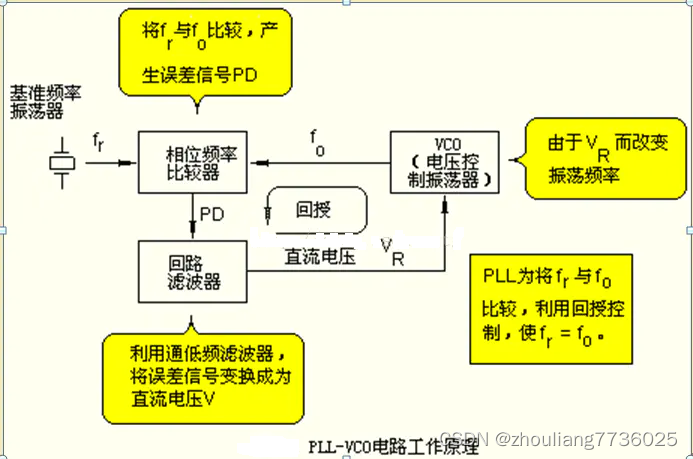

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图:

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

PLL里面的VCO在电压控制下可以输出一定范围内的各种各样频率的时钟。但是输出的时钟不稳定,数值和精度可能存在问题。为了解决精度和稳定的问题,将输出的时钟(分频后)和参考时钟进行比较通过负反馈处理,不断调整,得到(倍频后)稳定的高精度时钟。

2、PLL可以输出一个几倍或几十倍参考时钟的时钟.

3、特点

当一个电子产品需求多个晶体/谐振器, 特别是需求不同频率时,一个可以输出多路时钟信号的时钟发生器的成本比几个晶体/谐振器有优势。

由于产品特性,晶体/谐振器的失效率比硅芯片高很多。频率越高,失效率越高,会降低电子产品的可靠性。集成度更高的PLL时钟芯片可以提高电子产品的可靠性

高于50MHz的高频晶体由于需要使用高阶泛音晶体,生产工艺复杂,价格昂贵。PLL时钟芯片只需要一个低频晶体或一个可用的时钟参考就能产生多路高频高性能的时钟信号。

晶振容易老化。PLL时钟芯片可以在设备的整个生命周期中都保持其准确性。

2011

2011

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?