本文汇总常见接口信号的电平,包括I2C, SPI, UART, RS232, RS485, RS422, CAN, USB(2.0, 3.1),LVDS。其他接口如PCIE, MIPI, JTAG, 各种显示接口(VGA, HDMI, DVI),网口RJ45等混杂多种信号的通讯接口类型在这篇文章就不列举,有机会在后续的文章再单独描述。

1. TTL 与 CMOS

TTL: 三极管组成,包括集电极开路(OC)和推挽(push-pull)两种,OC需要外部上拉电阻。

CMOS: MOS管组成,包括集电极开路(OC)和推挽(push-pull)两种,OC需要外部上拉电阻。

TTL与CMOS电平类似,高电平为1, 低电平为0,常用高电平由5V, 3.3V, 2.5V, 1.8V。CMOS可以驱动TTL,但是TTL不能完全驱动TTL,有时需要上拉电阻或电平转换。

CMOS相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。

5V TTL VCC:5V; VOH>=2.4V,VOL<=0.4V.VIH>=2V,VIL<=0.8V;

3.3V LVTTL:VCC:3.3V.VOH>=2.4V,VOL<=0.4V,VIH>=2V,VIL<=0.8V

2.5V LVTTL:VCC:2.5V,VOH>=2V,VOL<=0.2V;VIH>1.7V,VOL<=0.7V;

5V CMOS Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。

3.3V LVCMOS:Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。

2.5V LVCMOS:Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

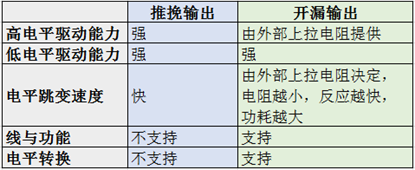

推挽与开漏区别:

I2C采用OC/OD,需要外部上拉电阻; SPI(PUSH-PULL),UART一般配置为PUSH-PULL输出,内部上拉输入.

2. RS232-C

在TxD和RxD上:逻辑1(MARK)=-3V~-15V,逻辑0(SPACE)=+3~+15V

在RTS、CTS、DSR、DTR和DCD等控制线上:信号有效(接通,ON状态,正电压)=+3V~+15V;信号无效(断开,OFF状态,负电压)=-3V~-15V。

RS-232C 与TTL转换:EIA RS-232C 是用正负电压来表示逻辑状态,与TTL以高低电平表示逻辑状态的规定不同。因此,为了能够同计算机接口或终端的TTL器件连接,必须在EIA RS-232C 与TTL电路之间进行电平和逻辑关系的变换。实现这种变换的方法可用分立元件,也可用集成电路芯片。目前较为广泛地使用集成电路转换器件,如MC1488、SN75150芯片可完成TTL电平到EIA电平的转换,而MC1489、SN75154可实现EIA电平到TTL电平的转换。MAX232芯片可完成TTL←→EIA双向电平转换。

3. RS422 与RS485

发送端间T+与T-的电压差+2 ~ +6v为逻辑1; -2 ~ -6v 为逻辑0。

接收端 R+与R-间的电压差大于 +200mv 为逻辑1,小于-200mv 为逻辑0。

定义逻辑1为D+>D-或R+>R-的状态, 定义逻辑0为D+<D-或R+<R-的状态。

接收端R+,R-之间的电压差不小于200mv.

共模电压范围,RS-485收发器共模电压范围为-7~+12V,但RS-422收发器共模电压范围为-7~+7V。

4. CAN

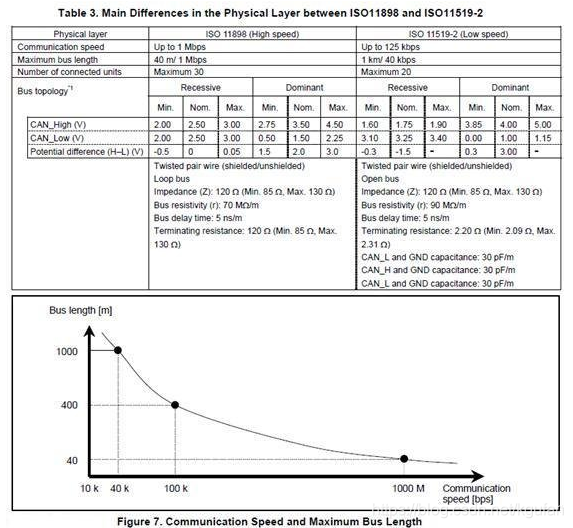

发收器将单端数字逻辑信号TXD(或者D)和RXD(或者R)转换为差分CAN总线所要求的电平。隐性(Recessive)为高电平,显性(Dominant)为低电平。

高速CAN典型值:隐性CANH=CANL=2.5V,差分0V; 显性CANH=3.5V, CANL=1.5V,差分2V;

低速CAN典型值:隐性CANH=1.75V, CANL=3.25V, 差分-1.5V, 显性CANH=4, CANL=1,差分3V。

5. USB

USB接口、引脚定义及电平在不同代有不同的要求。

对于USB 2.0 采用差分线进行数据传输,D+/D-采用(3.3V逻辑电平)。

差分信号高电平:D+>2.8V,D-<0.3V,D+ - D->0.2V

差分信号低电平:D->2.8V, D+<0.3V, D- - D+>0.2V

单端0状态(SE0):D+<0.3V, D-<0.3V;

差分信号状态并不直接代表数据状态0或1,而是指示逻辑电平有变化。USB采用不归零取反(NRZI)来传输数据,当传输线上的差分数据输入0时就取反,输入1时就保持原值无变化保持1,有变化变为零。当在USB总线上发送一个包时,传输设备就要进行位插入操作(即在数据流中每连续6个1后就插入一个0),从而强迫NRZI码发生变化。

对于USB3.X高速差分对,电压电平定义有:差分信号电压摆动典型0.5V,最小0.2V,最大0.6V。共模电压最小值为0V,最大为2.2V。

单端0状态(SE0):D+<0.3V, D-<0.3V;一般用于复位信号,SE0状态维持10ms以上则复位。

单端1状态(SE1):D+>2.8V,D->2.8V;无效状态,一般不出现。

低速下:差分信号高电平(D+>2.8V,D-<0.3V)为K状态,低电平(D->2.8V,D+<0.3V)为J状态;

高速和全速下:差分信号高电平为J状态,低电平(D->2.8V,D+<0.3V)为K状态;

主机默认在D+和D-都有15k电阻下拉,若从机D+有1.5k电阻上拉则为高速或全速设备,若D-有1.5k上拉则为低速设备。

USB 3.0 采用8b/10b编码,USB3.1采用128b/132b编码。

6. LVDS

LVDS = Low-Voltage Differential Signaling 低电压差分信号,属于平衡传输信号。

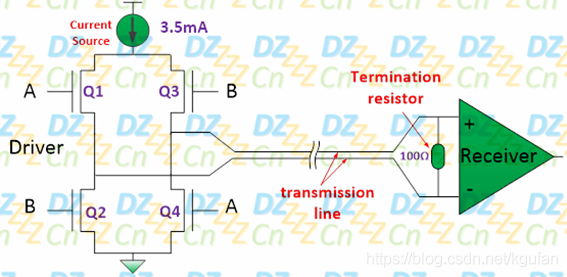

LVDS传输信号为电流驱动信号,终端匹配电阻标准规定为100Ω,由于恒流源为3.5mA,则摆动电平幅度为-350mV350mV。由于偏置电压为1.2V,则差分信号的电压范围为850mV1550mV。

当Q2、Q3导通而Q1、Q4截止时,恒流源电流经Q3流向接收器,并向下穿过100欧姆端接电阻再返回至驱动端,最后经Q2到地(GND),3.5mA的电流在100欧姆电阻上产生350mV的压降,此时同相端电压高于反相端电压,输出为高电平“H”.

而当Q2、Q3截止而Q1、Q4导通时,恒流源电流经Q1向右流向接收器,并向上穿过100欧姆端接电阻再返回至驱动端,最后经Q4到地(GND),3.5mA的电流在100欧姆电阻上也产生350mV的压降,但此时同相端电压低于反相端电压,输出为高电平“L”.

从LVDS结构原理可以看出,一对差分信号线只能够进行一个方向的数据传输,即单工通信(也称为点对点传输,point-to-point).

驱动器端的电气特征:

驱动电流: 2.5mA ~ 4.5mA, 典型值为3.5mA

差分电压摆动: 247mV<= Vswing <=454mV with two 49.9OHM(+/-1%) resistors in series.

共模电压: 1.125V<= Vos <=1.375V

短路电流: 12mA(P short to N),24mA(P or N short to GND)

接收器电气特征:

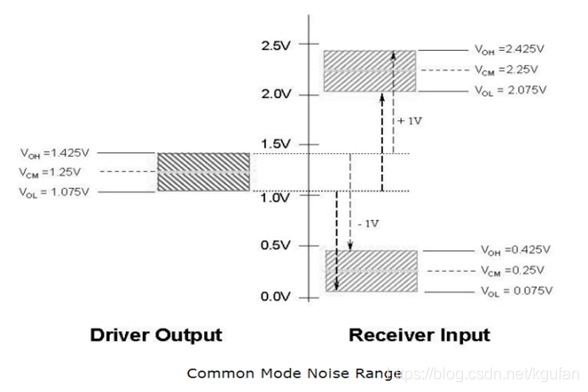

共模电压范围:0 <= Vin <= 2.4V

差分电压范围:100mV <= Vith <= 600mV

接收器和驱动器间对地电势差:+/-1V

7218

7218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?