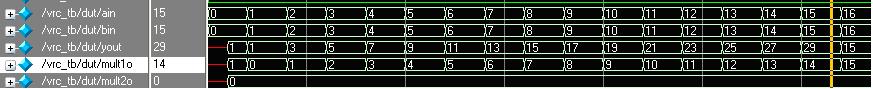

问题:使用ModelSim仿真整个VORC(Video Oriented Reconfigurable Coprocessor)时,其结果出错。从仿真波形可以看出三点怪异之处。第一:数据ain和bin相加的结果表明两者是错位相加(即:0+0,1+1而不是0+1,1+2),对照电路图可以找到原因:ain数据存在一个乘法器的延迟时间,这造成ain数据会晚一个节拍参与计算。第二:当数据ain和bin均为0时,乘法器的输出不为0,而是1,查看测试文件中所加的激励以及定义电路功能的操作码,可知:初始化时,将操作码定义为0时,造成mult1的两个输入数据均为1,因此乘法器的输出为1。第三:当数据ain和bin增加到16时,加法出错,如图一黄色竖线所在位置。分析仿真波形可以找出一个原因:MULT1(乘法器1)的结果不正确,也就是说MULT1不能正常工作。导致乘法器不能正确工作的原因推测是乘法器存在延迟。由于初始的代码使用的是纯组合逻辑,因此可能造成时序的混乱。(接下来需要进行验证)

测试文件的写法是否正确?也就是说,测试文件能不能达到测试的效果?(测试文件确实有问题,最好将输入数据的变化节拍大于时钟周期)

图一 VORC加法仿真波形(出现错误)

1、VRC_MULT(乘法器使用纯组合电路实现)

用Verilog中的乘号来编写时,使用ModelSim仿真时有延时,这会导致仿真整个VRC结构时,结果出错。

代码:

'timescale 1ns/1ns

module mult_8x4 (a, b, y);

input [7:0] a;

input [3:0] b;

output [11:0] y;

reg [11:0] y;

reg [7:0] areg;

reg [3:0] breg;

always @ (a or b)

begin

areg <= a;

breg <= b;

y <= areg * breg;

end

endmodule

测试文件

'timescale 1ns/1ns

module mult_8x4_tb ;

reg [7:0] a;

reg [3:0] b;

wire [11:0] y;

mult_8x4 dut (a, b, y);

initial

begin

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4616

4616

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?