verilog运算符

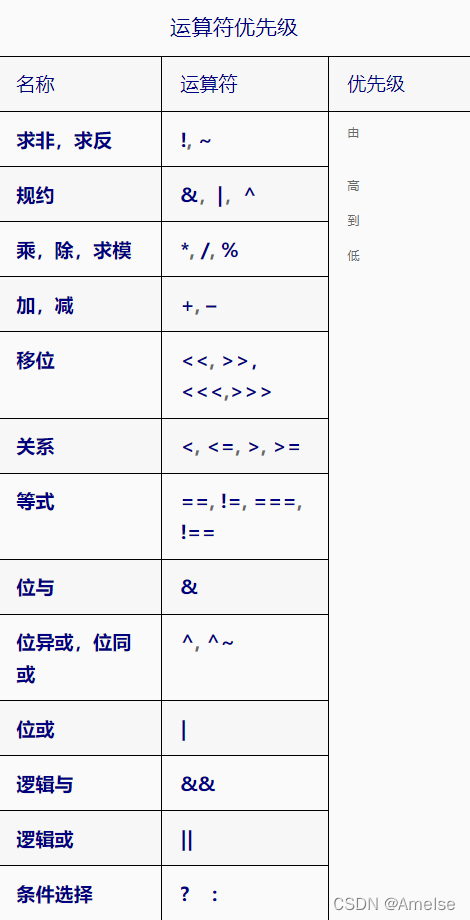

verilog HDL中运算符和优先级

一、算数运算符

verilog HDL中常用的运算符主要有五种,分别是加法(+)、减法(-)、乘法(*)、除法(/)、取模(%)。这五种运算符都属于双目运算符。

有符号数与无符号数的使用的注意在设计中是重要的

无符号数值一般储存在线网,reg型变量、整型数

有符号数值一般储存在整型变量,十进制形式整数,有符号的reg型寄存器变量,有符号线网中

算数运算符示例:

module arith_tb;

reg[3:0]a;

reg[2:0]b;

initial

begin

a = 4'b1111;

b = 4'b011;

$display("%b", a*b); //做乘法运算,结果为4'b1101

$display("%b", a/b); //做除法运算,结果为5,为4'b0101

$display("%b", a+b); //加法运算,结果为4'b0010

$display("%b", a-b); //减法运算,结果为4'b1100

$display("%b", a%b); //取模运算,结果为4'b0000

end

endmdule二、关系运算符

关系运算符也是双目运算符(比较大小)

module rela_tb

reg[3:0]a,b,c,d;

initial

begin

本文详细介绍了Verilog HDL中的各种运算符,包括算数、关系、相等、逻辑、按位、归约、位移、条件及连接复制运算符,并提供了相关示例,对于初学者理解Verilog语言的运算规则极具帮助。

本文详细介绍了Verilog HDL中的各种运算符,包括算数、关系、相等、逻辑、按位、归约、位移、条件及连接复制运算符,并提供了相关示例,对于初学者理解Verilog语言的运算规则极具帮助。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1251

1251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?