嵌入式软硬件爱好者

一张手册走天下。嵌入式单片机/Linux/Openwrt/电子电路技术交流分享。//主打一个技术层面的剑走偏锋,直击众人重视和不重视的重点//专注基础,才能走的更远

![]()

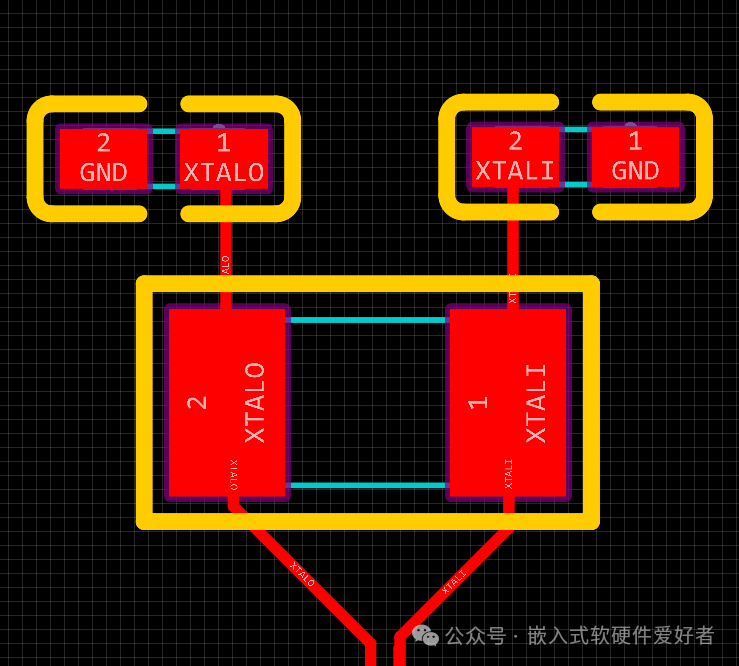

晶振电容

晶振旁边的电容在电路设计中不是用于滤波的。实际上,这些电容的主要作用是帮助晶振起振,并稳定其振荡频率。具体来说,电容与晶振一起构成了一个谐振电路,这个电路决定了晶振的振荡频率。电容的值需要经过精确计算和选择,以确保晶振能够稳定地工作在所需的频率上。

此外,晶振电路中的电容还有助于减少电路中的噪声和干扰,从而提高整个电路的稳定性和可靠性。然而,这种作用并不是通过滤波来实现的,而是通过与晶振的谐振作用共同完成的。

因此,当我们在电路中看到晶振旁边的电容时,应该理解它们的主要作用是辅助晶振起振和稳定频率,而不是进行滤波。

对于电容摆放的位置并没有太大的要求,有的人说把电容放在晶振和芯片引脚的外部,有的建议把电容放在晶振和芯片引脚之间,原因是晶振起振后的波形经过电容直达芯片。其实各有道理,另外一点来说,晶振如果放在外面,对于元器件摆放和布线更方便一些。正如前文所述,晶振和电容是共同完成起振的,放在哪里并无太大区别。

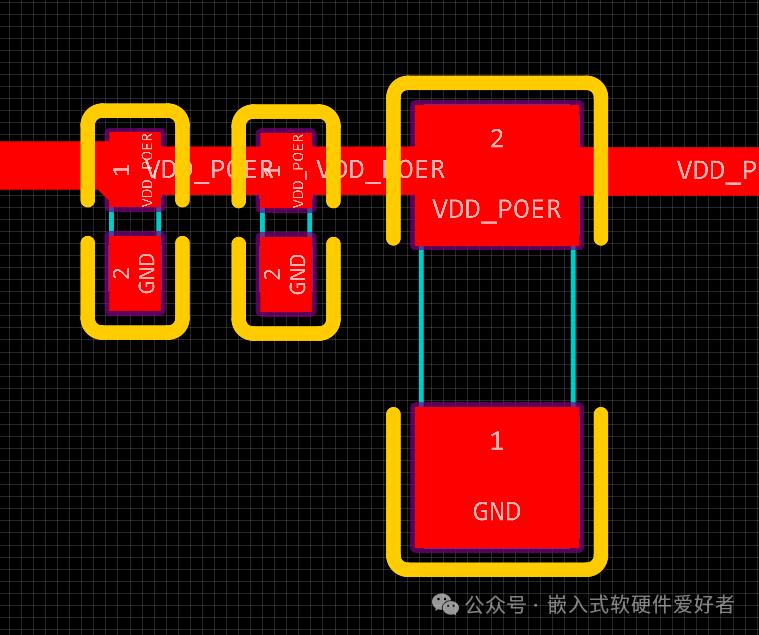

滤波电容

在滤波电路的设计中,电容的选择和使用是非常关键的。理论上,电容越大,其阻抗越小,通过的频率也越高。但实际上,当电容超过一定大小时(例如1μF),多为电解电容,这种电容具有较大的电感成分,因此在高频时其阻抗反而会增大。

在滤波过程中,通常会看到一个大电容并联一个小电容的情况。这样做的目的是利用大电容通低频、小电容通高频的特性,从而实现对不同频率信号的滤波。大电容主要负责滤除低频干扰,而小电容则主要负责滤除高频噪声。

因此,从滤波的角度来看,信号通常是先经过大电容,再经过小电容。大电容能够有效地平滑电源输出电压,减少低频干扰,而小电容则在大电容的基础上进一步滤除高频噪声,使得输出的信号更为纯净。

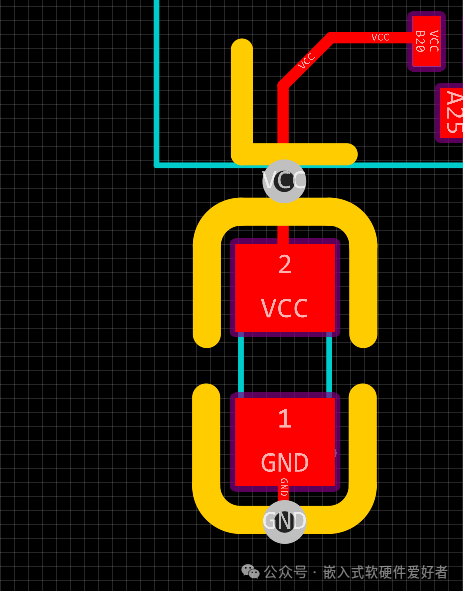

芯片引脚电容

一般来说芯片的引脚电容都是在电源供电如3.3V的旁边,对于这类电容,应尽可能保证其放置要求。

-

靠近引脚放置:为了最小化电源噪声和电压波动,建议将电容尽可能靠近芯片的3.3V引脚放置。这有助于减少电源线的长度,降低电阻和电感,从而提高电源的稳定性。

-

避免长距离走线:尽量避免电容与引脚之间有过长的走线,因为这可能增加电阻和电感,导致电源噪声增加。

-

考虑布线密度:在设计PCB时,还需要考虑布线密度和走线方向。有时,由于其他元件或走线的布局限制,电容可能无法直接放置在引脚旁边。在这种情况下,应尽量在可行的范围内优化布局,以减小电容与引脚之间的距离。

-

考虑散热和机械应力:如果电容或芯片受到散热或机械应力的影响,可能需要考虑在电容和芯片之间加入一些间隔或缓冲措施。

另外,在电容放置后都是一端连接芯片引脚及VCC供电,另一端连GND。一般情况下都需要放置过孔来连接网络,如下图两种过孔放置位置

这两种放置方式最好的就是下边这种,VCC电源经过电容滤波再到芯片引脚。而第一种从细节上来说是VCC流向芯片和电容两个方向。

以上就是电容相关的一些细节,感谢支持。

251

251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?