由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构。LUT本质上就是一个RAM.它把数据事先写入RAM后,每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

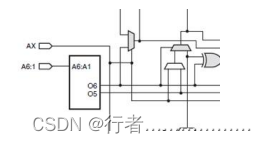

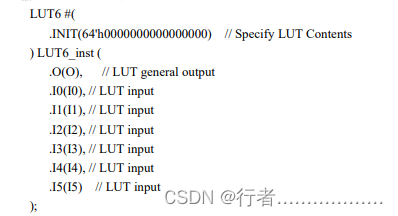

FPGA中的函数发生器通过六输入查找表(LUT)实现。slice的4个查找表(A, B, C和D)中的每一个都有六个独立输入(A 输入 A1 至 A6)和两个独立输出(O5 和 06)。

查找表可以实现的函数功能:

任意定义的六输入布尔函数

两个任意定义的五输入布尔函数,只要这两个函数共享公共输入·

两个任意定义的布尔函数(3个和2个或更少输入)

六输入功能使用:

•Al~A6 输入

•o5、o6 输出

两个五输入或更少的输入使用:·

Al-A5输入

·A6 驱动高.

05和06输出

多路复选器 F7AMUX, F7BMUX 和 F8MUX

·F7AMUX:用于从LUTA和B生成七个输入

F7BMUX:用于从 LUTC和D生成七个输入.

F8MUX:用于组合所有LUT以生成八个输入

六输入查找表原语如下:

2092

2092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?