简介

卷积是图像处理中很常见的一种操作,3x3是最常见的窗口大小。

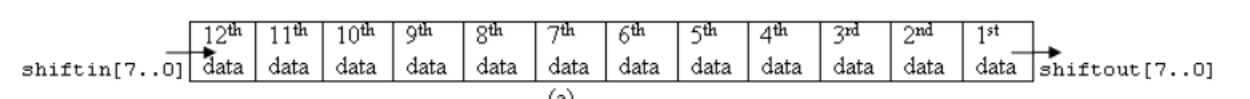

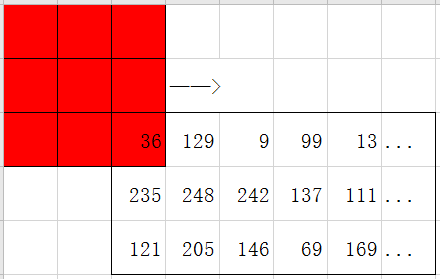

如果像素是一个个来的,要想实现3x3卷积,就得同时获取一个像素和它周围的8个像素,将输入像素缓存2行,这样就能同时获取3行的像素输入,此时再将这3个并行输入的像素移位进3x3窗口,就获得了3x3卷积模板,如图:

这里要注意,输入像素此时作为第三行数据输入3x3窗口,最下面的行缓存输出的才是第一行像素,上图窗口的右下角是3x3卷积模板的左上角,窗口的左上角是3x3卷积模板的右下角。

实现两行缓存并获取3x3卷积窗口,用shift-ram是最简单的实现方法。

shift-ram简介

shift-ram是一个ip核,quartus13.0中叫做Shift register(RAM based)

普通shift-ram如图:

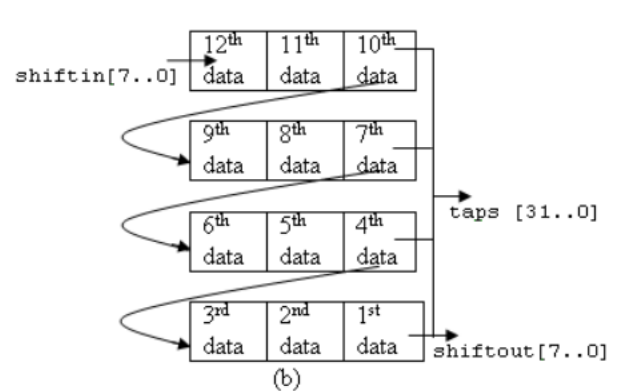

带taps的shift-ram:

其实带taps的shift-ram就是多个普通shift-ram组合,使用带taps的shift-ram可以轻松实现行缓存,设定taps数量为2,taps间隔为一行的像素数(此处为640),即可缓存两行。之后将这两个taps和输入像素移位进3x3窗口即可获得3x3卷积模板。

verilog源码

为了简单起见,输入和输出都是valid+data的形式。

module filter_3x3(

input clk,

input rst_n,

input iValid,

input [7:0] iData,

output oValid,

output reg [7:0] oData_11, oData_12, oData_13,

output reg [7:0] oData_21, oData_22, oData_23,

output reg [7:0] oData_31, oData_32, oData_33

);

reg [7:0] row3_data;

wire [7:0] row2_data;

wire [7:0] row1_data;

reg [1:0] Valid_shift;

// shift_ram实现2行缓存

line_shift_ram inst_line_shift_ram(

.clock (clk),

.clken (iValid),

.shiftin (row3_data),

.taps0x (row2_data),

.taps1x (row1_data),

.shiftout ()

);

// 将输入数据寄存作为窗口第三行起始数据,同时也作为行缓存的输入

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

row3_data <= 0;

else if(iValid)

row3_data <= iData;

end

// 获取3x3卷积模板

always @(posedge clk, negedge rst_n) begin

if(!rst_n) begin

{oData_11, oData_12, oData_13} <= 3'b000;

{oData_21, oData_22, oData_23} <= 3'b000;

{oData_31, oData_32, oData_33} <= 3'b000;

end else if(iValid) begin

{oData_11, oData_12, oData_13} <= {oData_12, oData_13, row1_data};

{oData_21, oData_22, oData_23} <= {oData_22, oData_23, row2_data};

{oData_31, oData_32, oData_33} <= {oData_32, oData_33, row3_data};

end

end

// iValid打两拍输出

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

Valid_shift <= 2'b00;

else

Valid_shift <= {Valid_shift[0], iValid};

end

assign oValid = Valid_shift[1];

endmodule

testbench

只仿真三行,每行640个像素。

`timescale 1ps/1ps

module test_tb;

reg clk = 1'b1;

always #10 clk = ~clk;

reg rst_n = 1'b0;

reg iValid = 1'b0;

reg [7:0] iData = 0;

wire oValid;

wire [7:0] oData_11;

wire [7:0] oData_12;

wire [7:0] oData_13;

wire [7:0] oData_21;

wire [7:0] oData_22;

wire [7:0] oData_23;

wire [7:0] oData_31;

wire [7:0] oData_32;

wire [7:0] oData_33;

initial begin

#20 rst_n <= 1'b1;

#20 iValid <= 1'b1;

// 第一行数据

repeat(640) begin

iData <= $random;

#20;

end

iValid <= 1'b0;

#100 iValid <= 1'b1;

// 第二行数据

repeat(640) begin

iData <= $random;

#20;

end

iValid <= 1'b0;

#100 iValid <= 1'b1;

// 第三行数据

repeat(640) begin

iData <= $random;

#20;

end

#500 $stop;

end

filter_3x3 inst_filter_3x3(

.clk (clk),

.rst_n (rst_n),

.iValid (iValid),

.iData (iData),

.oValid (oValid),

.oData_11 (oData_11),

.oData_12 (oData_12),

.oData_13 (oData_13),

.oData_21 (oData_21),

.oData_22 (oData_22),

.oData_23 (oData_23),

.oData_31 (oData_31),

.oData_32 (oData_32),

.oData_33 (oData_33)

);

endmodule

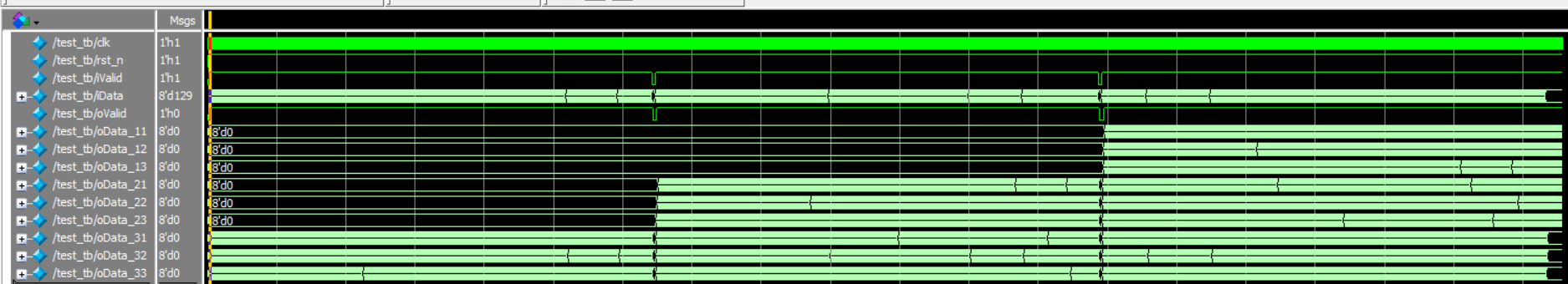

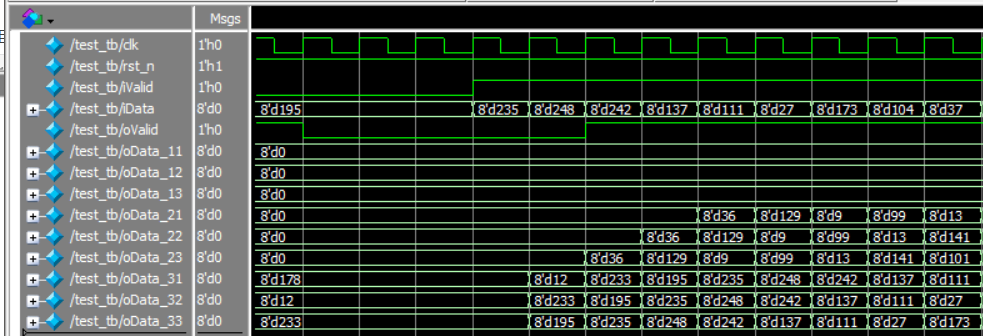

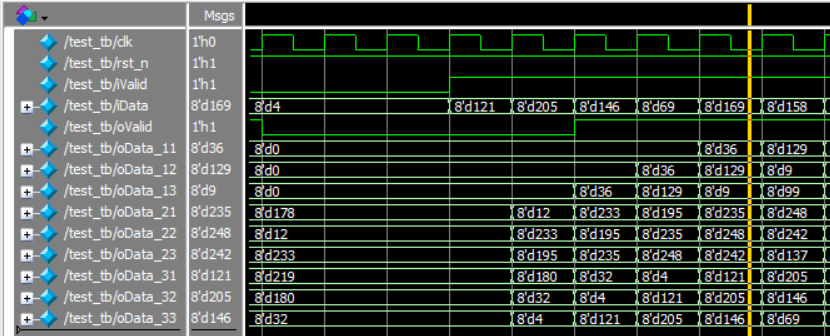

波形分析

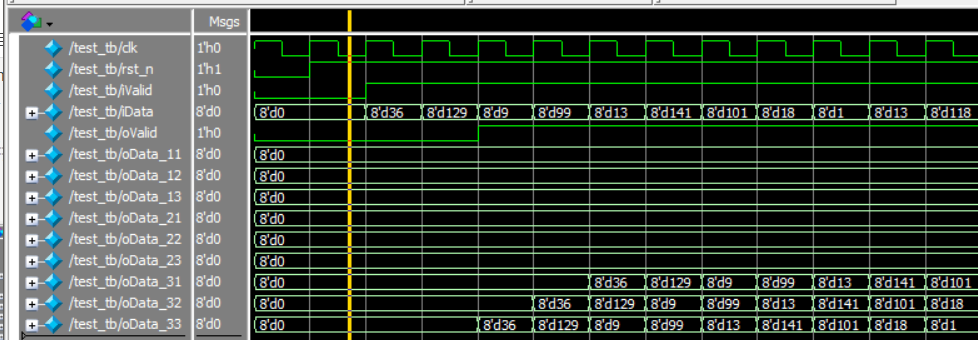

可以看出,3x3卷积模板的第三行最先出现,然后是第二行,最后才是第一行。

输入像素第一行的最前面几个像素如图,前三个为36,129,9。

输入像素第二行最前面几个像素如图,前三个像素为235,248,242:

此时再来看输入像素第三行,前三个像素为121,205,146:

上图黄色竖线处即可看到oData11 ~ oData33为36,129,9,235,248,242,121,205,146,正是每一行的前三个像素。

这个模板的移动类似于下图,最开始时模板只有右下角一个像素,然后向右移动,遍历完一行就遍历下一行。

虽然跟正常的卷积比,这个模板向左上角错位了,但视觉上影响不大,用它来做图像处理足够了。

1659

1659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?